匹 配 试 验 项 目

晶体振荡器俗称晶振,是晶振电路的核心元器件。晶振电路用于产生时间频率基准,为微控制器系统(Microcontroller Unit,MCU)提供精准的时基。在实际应用中,如果晶振电路负载参数匹配不当,一方面,可能会造成晶振电路工作频率出现偏差,进而造成计时不准,通信不能同步;另一方面,在睡眠唤醒时,电路扰动较小,可能会导致晶振电路起振困难。无论哪种情况,均会影响微控制器系统的性能甚至造成其无法工作。为此,华昕电子专门提供合理的匹配晶振电路负载参数的技术支持。

频率偏差

负载电容的计算与测试匹配

1.理论计算方法

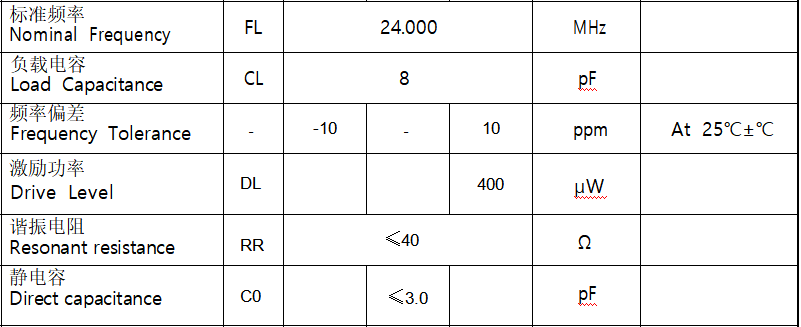

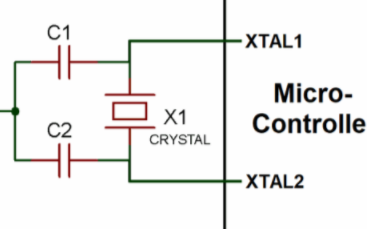

负载电容CL的大小取决于外部电容CL1、CL2和等效杂散电容CS,计算公式如下:

CL=(C1*C2)/(C1+C2)+Cs

华昕的datasheet中会给出晶振的负载电容CL的标称值。等效杂散电容CS与芯片引脚、焊盘、封装引脚和印刷电路板走线等均有关系,无法得到具体理论数值,按照经验,通常估算为3~5 pF。一般两个外部电容CL1和CL2选定为相同电容值。文中选定的晶振负载电容CL为8 pF,代入公式(1)可计算得到CL1=CL2=6~10 pF。

经过理论计算得到的外部电容CL1和CL2的范围值可以作为后续测试匹配的参考,然后通过实际测试匹配实验确定最优外部电容容值。

2.测试匹配方法

晶振的具体测试匹配方法是根据理论计算所得电容值范围附近选取典型电容值的电容,然后分别测试并记录不同外部电容值下的振荡频率、振荡频偏等参数,通过对比各参数选取最优外部电容值。

最优外部电容值评价准则:实测振荡频率越接近标称振荡频率,振荡频偏越小,则电容值越优,实际测试匹配过程需要权衡选择电容值。

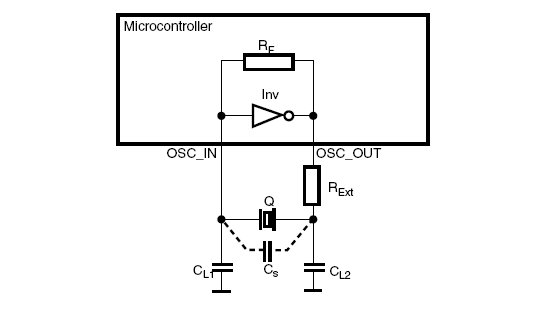

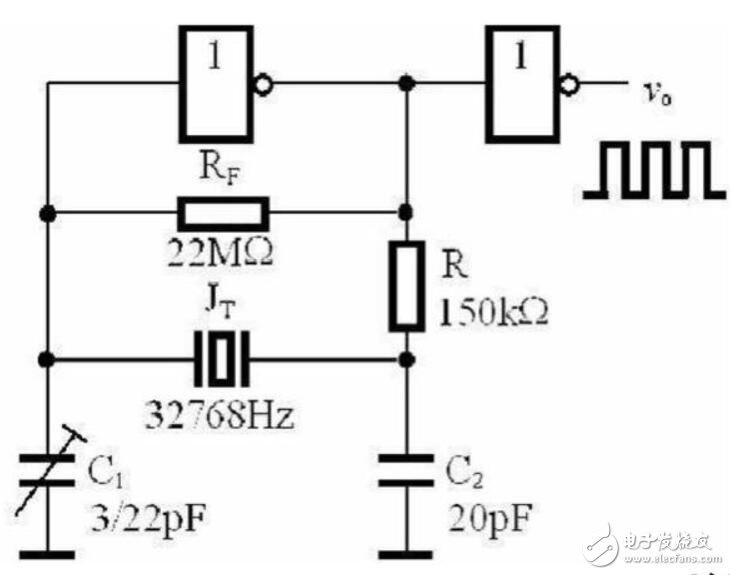

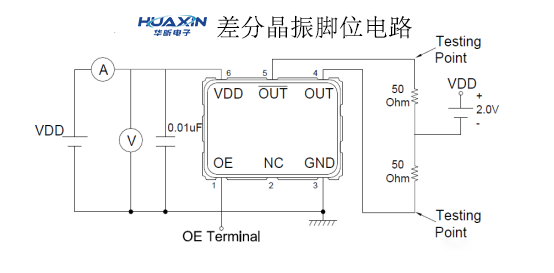

3.测试匹配过程晶振电路测试匹配的环境设置如图所示。

此处测试的目的仅仅是为了进行不同负载参数下晶振特性的比对,验证理论推算的正确性,因此我们选用示波器作为基本测量设备,如果需要获取精度更高的频率数据,需要选用专业的显频仪等设备进行测量。

本次示例选取6.8、8、10和100 pF 4种容值电容作为外部CL1和CL2的备选电容,限流电阻固定为1.5 kΩ,选择100 pF电容是为了更明显地验证当外部电容值和理论计算值差别较大时的晶振输出波形的表现状况。通过更换不同容值的外部电容,并利用示波器采集晶振电路输出波形(CL1和CL2需同时更换,保证CL1和CL2的容值始终一致)。对比输出波形的稳定性、频率偏差和幅值大小来判断最佳容值。

4.测试结果及分析

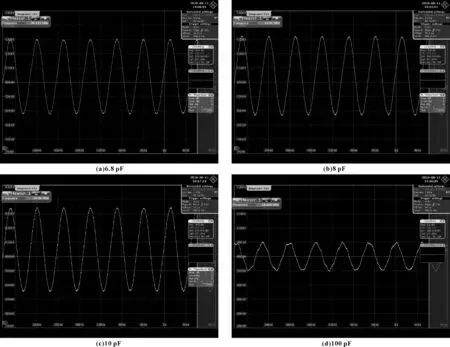

图中给出了当外部电容为6.8、8、10及100 pF时,晶振电路的输出波形。从图中可以看出,在前3种外部电容配置下,晶振电路的输出波形均较为平滑,未出现突变区域,波形重复度较高。当外部电容提升至100 pF时,可以看出,晶振电路输出波形呈现出明显不平滑现象,波形不规律区域较多。

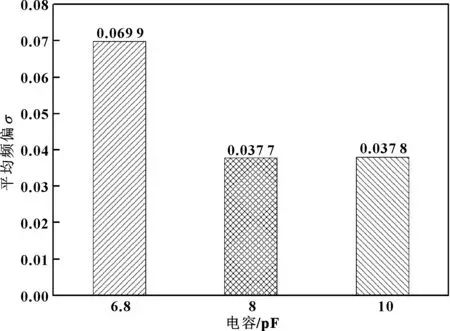

当外部电容为6.8、8和10 pF时,晶振电路输出波形的平均频偏对比。可以看出,当外部电容为8和10 pF时,平均频偏较低,且二者之间差别不大,当外部电容为6.8 pF时,平均频偏明显升高。说明8和10 pF是较为合适的容值。

-

测试

+关注

关注

8文章

5265浏览量

126593 -

控制器

+关注

关注

112文章

16316浏览量

177788 -

晶振电路

+关注

关注

7文章

92浏览量

25293

发布评论请先 登录

相关推荐

国产晶振之光:华昕电子,品质与技术的完美结合

华昕晶振电路参数匹配

华昕晶振电路参数匹配

评论