在激光雷达中,使用FPGA实现TDC时需要手动约束进位链的位置。这里简单记录下。

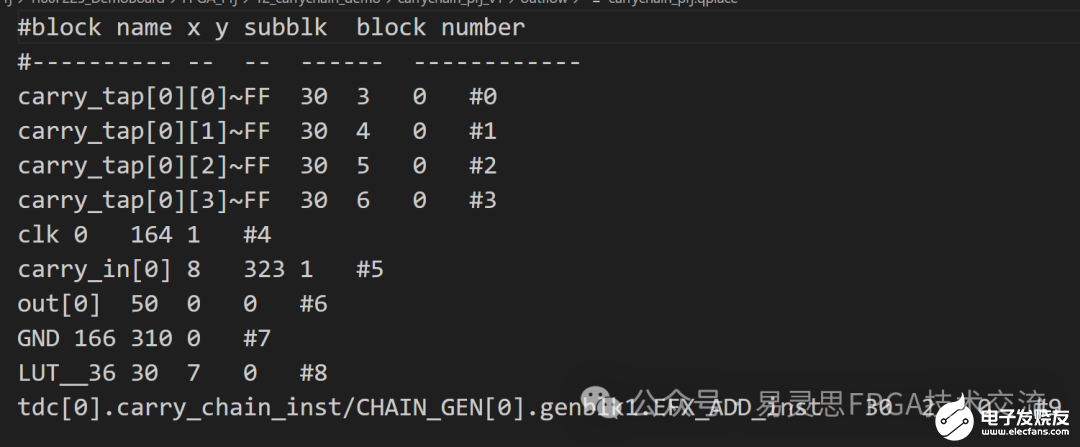

在outflow下会生成一个.qplace文件。用于指示布线的各个原语资源的分布位置 。

它的内容主是

是原语的单元名

表示水平位置,对应floorplan.

表示垂直位置 ,对应floorplan.

表示子块的位置 。目前只DSP24和DSP12可以有子块。在一个block可以指定多个字块。

是给block的一个编号,从0开始往下排。

锁定过程如下:

stp1:并把outflow下面的.qplace文件得到到工程目录下(可以修改名字也可以不修改,假如我们修改为carrychain.qplace)。把该qplace文件中想要锁定的block保留,其余可以删除。

stp2:在工程目录下建一个efx_pnr_settings.ini文件 。

stp3:在efx_pnr_settings.ini文件中输入

fix_pins=carrychain_prj.qplace

stp4:重新编译。

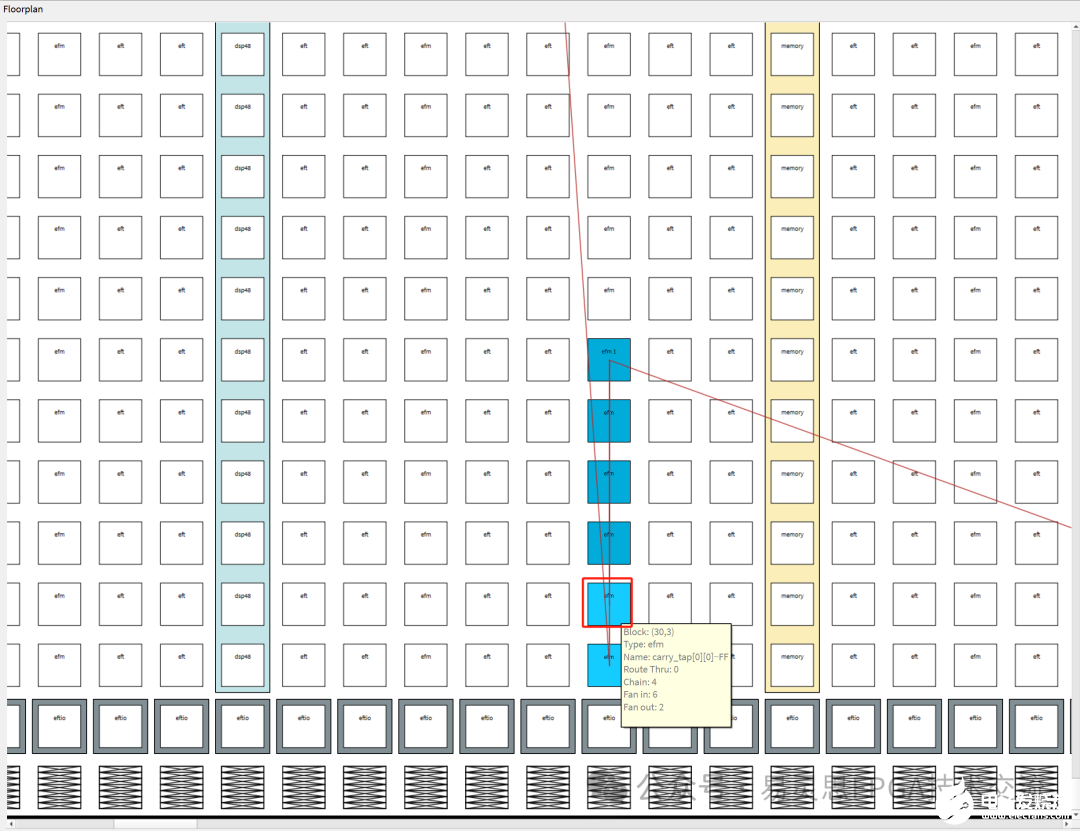

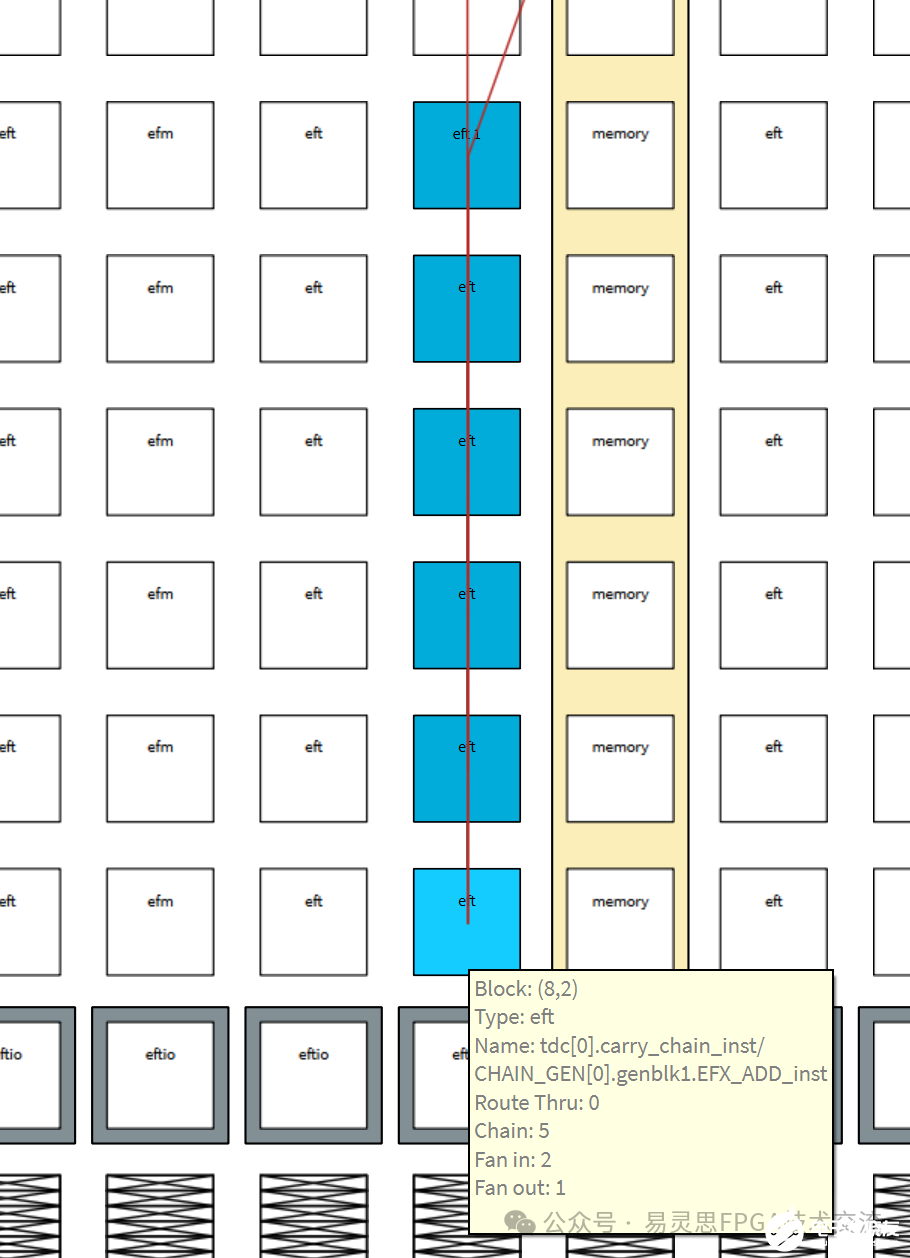

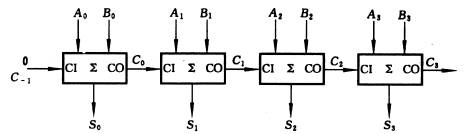

以加法进位链为例 ,上面我们生成了一个4级的加法进位链。具体约束在哪个位置可以在floorplan中确认位置 。

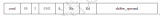

比如这里我们把它的位置约束到第8列。看下面的语句,第二行是进位链的输入位置用于进入进位链,第3,4,5,6依次约束进位链的carry_tap[0][x]~FF即可。

之前也有一个疑问是是否应该约束加法器,但是资源列表中并没有相应的资源,而且经过分析也认为只需要约束寄存器即可。

#block name x y subblk block number#---------- -- -- ------ ------------carry_tap[0][0]~FF 8 3 0 #0carry_tap[0][1]~FF 8 4 0 #1carry_tap[0][2]~FF 8 5 0 #2carry_tap[0][3]~FF 8 6 0 #3tdc[0].carry_chain_inst/CHAIN_GEN[0].genblk1.EFX_ADD_inst 8 2 0 #2605

约束的效果如下:

-

FPGA

+关注

关注

1630文章

21796浏览量

605529 -

TDC

+关注

关注

0文章

38浏览量

13804 -

进位链

+关注

关注

0文章

3浏览量

5144

发布评论请先 登录

相关推荐

4位带进位的加法+减法计算器

超前进位集成4(四)位加法器74LS283

加法器原理(16位先行进位)

基于选择进位32位加法器的硬件电路实现

加法器是什么?加法器的原理,类型,设计详解

怎么设计一个32位超前进位加法器?

ADC带进位的加法指令

加法器功能

DM74LS83A四位快速进位二进制加法器的数据手册免费下载

加法进位链的手动约束

加法进位链的手动约束

评论