必须要保护器件来应对ESD吗?

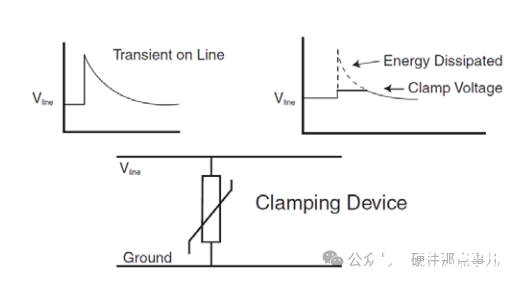

“是否真的需要电路保护器件来保护电路免受静电放电(ESD)的影响?”这是一个许多硬件工程师都会遇到的问题。目前电路中通常有I/O接口,这些接口由集成IC驱动。这些IC虽然功能强大,但对瞬态过应力(例如静电放电)的耐受能力却显著下降。因此,保护这些连接到产品I/O接口的IC免受瞬态过应力就很重要。所以针对瞬态过压保护的设计必不可少。

Part 02

芯片手册中的ESD防护能力2kV够吗?

从专业角度来看,这个ESD额定值并不足够,为了确保芯片在制造过程中不会被ESD损坏,芯片厂家通常会在芯片的I/O单元设计ESD保护结构。这种“芯片内”的保护主要应对的是在生产/制造过程中人或机器产生的静电危害。

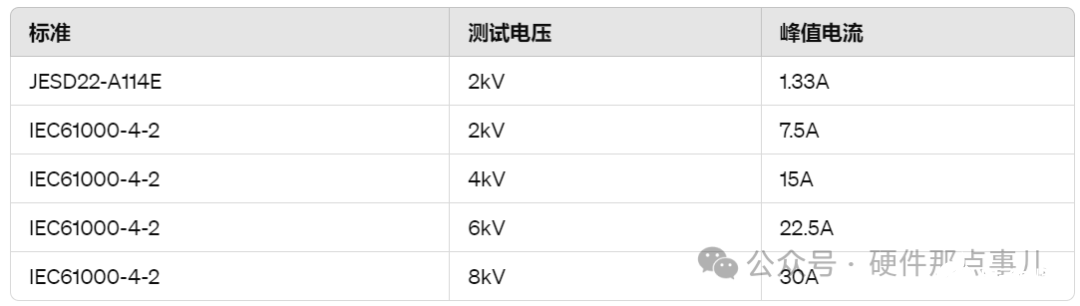

目前有几种不同的ESD标准,每一种标准都描述了适用于特定ESD环境的防护级别。对于器件级的ESD,一般采用的是JESD22-A114E标准。这是JEDEC中定义的人体模型(HBM)标准,芯片厂家在开发其芯片时是依据这一标准来设计的。这个标准目的就是确保在制造过程中让IC得到所需的最低限度的芯片内的保护。

相比之下,在系统级的电路设计就不再考虑JESD22-A114E,而是考虑完全不同的标准,即IEC61000-4-2。IEC61000-4-2描述并模拟了在系统环境中遇到的ESD威胁,为了模拟更接近“真实世界”的系统的ESD威胁,IEC标准是一个更严格的ESD测试。IEC规定了针对不同威胁级别的4种接触测试电压:±2kV、±4kV、±6kV、±8kV,峰值放电电流可高达30A。 JEDEC和IEC标准要求的峰值脉冲电流水平是不同的,如下表所示:

总结来说,尽管IC在芯片级提供了2kV ESD保护,但在实际应用中,这可远远不够,为了确保系统的稳定性和可靠性,需要采用符合IEC61000-4-2标准的系统级ESD保护措施。

Part 03

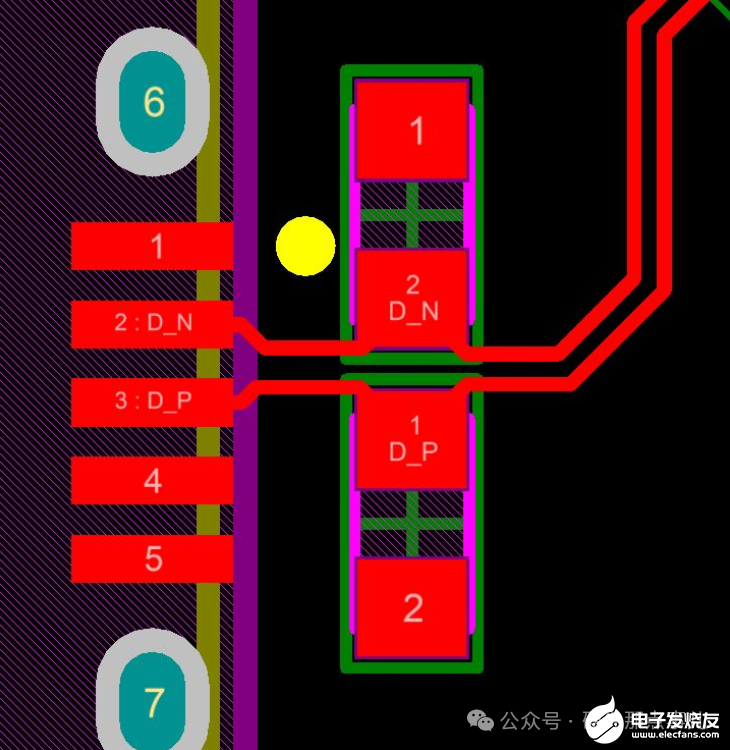

在设计电路板布局时,如何优化TVS器件的放置是一个关键问题,尤其是对于瞬态过压的保护效果来说。当处理ESD(静电放电)时,抑制初始瞬态尖峰的电压大小也会依赖于PCB布局的好坏。即使是非常好的保护电路,如果遇上比较差的PCB布局,那效果也是1-1=0。

1.尽可能将TVS元件放置在接口连接器附近:这样做有助于在ESD事件发生时,在PCB的入口处抑制ESD,从而减少由ESD引起的辐射发射可能产生的其他影响。

2.通过缩短从TVS器件到被保护I/O线的走线长度来最小化寄生电感,举个例子,如果ESD的上升时间为1ns的话,那么30A脉冲在1nH的串联等效电感走线上可以使TVS器件的钳位电压提高30V,从而使TVS的钳位电压大大增加,无法实现保护IC的目的。 3.尽可能将TVS器件的接地连接直接连接到地平面:如果需要使用过孔,那就尽可能多使用过孔连接到地平面。这样可以降低寄生电感,提高保护效果。

3.在高速数字信号上,TVS器件的等效电容成为一个重要考虑因素,因为电容存在充放电,会增大信号的上升时间,所以为了保持信号完整性,在不牺牲钳位性能的情况下,尽可能等效电容最小的器件。

-

ESD

+关注

关注

50文章

2422浏览量

180376 -

电路设计

+关注

关注

6745文章

2785浏览量

220142 -

TVS

+关注

关注

8文章

991浏览量

63778 -

过压保护

+关注

关注

3文章

353浏览量

33915 -

保护器件

+关注

关注

1文章

352浏览量

14311

发布评论请先 登录

高压起弧试验机保护电路设计:过流、过压与di/dt抑制的工程实践

风华车规片式压敏电阻APV系列能为汽车电子提供卓越的瞬态过压保护

可调整阈值的过压保护控制集成电路

探索MAX16010 - MAX16014:超小型过压保护与检测电路的卓越之选

为什么过压、过流和短路保护在电源中非常重要?

电路设计中关于瞬态过压保护最常出现的三个疑问解答

电路设计中关于瞬态过压保护最常出现的三个疑问解答

评论