1 传统冯诺依曼瓶颈

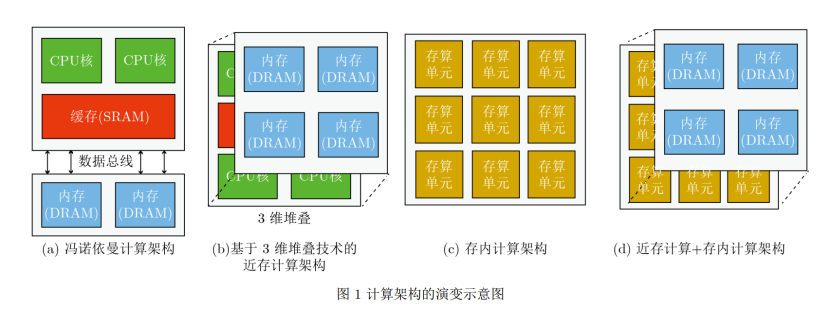

随着人工智能、物联网、智能传感等应用的快速兴起,数据以爆发式的速度增长。海量数据的高效存储、迁移与处理成为当前信息领域的重大挑战。受限于经典的冯诺依曼计算架构存储与处理分离的特性,在面向大数据分析等应用场景中,数据总线的带宽严重制约了处理器的性能与能量效率,并且数据的频繁迁移带来严重的传输功耗问题。

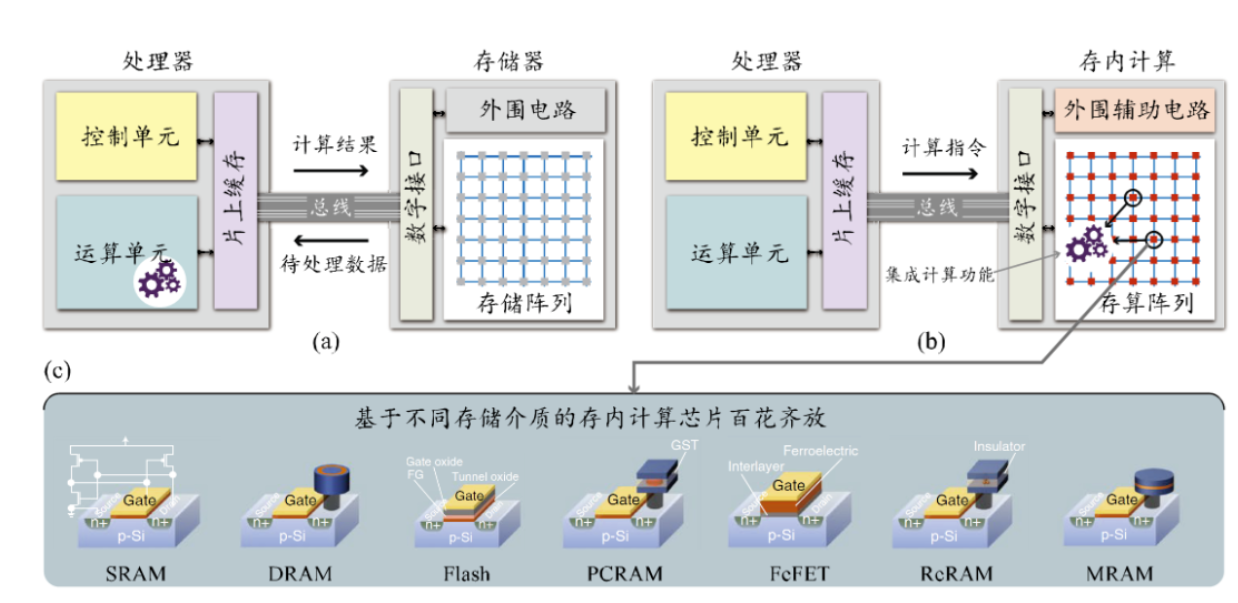

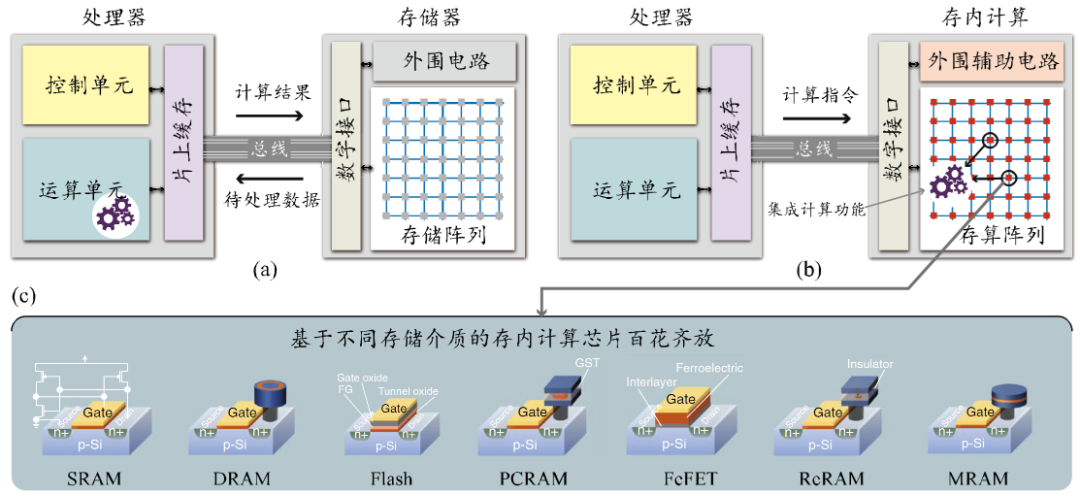

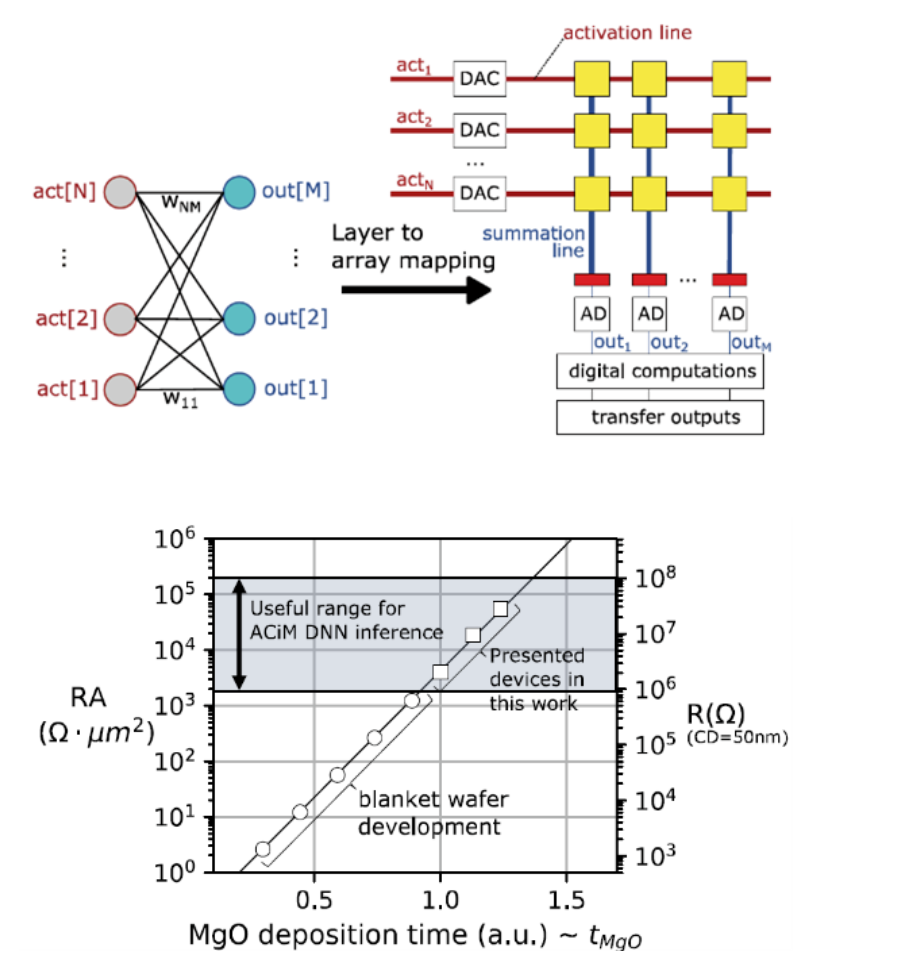

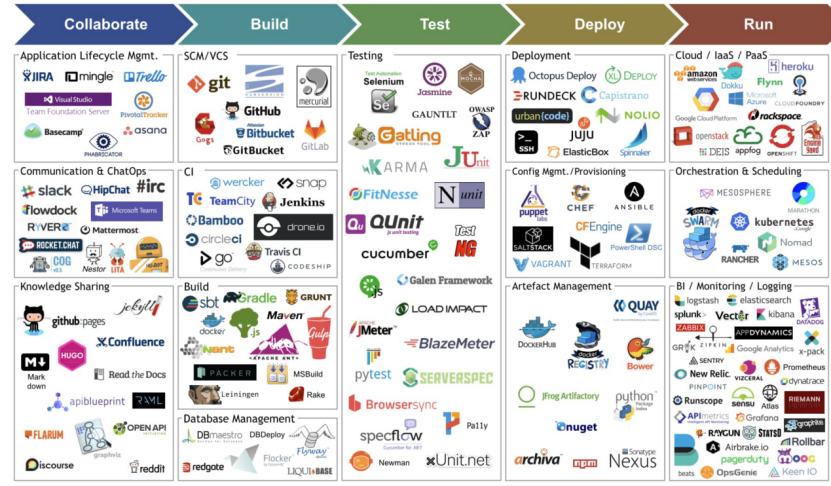

存内计算架构在此基础上应运而生。如图-1b所示,通过赋予存储器计算功能,以数据为中心,避免不必要的数据频繁搬运,降低系统的功耗和延时。

图1 (a)经典冯诺依曼架构图;(b)主处理器+存内计算的架构示意图;(c)基于不同存储介质的存内计算技术百花齐放。

近年来,基于不同存储介质的存内计算技术不断涌现,并受到学术界和工业界的广泛关注。从2017年至今,存内计算主题开始频繁出现在电路和芯片领域的顶级会议/期刊上(ISSCC、VLSI、IEDM、JSSC、TCAS-I),且占比快速增加。

2 产业界相继发布存内计算芯片

工业界方面,台积电、三星、英特尔、IBM、Global Foundries、IMEC等国际半导体巨头相继于2021-2023年期间发布了各自的存内计算原型芯片或初期商用芯片,但仍没有十分完善的产品出现。存内计算技术采用非冯诺依曼架构,在大数据时代,为人工智能、物联网、智能传感器等领域提供高效的硬件解决方案,有重要的应用价值。

三星在顶级学术期刊Nature上发表了全球首个基于MRAM(磁性随机存储器)的存内计算研究,紧接着台积电在近日的ISSCC上合作发表了六篇关于存内计算存储器IP的论文,大力推进基于ReRAM的存内计算方案。

2.1 三星发布基于MRAM的存内计算

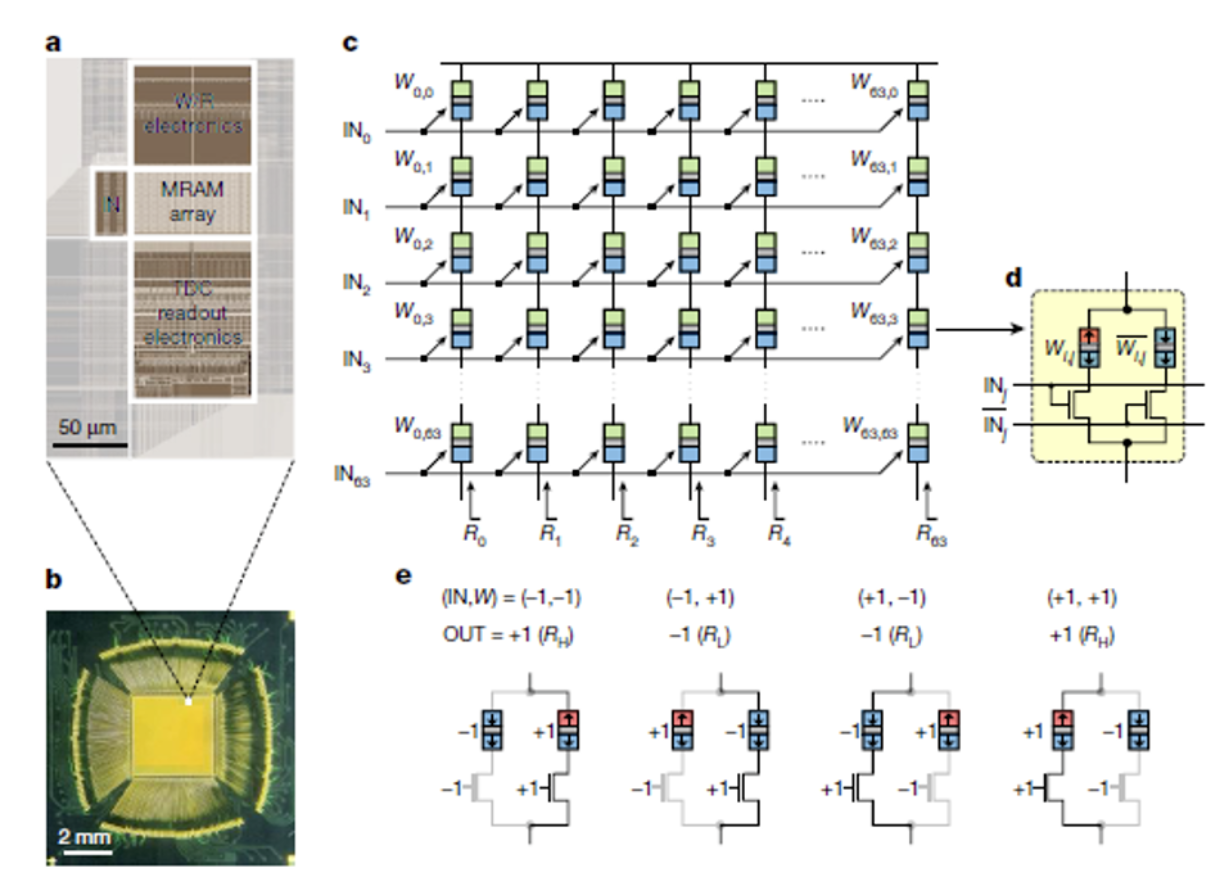

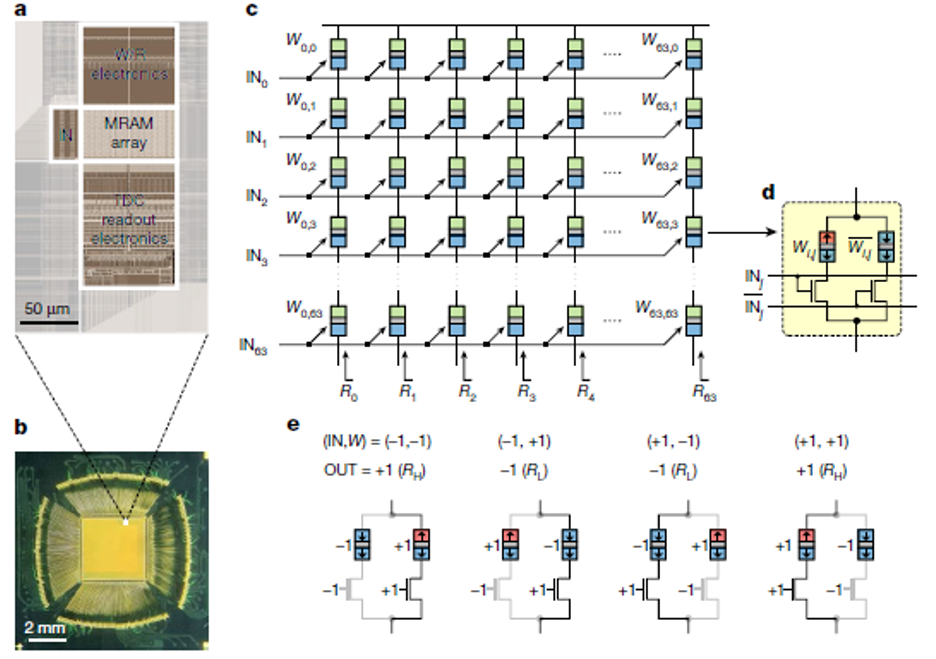

2022年,三星半导体宣布,通过结构创新,实现了基于MRAM(磁阻随机存取存储器)的内存内计算(In-Memory Computing),进一步拓展了三星的下一代低功耗人工智能芯片技术的前沿领域。

MRAM磁阻内存很难用于内存内计算,因为它在标准的内存内计算架构中无法发挥低功耗优势。

三星研究团队设计了一种名为“电阻总和”(resistance sum)的新型内存内计算架构,取代标准的“电流总和”(current-sum)架构,成功开发了一种能演示内存内计算架构的MRAM阵列芯片,命名为“用于内存内计算的磁阻内存交叉阵列”(crossbar array of magnetoresistive memory devices for in-memory computing)。

成功解决了单个MRAM器件的小电阻问题,从而降低功耗,实现了基于MRAM的内存内计算。按照三星的说法,在执行AI计算时,MRAM内存内计算可以做到98%的笔迹识别成功率、93%的人脸识别准确率。

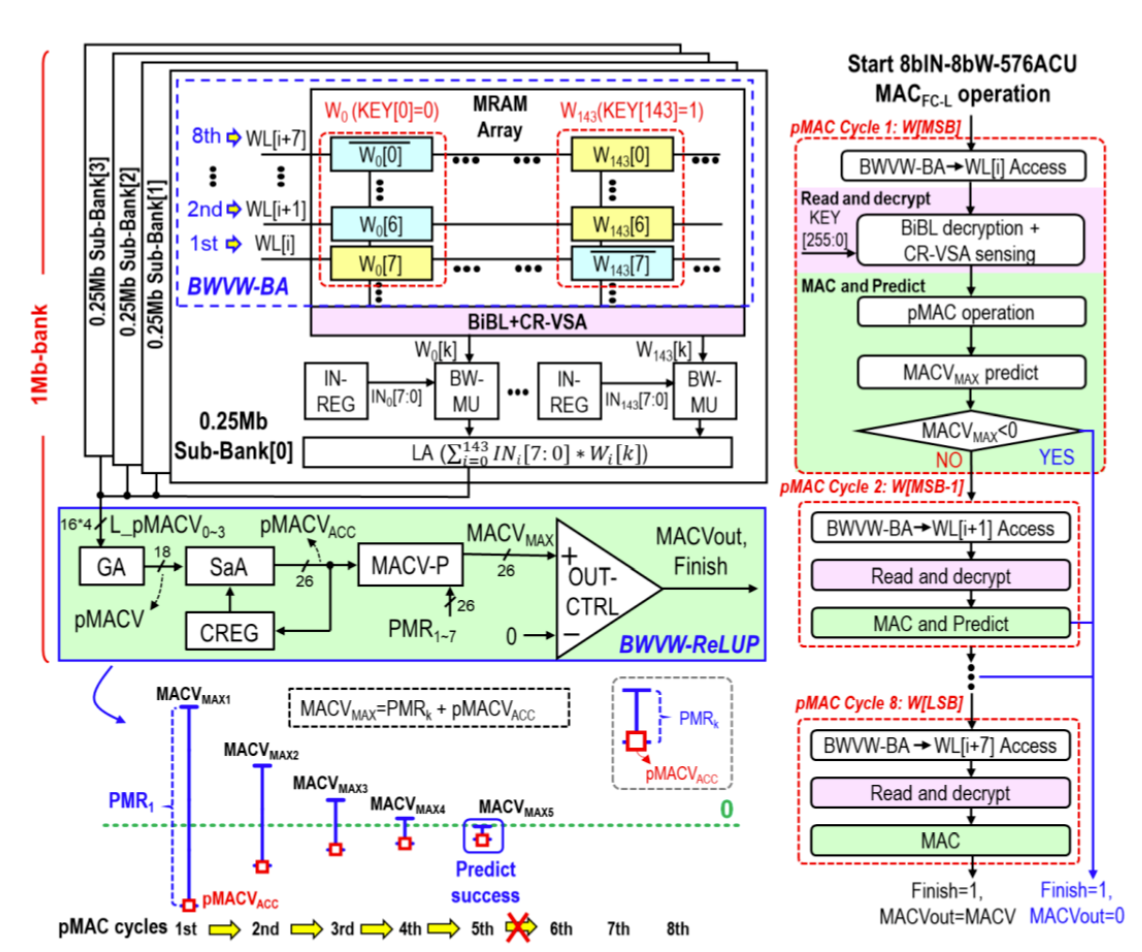

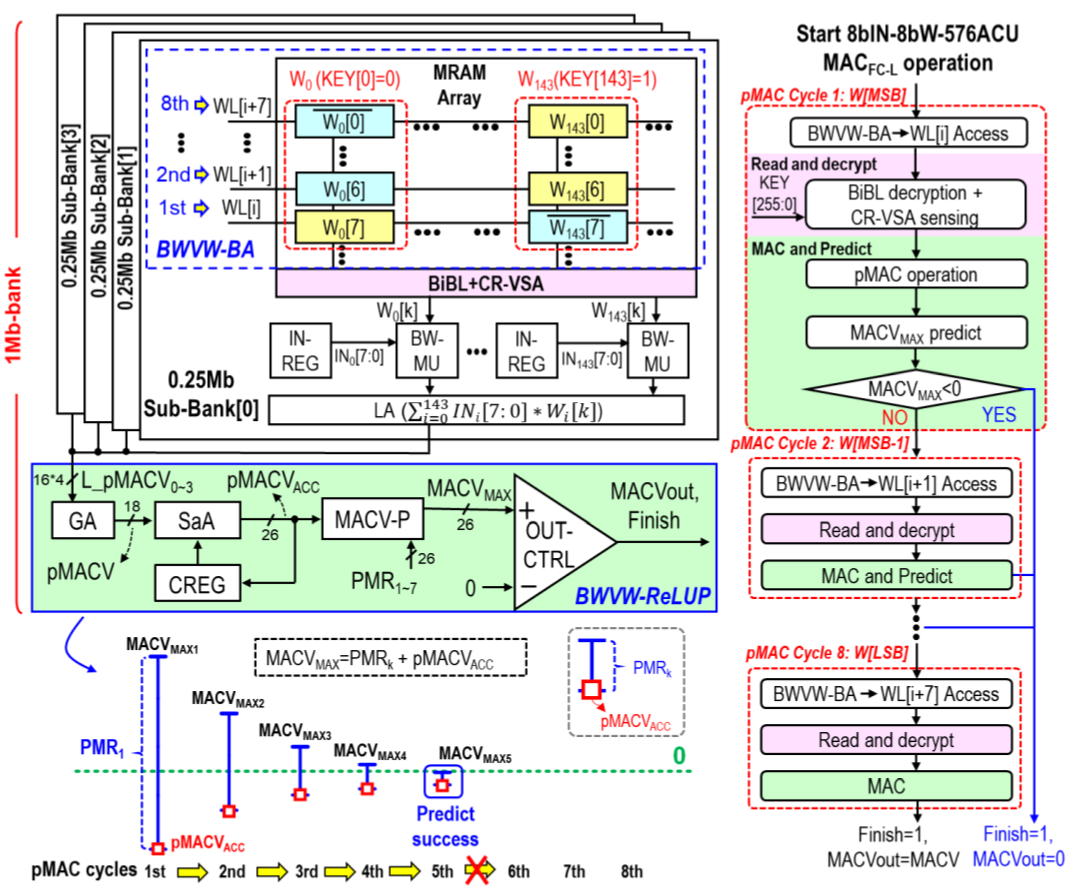

2.2 台积电发布独立式STT-MRAM

2024年2月20日,中国台湾“国研院半导体研究中心”宣布,与台积电合作开发的“选择器元件与自旋转移力矩式磁性存储整合”(Selector and STT-MRAM Integration)技术,于2023年12月全球顶尖电子元件会议IEDM(International Electron Devices Meeting)中发表,并获选为Highlight Paper,成为全世界极少数成功开发出高密度、高容量的独立式STT-MRAM制作技术的团队。

由于STT-MRAM具备高速度、高可靠度、小体积、省电等优点,十分适合应用于云端计算与物联网上进行大量的数据储存。

据悉,台积电三十几年来一直致力科技创新及研发,重视技术自主,近年研发经费投入平均是营收的8%,2020年研发经费首度超过1000亿元新台币,未来随着业务不断成长,研发经费会越来越多。

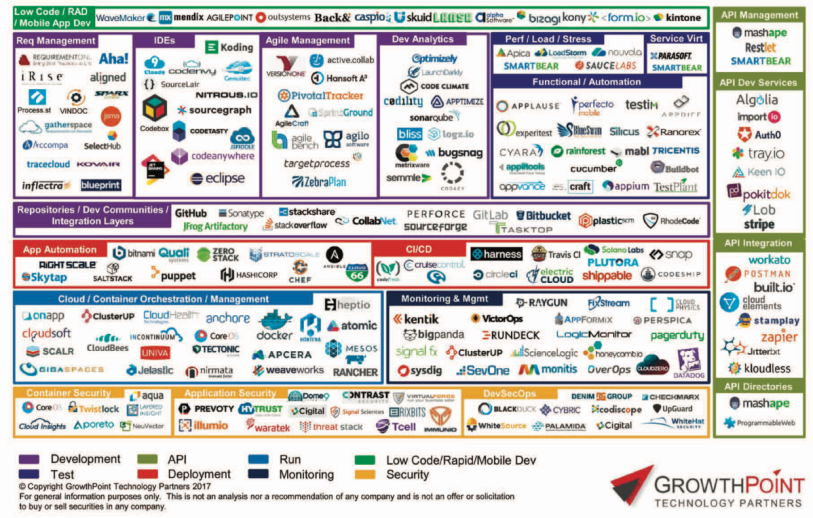

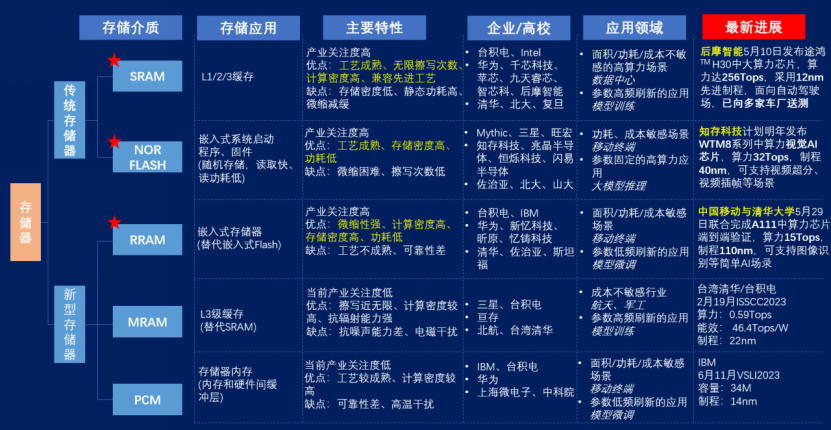

3MRAM存内计算的发展

存内计算对存储介质适配性的评价主要从以下几个方面出发:非易失性、能否形成交叉阵列、不同状态比率、单元计算时输出量、存储密度、功耗、响应速度、工艺成熟度、制造成本、器件一致性等。当前,如图-1c所示,基于多种存储介质的存内计算研究和应用百花齐放,如静态随机存储器(SRAM)、动态随机存储器(DRAM)、闪存(Flash)、忆阻器(ReRAM)、铁电晶体管(FeFET)、相变存储器(PCM)、磁随机存储器(MRAM)等。然而,基于上述评价标准,由于物理特性限制,各类存储介质在存内计算应用的不同场景上各有优劣,尚未出现统一的解决方案。MRAM是非易失器件,具有高耐久性、高速度、低功耗、微缩性好、器件一致性好等优点,当前第一代(Toggle-MRAM)、第二代(STT-MRAM)都已在国外实现量产,基于MRAM的存内计算技术关注度快速提升。

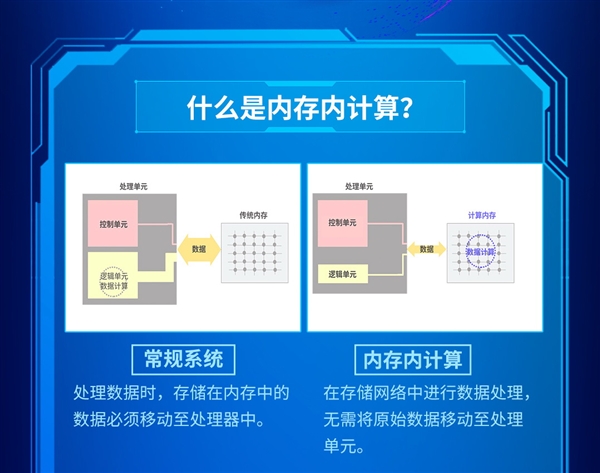

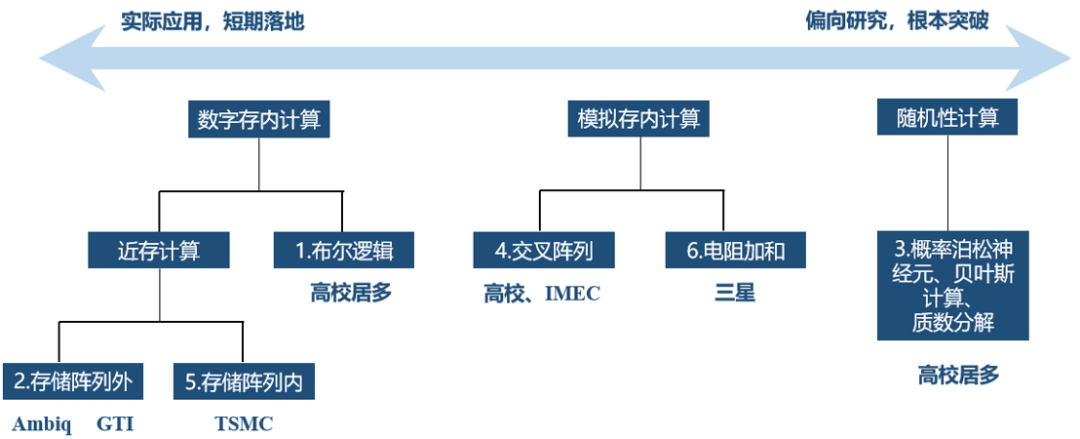

图2 MRAM存内计算技术分布图

笔者按照技术特点对主要的MRAM存内计算进行了大致的分类,如图2所示。

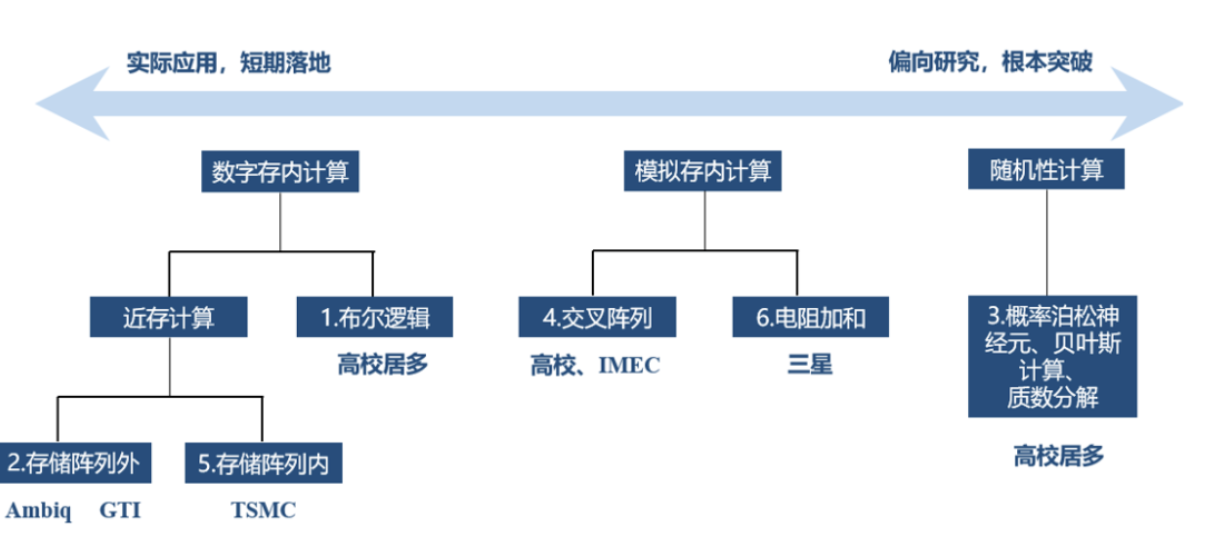

3.1 数字存内计算技术

早期MRAM存内计算技术以数字存内计算技术为主,包含广义上的MRAM近存计算(主要利用其高密度、高速度、非易失的特性,离实际应用较为接近,方便落地)及利用读写外围电路辅助实现布尔逻辑运算的高校研究类工作为主,私以为两者实际非常接近,本质都为近存计算,只是“近的”程度不同(图3)。

图3 中国台湾清华MRAM近存计算方案及北航MRAM布尔逻辑存内计算方案

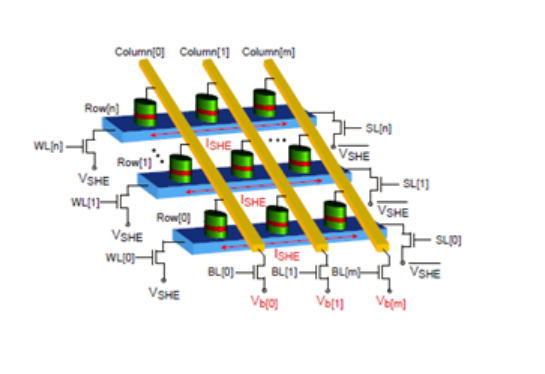

3.2电阻式的模拟存内计算方案

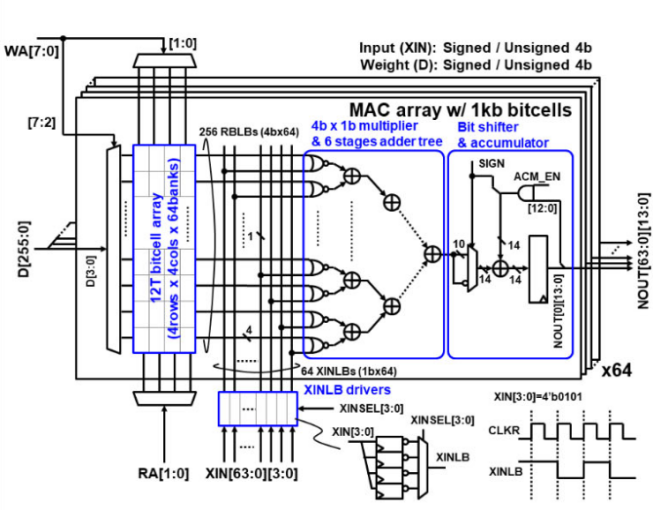

第二类为电阻式的模拟存内计算方案。模拟存内计算一直是近年来的热门,以NOR flash、ReRAM、SRAM等为代表的模拟存内计算方案层出不穷。MRAM由于其出色的一致性、微缩能力、非易失、高密度、工艺成熟度等特性本应十分适合模拟存内计算方案。然而,现有第一、二代MRAM阻值(<10KΩ)及高低阻值比率较低(<300%),只能存储单比特数据,在存内计算底层电路性能上带来诸多不利影响。如何突破MRAM器件物理特性限制,研究高性能的MRAM存内计算电路结构有着重要意义。IMEC采用高阻值的自旋轨道矩(SOT)器件(MΩ级别),解决器件电阻问题,且其高一致性在一定程度上降低了高低阻值比率较小的影响(图4)。三星电子则采用另一条路径,采用电阻加和的形式,提升整体的计算阻值,解决电阻问题,但该方案同样面临面积效率低、计算精度、速度等问题(图5)。

图4 IMEC高阻值SOTMRAM存内计算

图5 三星电子电阻加和式存内计算方案

3.3 概率计算及随机计算

第三类为概率计算及随机计算等方向,其通常利用MRAM本身随机翻转的本征物理特性进行特定问题的计算或概率流的计算。第三类主要由高校在进行研究,应用前景较为受限,此处不再详细展开。

虽然MRAM在模拟存内计算方面受到上述挑战,但目前已有一些有效的解决方案。凭借MRAM密度、非易失等其他优异特性,其在模拟存内计算及数字存内计算方向仍然受到较高的关注。

4 国内存内计算产业的发展

我国的存内计算产业也开始迅猛发展,知存科技、九天睿芯、智芯科、后摩智能、苹芯科技等国内专注存内计算赛道的新兴公司纷纷获得融资,加速在该领域的早期市场布局及商业落地。

以知存科技推出的量产SoC芯片WTM2101,WTM2101基于40 nm工艺进行流片,单个NOR Flash 器件能够存储8 bit权重,因此可以进行8 bit精度的矩阵乘加运算。WTM2101具有4大优势特点:

(1)基于存内计算架构,可高效地实现神经网络语音激活检测和上百条语音命令词识别。

(2)以超低功耗实现神经网络环境降噪算法、健康监测与分析算法。

(3)典型应用场景下,工作功耗均在微瓦级别。

(4)采用极小封装尺寸。

基于以上优势特点, WTM2101可应用于智能可穿戴设备、智能家居、安防监控、玩具机器人等;适应多种应用,如语音识别、语音降噪/增强、轻量级视觉识别、健康监测和声纹识别等。

参考文献

[01]https://tech.sina.com.cn/n/k/2022-01-13/doc-ikyamrmz4934582.shtml

[02]https://www.laoyaoba.com/n/891415

[03]https://36kr.com/p/1665309247756289

[04]https://blog.csdn.net/younger_china/article/details/136058833

[05]郭昕婕等,存内计算芯片研究进展及应用

审核编辑 黄宇

-

存储器

+关注

关注

38文章

7537浏览量

164513 -

芯片架构

+关注

关注

1文章

31浏览量

14596 -

MRAM

+关注

关注

1文章

236浏览量

31827 -

存内计算

+关注

关注

0文章

30浏览量

1412

发布评论请先 登录

相关推荐

存内计算芯片研究进展及应用

从MRAM的演进看存内计算的发展

从MRAM的演进看存内计算的发展

评论