今日正文

(1)怎么看ADC

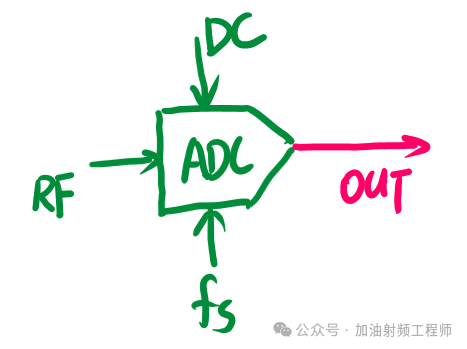

一个ADC,可以把它简单的看成这样一个器件,三个输入,一个输出。

一个输出为数字采样信号输出。

(2)ADC的电源选型

市面上有很多型号的LDO和DC-DC,到底应该选择哪种呢。按理说,指标最高的一般都没问题,但是关键指标高的那不是贵么?所以要是能选个指标没那么好,但是和所用ADC搭配刚刚好的器件,那不是又便宜又性能OK么?

与ADC的电源选型相关的,就是ADC的PSSR和PSMR。

当噪声从ADC的电源端引入的时候,噪声可能会直接出现在ADC的输出端,也有可能是噪声与模拟输入信号产生的调制信号出现在ADC的输出端。

举个例子,假设叠加在DC上的噪声信号的频率为1MHz,模拟输入信号为100MHz,而PSSR关注的是ADC输出端的1MHz频率处的幅度,而PSMR则关注的是ADC输出端在101MHz和99MHz频率处的幅度。

ADC厂家的手册上,很多都没有PSSR和PSMR的详细指标。

如果我们对LDO和DCDC的成本敏感的话,比如说出货量很大,单个器件省点就能省下一大笔钱的话,可能就需要自己做些预研工作,测试一下ADC的PSSR和PSMR随频率变化的曲线,以此来选择合适的电源器件。

如果不敏感的话,可能就不费那个事了,直接高指标的电源器件+高抑制的电源滤波,完事。

(3)ADC的时钟电路

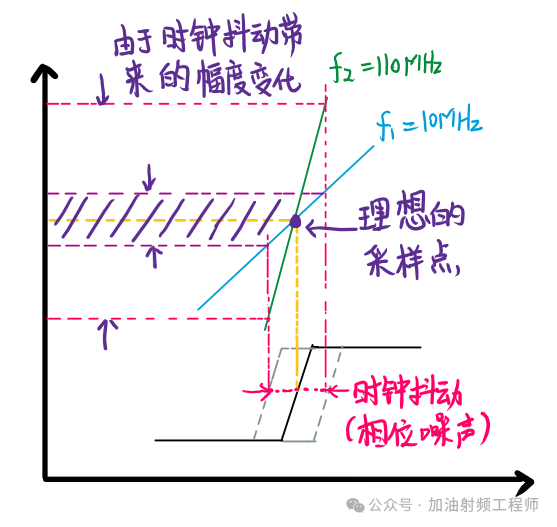

如上图所示,当时钟边沿有抖动的时候,采样的时刻也会有抖动,这样对应的采样数据也会有抖动,而且输入频率越高,由于时钟抖动带来的幅度变化越大。

所以,在评估ADC的时钟是否符合要求的时候,需要综合考虑时钟的抖动带来的影响。

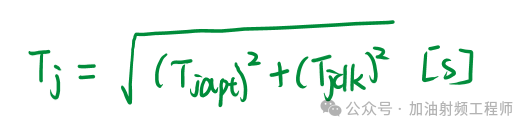

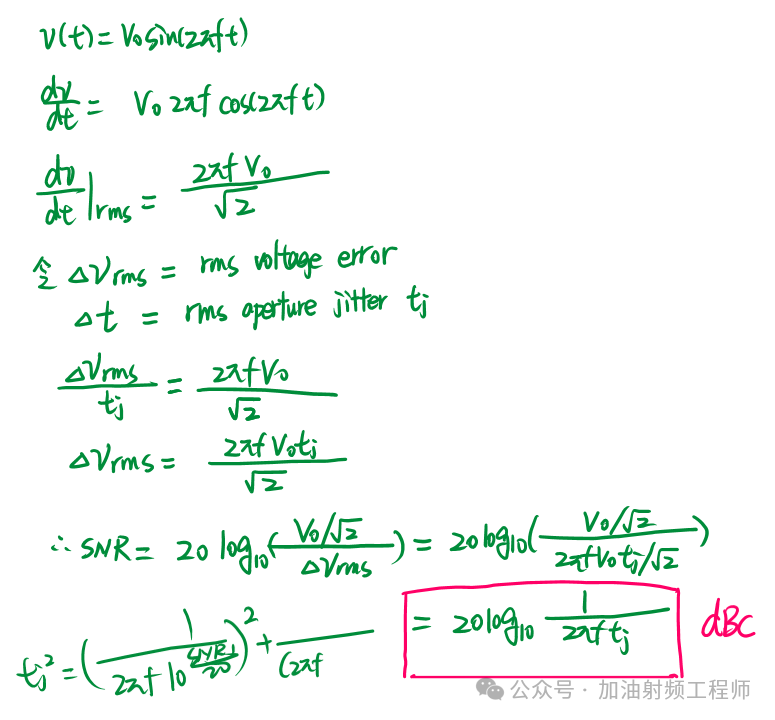

采样时钟抖动Tj是由时钟源(Tjclk)和内部ADC孔径抖动(Tjapt)产生的抖动的组合,即:

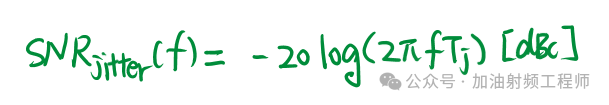

由总抖动导致的ADC的SNR下降,可按以下公式进行计算:

具体推导如下:

这个公式,是假定影响ADC的SNR的只有抖动本身,而ADC的SNR为无穷大。

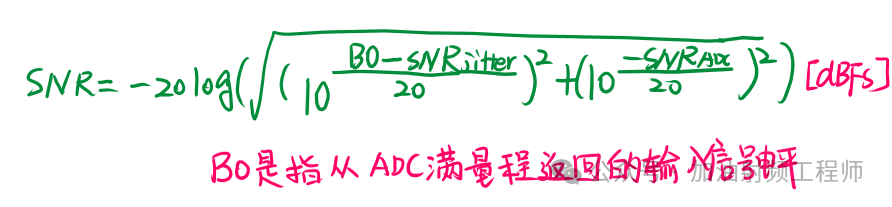

但是,ADC本身受量化噪声和热噪声的影响,所以自身有一个SNR,假设为SNRADC,则:

这边的单位会有点绕,本质上就是由抖动计算出来的SNR的单位是dBc,也就是说以信号的大小为基准的;但是加上ADC本身的SNR之后,由于手册上计算SNR时,都是基于-1dBFS来得到的,所以两者结合起来的时候,划归到统一的单位,即dBFS,所以会有BO这一项。

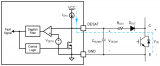

(4)ADC的输入电路

对ADC的输入电路进行设计的时候,需要根据具体要求,来设计电路。

同时还要考虑抗混叠滤波器。

设计完的电路,拿不准的时候,可以用仿真来验证。

-

时钟抖动

+关注

关注

1文章

62浏览量

15965 -

SNR

+关注

关注

3文章

196浏览量

24515 -

ADC采样

+关注

关注

0文章

134浏览量

12903 -

抗混叠滤波器

+关注

关注

1文章

10浏览量

10868

原文标题:用ADC之前,选它外围电路的时候,需要考虑些什么

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

电源外围保外围应用电路

开发经验!嵌入式硬件设计需要考虑的一些问题总结

【开发经验】嵌入式硬件设计需要考虑的一些问题总结

请问设计稳压电路的时候要考虑哪些因素?

一文教你如何进行ADC的外围电路设计!

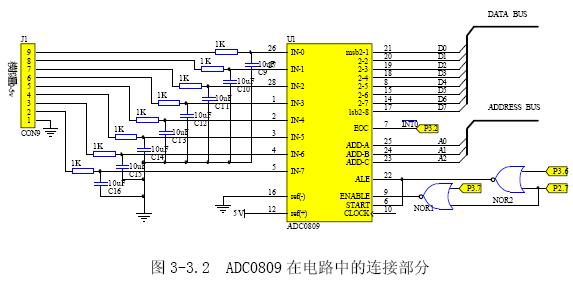

adc0809外围电路

选ADC做外围电路的时候,需要考虑些什么?

选ADC做外围电路的时候,需要考虑些什么?

评论