生产力和工艺良率

概览

晶圆制造和封装是一个极其漫长和复杂的过程,涉及数百个要求严格的步骤。这些步骤从未每次都完美执行,污染和材料变化结合在一起会导致晶圆在生产过程中的损失。此外,晶圆上的一些芯片未能满足客户的电气和性能规范。在本章中,将确定主要的良率测量点以及影响良率的主要工艺和材料因素。还介绍了不同良率点和不同电路的典型良率。

良率测量点

维护和提高工艺和产品良率是半导体制造业的生命线。对一个偶然的观察者来说,似乎整个行业都对生产良率着迷。这种观察确实是正确的。由于工艺的严格要求和生产一个封装芯片所需的庞大工艺数量,导致产品损失。这两个因素导致生产过程通常只发货其投入晶圆制造线的芯片的20%到80%。

这些良率与大多数制造操作相比似乎非常低。然而,考虑到生产由数百万微米或亚微米尺寸图案组成的数百个电路,这些图案层数相等且非常薄,都处于非常严格的清洁水平之内,全部在140毫米^2的芯片限制之内,来自39个不同的掩模,该行业能够生产出功能芯片的事实本身就是一个证明。

另一个有助于保持良率低迷的因素是大多数生产错误的不可修复性。虽然有缺陷的汽车零件可以更换,但在半导体制造业中很少有这样的选择。有缺陷的芯片或晶圆通常无法恢复。在某些情况下,未通过性能测试的芯片可以降级并出售用于要求较低的用途。报废的晶圆可能会找到新的生命,作为控制或监控晶圆。

除了这些工艺因素外,还有业务的批量性质。高昂的资本成本和高于平均水平的工程人员比例转化为高开销业务。这种高开销,加上竞争保持销售价格的下行压力,要求大多数芯片生产商运行高产量、高良率的工艺。

鉴于所有这些因素,对良率的关注是可以理解的。大多数设备和材料供应商都强调其产品可能带来的良率提升。同样,工艺工程团队的主要职责是维护和提高工艺良率。良率测量从单个工艺级别开始,并贯穿整个工艺序列进行跟踪,从进入空白晶圆到完成电路的发货。

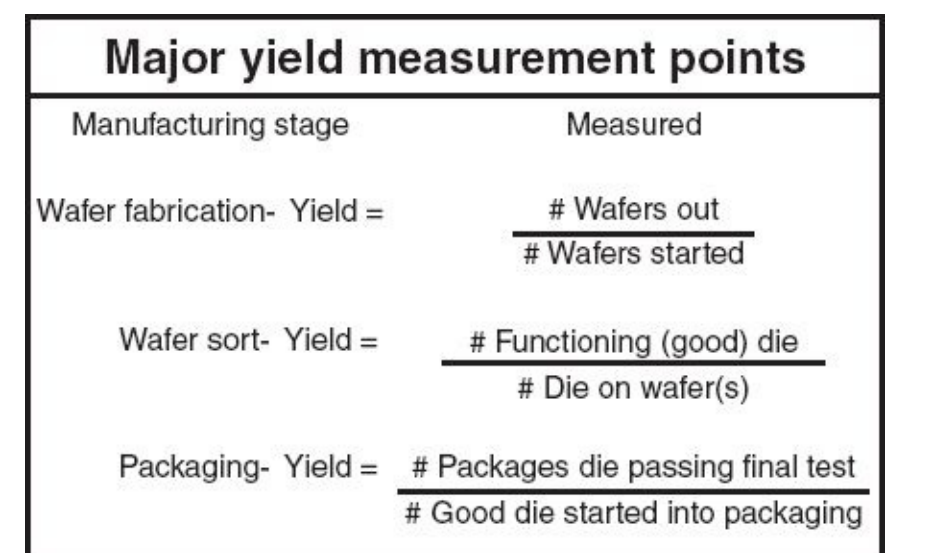

通常,工厂会在工艺的三个主要点监控良率。它们分别在晶圆制造过程结束时、晶圆分选后以及封装和最终测试过程结束时(见下图所示)。

累积晶圆制造良率 一个主要的良率测量点是在晶圆制造完成时。这种良率被称为fab良率、线良率、累积fab良率或“累积”良率。

无论名称如何,它都是以离开晶圆制造的晶圆数量除以进入工艺的晶圆数量的百分比来表示。由于不同类型的产品具有不同的组件、特征尺寸和密度因素,晶圆制造良率是针对每种产品类型而不是整个制造线良率来计算的。

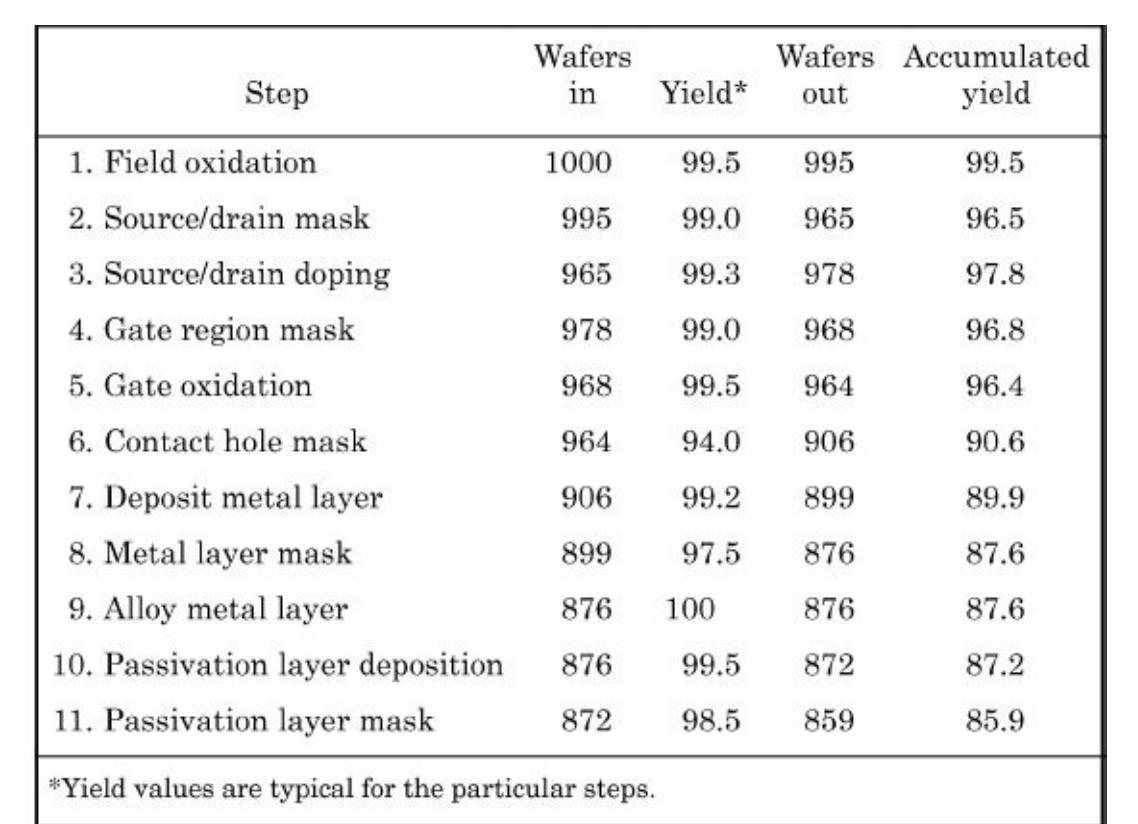

累积fab良率首先通过计算离开每个单独工艺的晶圆数量(称为站点良率)并除以进入该站点的数量来开始。

站点良率又通过相乘来计算整体累积fab良率。

审核编辑:刘清

-

半导体

+关注

关注

335文章

27970浏览量

225146 -

晶圆

+关注

关注

52文章

5021浏览量

128609

原文标题:半导体工艺之氧化(一)

文章出处:【微信号:FindRF,微信公众号:FindRF】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

晶圆制造和封装之影响良率的主要工艺和材料因素(一)

晶圆制造和封装之影响良率的主要工艺和材料因素(一)

评论