一、引言

在数字电路的设计与实现中,亚稳态是一个不可忽视的现象。它可能由多种因素引发,对电路的稳定性和可靠性产生严重影响。本文将深入探讨数字电路中亚稳态的概念、产生原因、影响以及应对策略,以期为读者提供全面而深入的理解。

二、亚稳态的概念

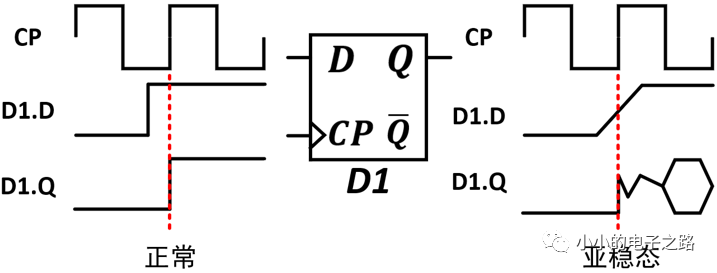

亚稳态,又称为亚稳定状态或不稳定状态,是指触发器或其他数字电路元件在输入信号变化时,其输出在一段时间内处于不确定状态的现象。在这种状态下,电路的输出可能表现为非预期的振荡、中间电平或其他不稳定现象,从而导致电路的功能失效或产生误动作。

三、亚稳态的产生原因

亚稳态的产生原因多种多样,主要包括以下几个方面:

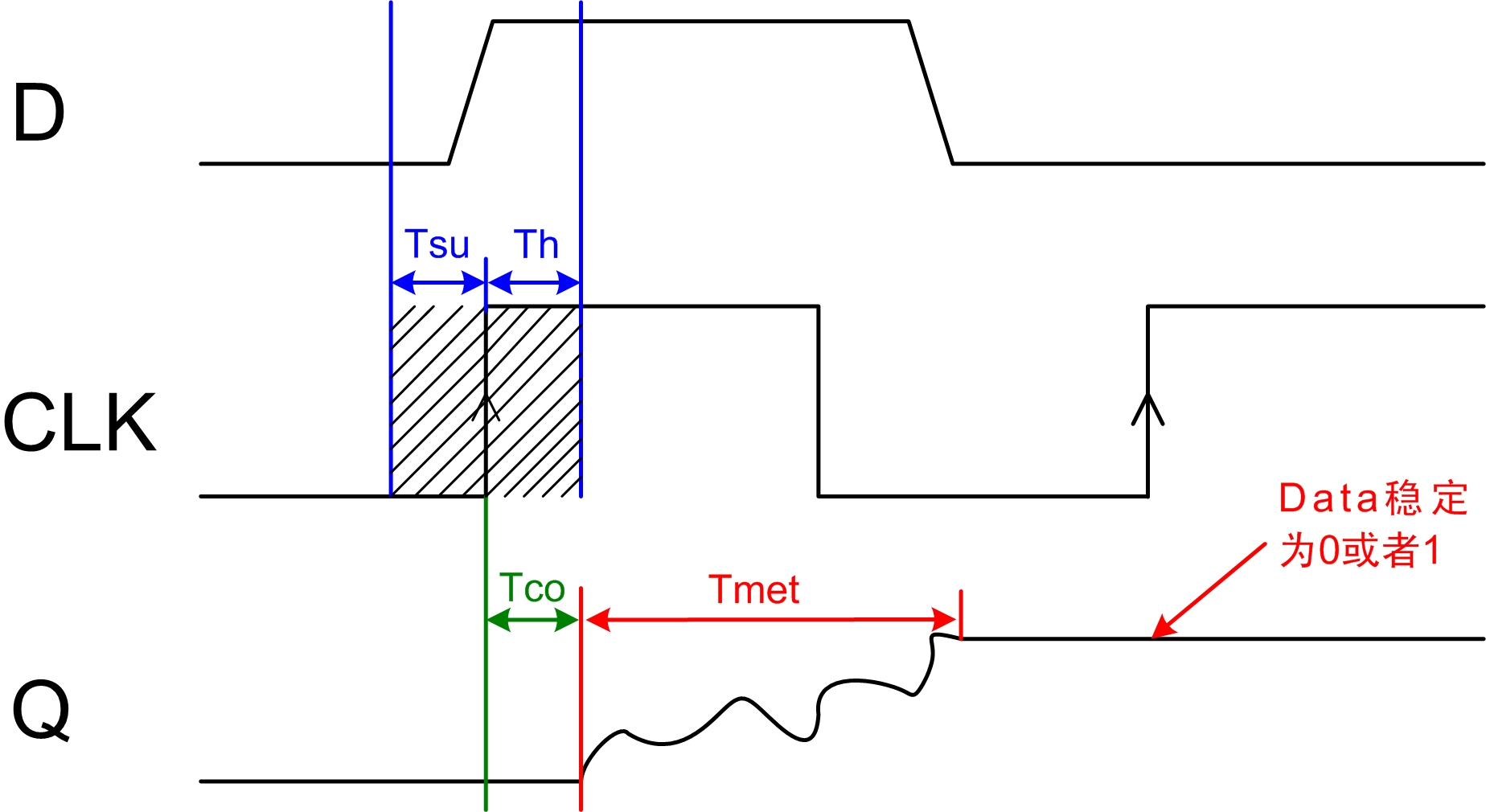

输入信号不满足触发器的建立时间和保持时间要求:建立时间是指在时钟边沿到来之前输入信号必须保持稳定的时间;保持时间是指在时钟边沿到来之后数据必须保持稳定的时间。如果输入信号在这两个时间段内没有保持稳定,就可能导致触发器进入亚稳态。

电源干扰和噪声:电源噪声、电磁干扰等因素可能导致电路中的信号发生畸变或抖动,从而引发亚稳态现象。

环境因素:温度、湿度、压力等环境因素的变化也可能对电路的稳定性产生影响,进而引发亚稳态现象。

元器件故障:元器件的老化、损坏或性能下降也可能导致电路进入亚稳态。

四、亚稳态的影响

亚稳态对数字电路的影响主要表现在以下几个方面:

输出信号失真:在亚稳态期间,电路的输出信号可能表现为非预期的振荡、中间电平或其他不稳定现象,导致输出信号失真。

逻辑混乱:由于输出信号的不确定性,与其相连的其他数字部件可能对其作出不同的判断,导致整个电路的逻辑混乱。

复位失败:在复位电路中产生亚稳态可能导致复位失败,使电路无法正常工作。

系统崩溃:在复杂系统中,亚稳态可能导致系统崩溃或死机,造成严重的后果。

五、亚稳态的应对策略

为了降低亚稳态对数字电路的影响,可以采取以下应对策略:

引入同步机制:通过引入同步机制,可以确保电路中的各个部分在相同的时钟周期内进行操作,从而降低亚稳态的发生概率。

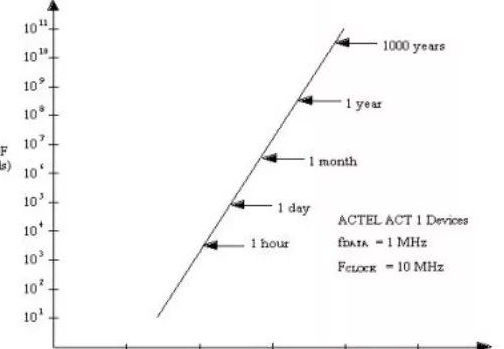

采用响应更快的触发器:使用具有更短建立时间和保持时间的触发器可以降低输入信号不满足要求时进入亚稳态的风险。

降低时钟频率:降低时钟频率可以减少电路中的信号传输速度和抖动,从而降低亚稳态的发生概率。但需要注意的是,过低的时钟频率可能会影响电路的性能。

使用防抖电路:防抖电路可以在输入信号发生变化时暂时屏蔽其影响,从而避免触发器进入亚稳态。但需要注意的是,防抖电路可能会增加电路的复杂性和成本。

优化电路设计:通过优化电路设计,如减少不必要的元件、优化信号路径等,可以降低亚稳态的发生概率。

加强电源和噪声抑制:通过加强电源滤波、使用屏蔽线等措施可以降低电源噪声和电磁干扰对电路的影响,从而降低亚稳态的发生概率。

六、亚稳态电路的应用与挑战

尽管亚稳态对数字电路的稳定性和可靠性产生了一定的影响,但它在某些应用中却具有一定的意义。例如,在数字信号处理、误码纠正等领域中,亚稳态电路可以被用来实现特定的功能。然而,随着技术的不断发展,对数字电路的稳定性和可靠性要求越来越高,亚稳态电路的应用也面临着一些挑战和限制。

七、结论

亚稳态是数字电路中一个不可忽视的现象。通过深入了解其概念、产生原因、影响以及应对策略,我们可以更好地设计和实现数字电路,提高其稳定性和可靠性。同时,我们也需要认识到亚稳态电路的应用与挑战,并不断探索新的解决方案以满足不断提高的技术要求。

-

数字电路

+关注

关注

193文章

1631浏览量

81039 -

亚稳态

+关注

关注

0文章

47浏览量

13366

发布评论请先 登录

相关推荐

数字电路中的亚稳态是什么

数字电路中的亚稳态是什么

评论