审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

仿真

+关注

关注

50文章

4134浏览量

134124

发布评论请先 登录

相关推荐

AD转换中需要注意电流的回流路径,这个电流的回流路径具体指的是什么呢?

AD转换中需要注意 电流的回流路径 这个电流的回流路径具体指的是什么呢

是不是单片机和AD转换芯片之间的数据线和DGND线构成一个回路输入信号和AGND构成一个回路

发表于 02-14 07:53

如何使用Matter创建AIoT连接

人工智能 (AI) 与物联网 (IoT) 不断融合,形成了人工智能物联网 (AIoT),为各个细分市场的开发人员带来了诸多机遇。随着连接的互操作性日益提高,物联网将收集大量的原始数据。能够分析、学习

termius如何使用,termius如何使用的过程,linux服务器远程连接的实用教程

的实用教程。 (一).termius如何使用的过程: 先创建连接,填写服务器信息与认证信息后保存。连接成功后在命令行输入命令操作服务器,如“pwd”查路径等。文件传输时,进

多台仓储AGV协作全局路径规划算法的研究

多AGV动态路径规划需解决冲突避免,核心在整体协调最优。规划时考虑道路设计、拥堵、最短路径和交通管制,用A*算法避免重复路径和转弯,同时需交通管制防相撞。创新响应需求是关键,良好路径规

虚拟桌面基础架构(VDI)远程连接如何实现

平台部署VMware或Citrix这样的虚拟化软件。2、创建虚拟桌面使用虚拟化平台创建多个虚拟桌面。3、配置网络确保网络连接稳定,以支持远程访问。4、分配用户访问

SD-WAN技术在直播网络中如何实现智能路径选择?

SD-WAN技术在直播网络中实现智能路径选择主要通过以下几个步骤: 1、实时网络监控:SD-WAN系统持续监控所有可用的网络路径,包括它们的带宽、延迟、丢包率和抖动等关键性能指标。 2、路径评估

为什么在espconn_secure_accept创建的服务器上无法有多个安全连接?

为什么在espconn_secure_accept创建的服务器上无法有多个安全连接?

发表于 07-22 08:10

鸿蒙开发:创建PageAbility

通过DevEco Studio开发平台创建PageAbility时,DevEco Studio会在app.js/app.ets中默认生成onCreate()和onDestroy()方法,其他方法需要开发者自行实现。

Espressif-IDE创建工程项目时出现cdt构建环境变量中找不到路径的情况,为什么?

如图

路径错误.png (17.2 KiB) Viewed 1272 times

而后根据提示进行配置 安装工具,但又出现如下信息

WARNING: Git was not found

发表于 06-11 06:48

基于隐形飞机喷气式发动机双S弯喷管的纤维缠绕工艺

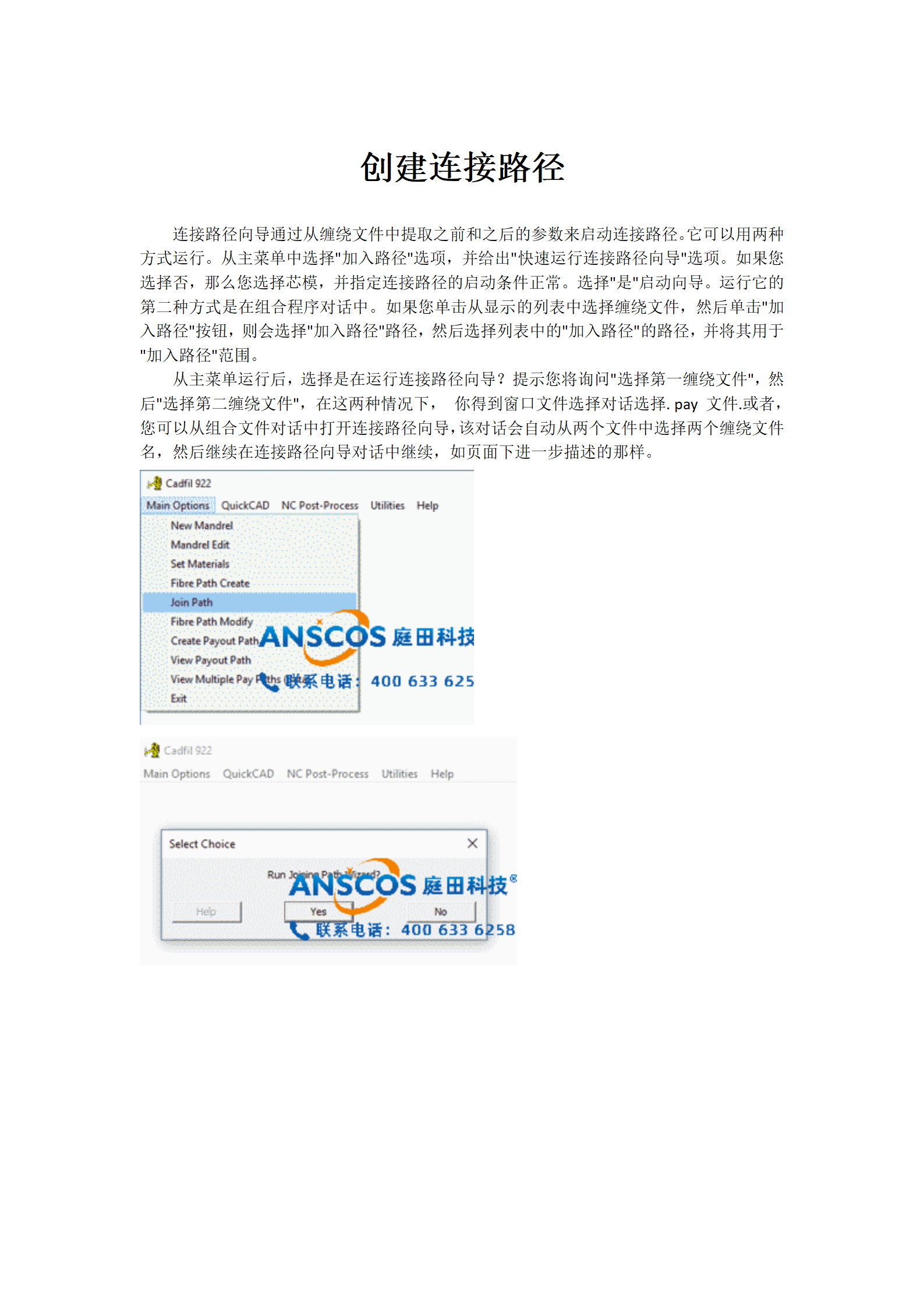

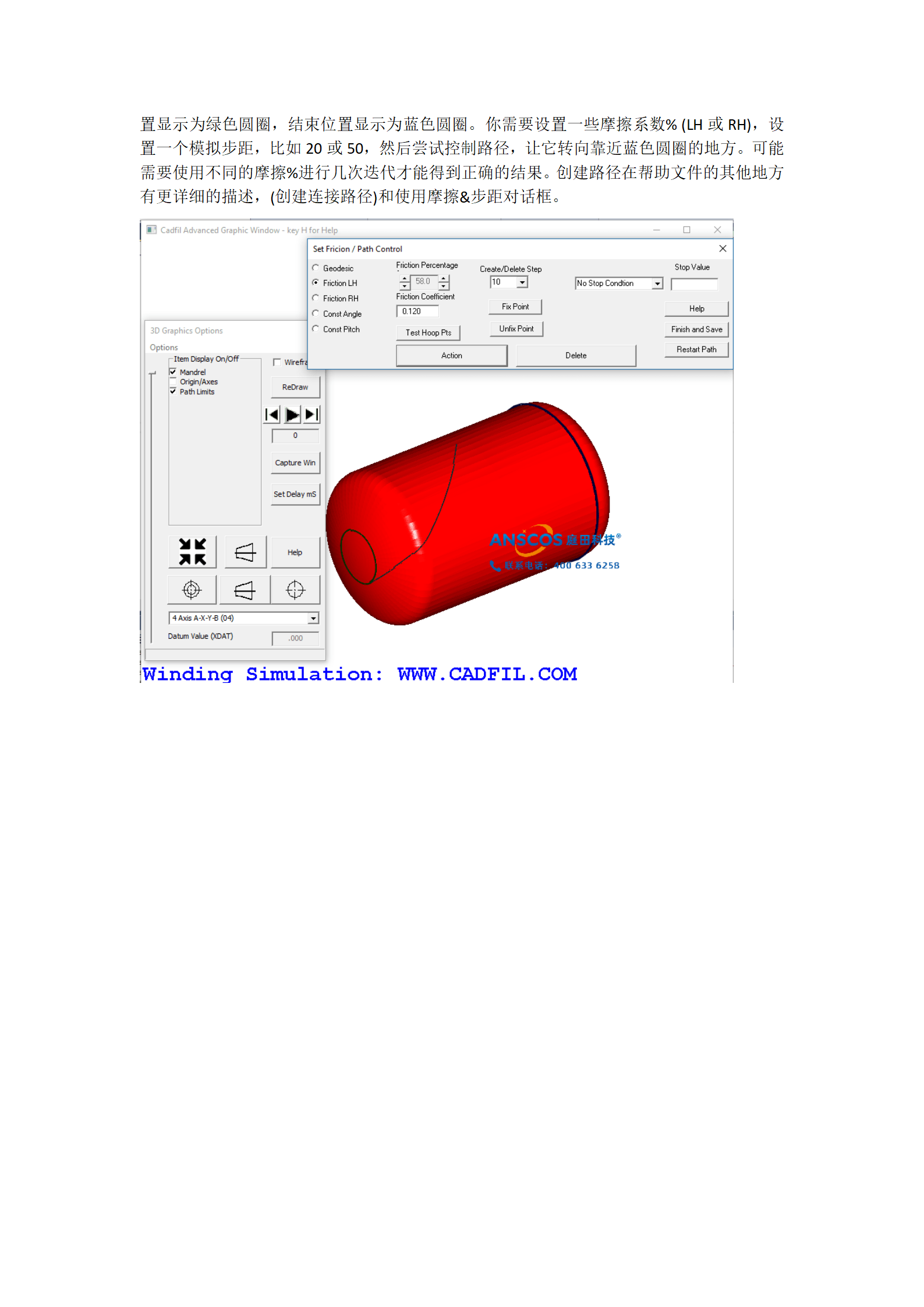

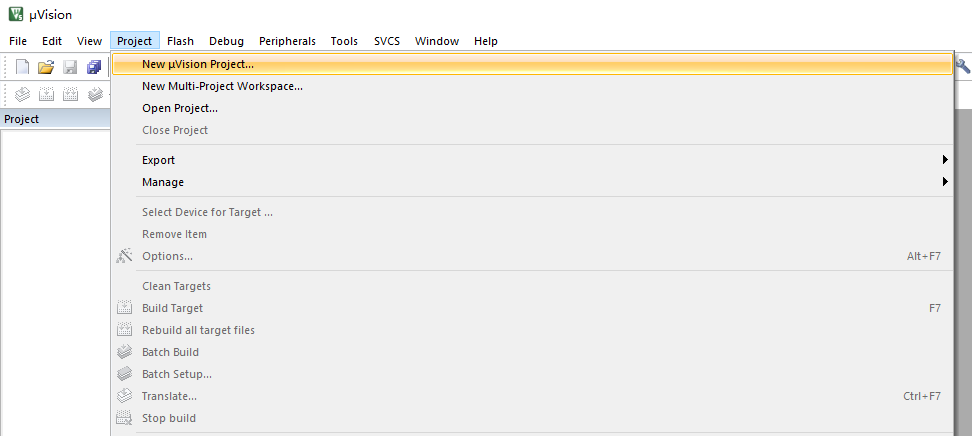

使用了一种基于使用相对于弯曲脊柱生成的螺旋路径的方法。这类似于相对于轴线为直线的普通圆管的轴线缠绕螺旋线。下面简要总结了在Cadfil中创建蜿蜒路径的过程。

图2 使用

发表于 04-19 09:52

CW32F003E4芯片入门学习:3.工程模板的创建(不使用例程或模板)

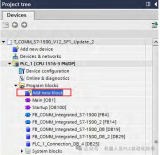

1.2.1.新建keil工程文件夹 创建一个文件夹为CW32_new_pro,注意避免出现中文路径和特殊符号 1.2.2.创建keil工程 打开keil,选择Project->New uVision

博途:TCP通讯连接参数配置指南

您需要一个“TCON_Param”类型的数据块来存储TCON通信指令的连接参数。以下是如何创建“TCON_Param”类型的数据块的说明。

发表于 02-29 11:33

•5785次阅读

Cadfil创建连接路径

Cadfil创建连接路径

评论