根据电荷守恒原理,在一个孤立回路中,电荷代数和总是相等不变。

对于一个1F的电容,当它的压差为1V时,它所携带的电荷量是Q=CU=1库仑,这里的电荷量是指电容的两个极板各自携带的电荷量的绝对值是1C。定义极板正负后,正极板携带的是1库仑的正电荷,负极板携带的是1库仑的负电荷。正负极板的电荷量绝对值永远是相同的,电容的电压并非是正负极板的电荷量绝对值不同产生的。

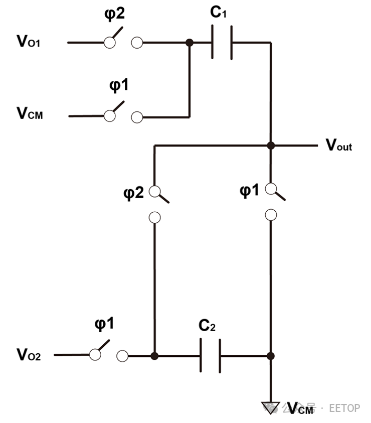

从电荷角度理解开关电容加法器中的电荷守恒,开关电容加法器的电路如下所示:

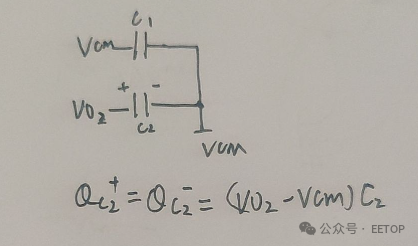

φ1时C2对Vo2采样,C1清零,选定C2的正负之后不再改变,计算C2的正负极板电荷如下图所示:

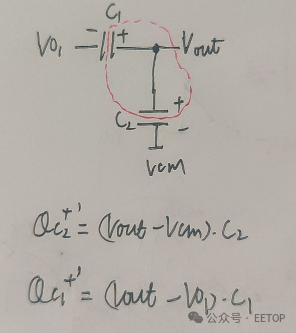

φ2时C1对Vo1采样,并产生输出电压Vout。因为C2的上极板是正并与C1的右极板连接,同一个节点连接的极板极性相同,所以定义C1左负右正。因为C1右极板要变成正极性,所以右极板电子要往C2正极板移动直到稳定,此时电子也会从Vo1流向C1的负极板以保持C1的正负极板电荷量相同。

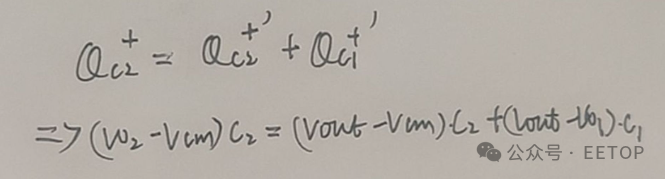

在上述过程达到稳定时,由于电容正负极板之间是断路,所以在Vout节点只是C1正极板的电子流向C2的正极板而无外部电荷流入或内部电荷流出,所以这个节点的电荷总量是守恒的,因此稳定时(φ2时C1正极板电荷量+φ2时C2正极板电荷量)=φ1时C2正极板电荷量,所以:

由上式可以求得Vout的表达式。

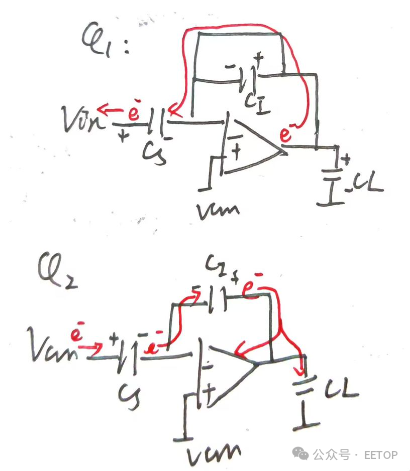

以开关电容积分器为例说明什么样的节点是电荷守恒,一个考虑负载电容CL的开关电容积分器电路在φ1和φ2时电路如下:

Phi1时CS采样,定义Cs左正右负,电子从运放输出流到Cs的右极板使得右极板变负,当然CL上极板也会有电子流出使得CL上极板变正。

Phi2时,假定VCM小于Vin,那么一开始运放负输入端电压会向下跳变,因为电容的电压无法突变。由于负反馈,运放输出电流对负输入端进行充电,电子流向如图。

在这个过程中,Cs的负极板电子流向CI左极板,电子只是从CS的负极板移到CI的负极板,所以在运放负输入端看到的总负电荷量是没有变化的,因此这个节点是电荷守恒的,对这个节点列写电荷守恒方程是可以求出VO的。

那运放输出端会符合电荷守恒吗?但如果看运放输出端时这并不是一个封闭的系统,因为CI的电子在移动到CL上的同时,还会有部分电子电流流向运放到VDD,所以Vo节点看到的总电荷是减少的,该节点不适用电荷守恒,无法列写该节点的电荷守恒方程。

值得注意的是,不是所有节点都符合电荷守恒,只要这个节点无能够从外部充放电的支路而只与电容极板相连,那这个节点就是电荷守恒的。

审核编辑:刘清

-

加法器

+关注

关注

6文章

183浏览量

30123 -

开关电容

+关注

关注

0文章

101浏览量

18438 -

电容电压

+关注

关注

0文章

74浏览量

11212

原文标题:开关电容加法器的电路如下所示:

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

十进制加法器,十进制加法器工作原理是什么?

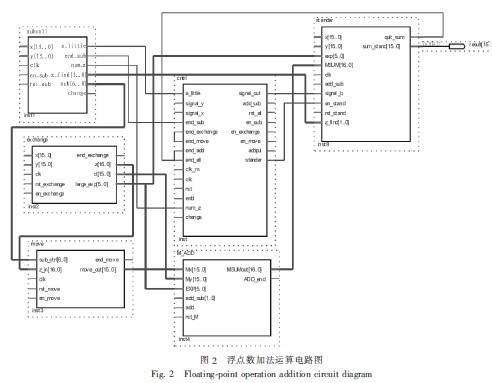

FPU加法器的设计与实现

同相加法器电路原理与同相加法器计算

加法器是什么?加法器的原理,类型,设计详解

加法器工作原理_加法器逻辑电路图

开关电容加法器的电路详解

开关电容加法器的电路详解

评论