瑞萨RZ/T2M MPU

RZ/T2M是一款行业领先的高性能、多功能MPU,可实现AC伺服系统和工业电机等工业设备的高速处理、高精度控制和功能安全。RZ/T2M具有最大频率为800 MHz的双Arm Cortex-R52内核,可进行实时控制,而且还拥有能够与CPU直接连接的大容量紧密耦合内存(576KB),以实现高性能实时处理。此外,它还可以将电机控制的外设布置到能直接连接至CPU的LLPP(低延迟外设端口)上,来实现较低的延迟访问。RZ/T2M拥有多协议编码器硬件接口,可为A-format、EnDat 和BiSS等各种绝对编码器协议提供支持。此外,RZ/T2M还拥有一个3端口的千兆以太网交换机,可为TSN标准及EtherCAT、PROFINET RT/IRT和EtherNet/IP等工业以太网协议提供支持,而无需额外的以太网交换机IC。

瑞萨RZ/N2L MPU

RZ/N2L是一种工业以太网通信用MPU,可轻松将网络功能添加到工业设备中。它搭载支持TSN的三端口千兆以太网交换机和EtherCAT从控制器,可支持EtherCAT、PROFINET RT/IRT、EtherNet/IP、OPC UA等主要的工业以太网通信协议。它对网络专用配套芯片加以优化,无需大幅改变设备的内部配置即可直接连接并快速访问外部应用主机CPU。此外,Arm Cortex-R52的最大工作频率为400MHz,外设功能包括带ECC的大容量RAM与ΔΣ I/F、A/D转换器、PWM定时器、UART和CAN等,可在单个芯片上实现远程I/O、传感器集线器、变频器和网关。

认证步骤

安装所需的IAR版本

配置项目一般选项

配置调试器设置选项

配置调试器额外选项

记录认证过程

提示

使用注意事项

安装所需的IAR版本

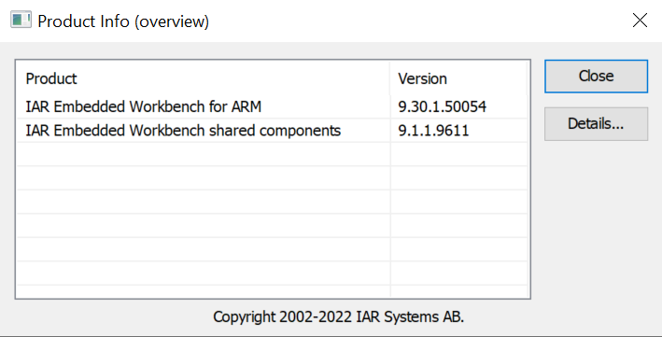

对于RZ/T2M,安装IAR EW for Arm v9.30.1或以上版本

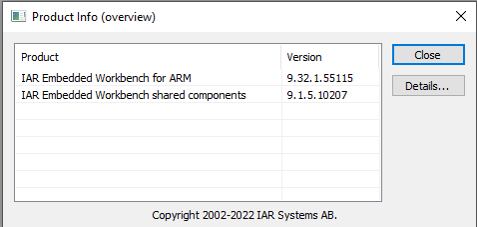

对于RZ/N2L,安装IAR EW for Arm v9.32.1或以上版本

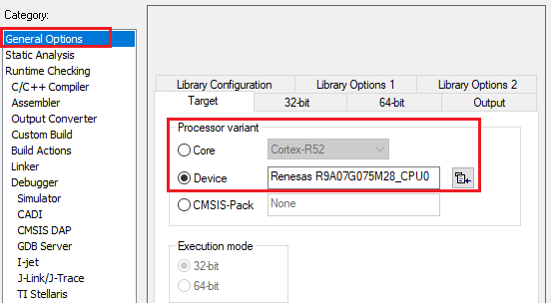

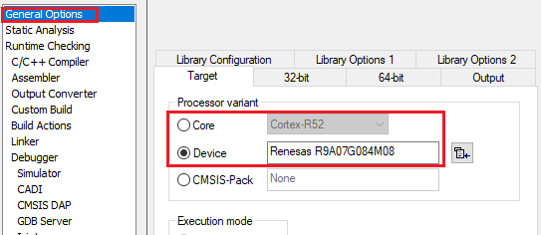

配置项目一般选项

RZ/T2M & RZ/N2L

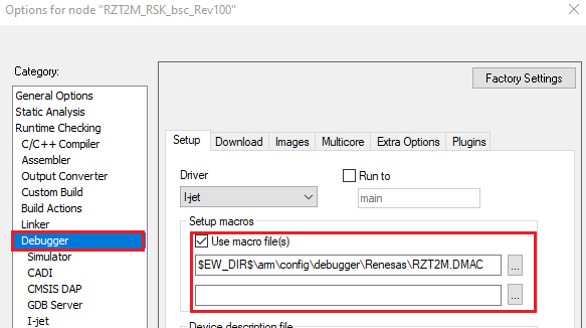

配置调试器设置选项

RZ/T2M & RZ/N2L

*RZ/T2M和RZ/N2L使用相同的DMAC文件,即RZT2M.DMAC

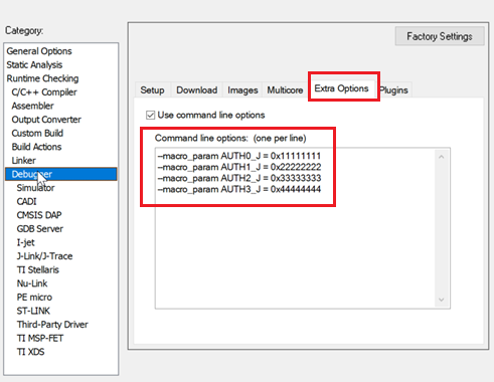

配置调试器额外选项

RZ/T2M & RZ/N2L

IAR C-SPY调试器平台提供C-SPY宏让用户自定义调试过程,包括I-jet连接阶段

详细信息请参阅位于Embedded Workbench xxxarmdoc 中随附的EWARM_IjetConnectMacros.pdf

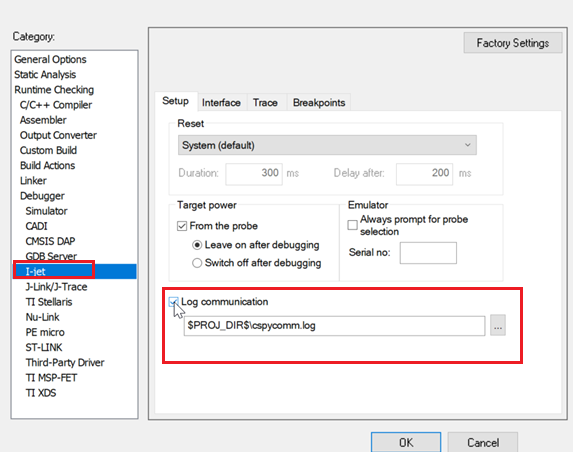

记录认证过程

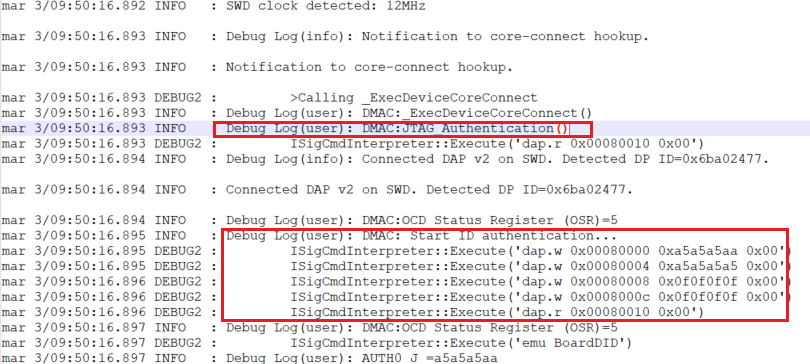

I-jet认证参考日志:

mar 3/09:50:16.355 DEBUG2 : StartSession() mar 3/09:50:16.355 INFO : Debug Log(info): Loading the I-jet driver mar 3/0916.355 DEBUG2 : -> ConnectToHardware() mar 3/0916.356 DEBUG2 : -> CreateJetTerminal() mar 3/0916.356 DEBUG2 : <- CreateJetTerminal() mar 3/0916.356 DEBUG2 : -> AcquireSigAPIPtr() mar 3/0916.356 DEBUG2 : SigAPISetPath('C:Program FilesIAR SystemsEmbedded Workbench 9.1_3arminjetin') mar 3/0916.394 DEBUG2 : <- AcquireSigAPIPtr() mar 3/0916.394 DEBUG2 : -> CreateSigProbe() mar 3/0916.430 DEBUG2 : SigProbe version: 1.67 mar 3/0916.430 DEBUG2 : <- CreateSigProbe() mar 3/0916.430 DEBUG2 : -> SigProbeInit() mar 3/0916.431 DEBUG2 : <- SigProbeInit() mar 3/0916.431 INFO : Debug Log(info): Probe: Probe SW module ver 1.67 mar 3/0916.431 INFO : Probe: Probe SW module ver 1.67 mar 3/0916.431 INFO : Debug Log(info): Probe: Option: trace(Auto,size_limit=100%) mar 3/0916.431 INFO : Probe: Option: trace(Auto,size_limit=100%) mar 3/0916.431 DEBUG2 : -> ConnectToProbe() mar 3/0916.431 DEBUG2 : ISigProbe::EnumScan() mar 3/0916.545 INFO : Debug Log(info): Probe: Found I-jet, SN=84469 mar 3/09:50:16.545 INFO : Probe: Found I-jet, SN=84469 mar 3/09:50:16.545 DEBUG2 : scanning finished: found 1 probes mar 3/09:50:16.546 DEBUG2 : connection Serial No: 84469 mar 3/09:50:16.556 DEBUG2 : connection found probes: mar 3/09:50:16.570 INFO : Debug Log(info): Probe: Opened connection to I-jet:84469 mar 3/09:50:16.570 INFO : Probe: Opened connection to I-jet:84469 mar 3/09:50:16.602 INFO : Debug Log(info): Probe: USB connection verified (15179 packets/s) mar 3/09:50:16.602 INFO : Probe: USB connection verified (15179 packets/s) mar 3/09:50:16.602 INFO : Debug Log(info): Probe: I-jet, FW ver 8.2, HW Ver:A mar 3/09:50:16.602 INFO : Probe: I-jet, FW ver 8.2, HW Ver:A mar 3/09:50:16.729 INFO : Debug Log(info): Probe: MIPI20 adapter detected mar 3/09:50:16.729 INFO : Probe: MIPI20 adapter detected mar 3/09:50:16.729 INFO : Debug Log(info): Probe: Versions: JTAG=1.95 SWO=1.41 A2D=1.74 Stream=1.52 SigCom=2.46 mar 3/09:50:16.729 INFO : Probe: Versions: JTAG=1.95 SWO=1.41 A2D=1.74 Stream=1.52 SigCom=2.46 mar 3/09:50:16.730 DEBUG2 : <- ConnectToProbe() mar 3/09:50:16.730 DEBUG2 : -> CreateSigEmus() mar 3/09:50:16.730 DEBUG2 : ISigAPI::CreateInstance('ISigEmu', 'EARM', '') mar 3/0916.768 DEBUG2 : Core 0: sigEmu->LinkAttach(ISigProbe) mar 3/0916.768 DEBUG2 : core 0: IsigEmu::ParamSet('Emulator', 'ijet') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('Processor', 'Cortex-R52') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('JtagHeader', 'ARM-SWD') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('CoreSightSWJ', 'SWD') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('JTagSpeed', 'auto') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('BoardCfg', 'C:Program FilesIAR SystemsEmbedded Workbench 9.1_3arm/config/debugger/Renesas/RZT2M_CPU0.ProbeConfig') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('JtagInitDelay', '200,r:300') mar 3/09:50:16.768 DEBUG2 : core 0: IsigEmu::ParamSet('BigEndian', '0') mar 3/09:50:16.768 DEBUG2 : ISigEmu::LinkAttach('SigTerminalLog'...) mar 3/09:50:16.768 DEBUG2 : Core 0: sigEmu->LinkAttach(SigTerminalLog) mar 3/09:50:16.768 DEBUG2 : <- CreateSigEmus() mar 3/09:50:16.768 DEBUG2 : -> CreateInterfaceComProtocol() mar 3/09:50:16.768 DEBUG2 : ISigProbe::AcquireInterface('ComProtocol') mar 3/09:50:16.768 DEBUG2 : <- CreateInterfaceComProtocol() mar 3/09:50:16.768 DEBUG2 : -> CollectCoreNames() mar 3/09:50:16.779 DEBUG2 : <- CollectCoreNames() mar 3/09:50:16.779 DEBUG2 : -> DoIceConnect() mar 3/09:50:16.779 DEBUG2 : core 0: IsigEmu::ParamSet('BoardDID', 'CR52_0') mar 3/09:50:16.779 DEBUG2 : Core 0: IceConnect(...) mar 3/09:50:16.812 DEBUG2 : <- DoIceConnect() mar 3/09:50:16.812 DEBUG2 : -> DoIceInit() mar 3/09:50:16.812 DEBUG2 : Core 0: IceInit(...) mar 3/09:50:16.856 DEBUG2 : ISigEmu::IceVersion(204) mar 3/09:50:16.856 INFO : Debug Log(info): Emulation layer version 5.16 mar 3/09:50:16.856 DEBUG2 : ISigEmu::IceStatus(0) mar 3/09:50:16.856 DEBUG2 : <- DoIceInit() mar 3/09:50:16.856 DEBUG2 : -> CreateCmdInterpreter() mar 3/09:50:16.856 DEBUG2 : ISigProbe::CreateInstance(..., 'SigCmdInterpreter', '') mar 3/0916.888 DEBUG2 : <- CreateCmdInterpreter() mar 3/0916.888 DEBUG2 : ISigCmdInterpreter::LinkAttach('ISigEmu',...) mar 3/0916.888 DEBUG2 : -> AcquireA2DInterface() mar 3/0916.889 DEBUG2 : ISigProbe::AcquireInterface('ISigA2D') mar 3/09:50:16.889 DEBUG2 : ISigA2D::LinkAttach('SigEmu',...) mar 3/09:50:16.889 DEBUG2 : ISigA2D::LinkAttach('SigTerminalLog',...) mar 3/09:50:16.889 DEBUG2 : ISigA2D::Init('null') mar 3/09:50:16.892 INFO : Debug Log(info): SWD clock detected: 12MHz mar 3/09:50:16.892 INFO : SWD clock detected: 12MHz mar 3/09:50:16.893 INFO : Debug Log(info): Notification to core-connect hookup. mar 3/09:50:16.893 INFO : Notification to core-connect hookup. mar 3/09:50:16.893 DEBUG2 : >Calling _ExecDeviceCoreConnect mar 3/09:50:16.893 INFO : Debug Log(user): DMAC:_ExecDeviceCoreConnect() mar 3/09:50:16.893 INFO : Debug Log(user): DMAC:JTAG_Authentication() mar 3/09:50:16.893 DEBUG2 : ISigCmdInterpreter::Execute('dap.r 0x00080010 0x00') mar 3/09:50:16.894 INFO : Debug Log(info): Connected DAP v2 on SWD. Detected DP ID=0x6ba02477. mar 3/09:50:16.894 INFO : Connected DAP v2 on SWD. Detected DP ID=0x6ba02477. mar 3/09:50:16.894 INFO : Debug Log(user): DMAC:OCD Status Register (OSR)=5 mar 3/09:50:16.895 INFO : Debug Log(user): DMAC: Start ID authentication... mar 3/09:50:16.895 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080000 0xa5a5a5aa 0x00') mar 3/09:50:16.895 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080004 0xa5a5a5a5 0x00') mar 3/09:50:16.896 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080008 0x0f0f0f0f 0x00') mar 3/09:50:16.896 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x0008000c 0x0f0f0f0f 0x00') mar 3/09:50:16.896 DEBUG2 : ISigCmdInterpreter::Execute('dap.r 0x00080010 0x00') mar 3/09:50:16.897 INFO : Debug Log(user): DMAC:OCD Status Register (OSR)=5 mar 3/09:50:16.897 DEBUG2 : ISigCmdInterpreter::Execute('emu BoardDID') mar 3/09:50:16.897 INFO : Debug Log(user): AUTH0_J =a5a5a5aa mar 3/09:50:16.897 INFO : Debug Log(user): AUTH1_J =a5a5a5a5 mar 3/09:50:16.897 INFO : Debug Log(user): AUTH2_J =f0f0f0f mar 3/09:50:16.897 INFO : Debug Log(user): AUTH3_J =f0f0f0f mar 3/09:50:16.897 DEBUG2 :) = 0 mar 3/09:50:16.919 INFO : Debug Log(minor): CPU status OK mar 3/09:50:16.919 DEBUG2 : <- AcquireA2DInterface() mar 3/09:50:16.919 DEBUG2 : -> AcquireEmuVectInterface() mar 3/09:50:16.919 DEBUG2 : ISigEmu::AcquireInterface('ISigEmuVect') (core 0) mar 3/09:50:16.919 DEBUG2 : <- AcquireEmuVectInterface() mar 3/09:50:16.919 DEBUG2 : -> AcquireEmuWptInterface() mar 3/09:50:16.919 DEBUG2 : ISigEmu::AcquireInterface('ISigEmuWpt') mar 3/09:50:16.920 DEBUG2 : <- AcquireEmuWptInterface() mar 3/09:50:16.920 DEBUG2 : -> AcquirePcSamplerInterface() mar 3/09:50:16.920 DEBUG2 : ISigEmu::AcquireInterface('ISigPcSampler') mar 3/09:50:16.920 DEBUG2 : <- AcquirePcSamplerInterface() mar 3/09:50:16.920 DEBUG2 : <- ConnectToHardware() mar 3/09:50:16.920 DEBUG2 : LowLevelReset(hardware, delay 200) mar 3/09:50:16.921 INFO : Debug Log(info): LowLevelReset(hardware, delay 200) mar 3/09:50:16.921 DEBUG2 : core 0: IsigEmu::ParamSet('JtagInitDelay', '200,r:300') mar 3/09:50:16.921 DEBUG2 : core 0: IsigEmu::ParamSet('ResetStyle', 'HARDWARE') mar 3/09:50:16.921 DEBUG2 : Core 0: hardware reset mar 3/09:50:17.241 DEBUG2 : -> LowLevelReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:17.644 INFO : Debug Log(info): Notification to init-after-hw-reset hookup. mar 3/09:50:17.644 INFO : Notification to init-after-hw-reset hookup. mar 3/09:50:17.644 DEBUG2 : Calling _ExecDeviceCoreConnect mar 3/09:50:17.644 INFO : Debug Log(user): DMAC:_ExecDeviceCoreConnect() mar 3/09:50:17.645 INFO : Debug Log(user): DMAC:JTAG_Authentication() mar 3/09:50:17.645 DEBUG2 : ISigCmdInterpreter::Execute('dap.r 0x00080010 0x00') mar 3/09:50:17.646 INFO : Debug Log(user): DMAC:OCD Status Register (OSR)=1 mar 3/09:50:17.646 INFO : Debug Log(user): DMAC: Start ID authentication... mar 3/09:50:17.646 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080000 0xa5a5a5aa 0x00') mar 3/09:50:17.646 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080004 0xa5a5a5a5 0x00') mar 3/09:50:17.646 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x00080008 0x0f0f0f0f 0x00') mar 3/09:50:17.647 DEBUG2 : ISigCmdInterpreter::Execute('dap.w 0x0008000c 0x0f0f0f0f 0x00') mar 3/09:50:17.647 DEBUG2 : ISigCmdInterpreter::Execute('dap.r 0x00080010 0x00') mar 3/09:50:17.647 INFO : Debug Log(user): DMAC:OCD Status Register (OSR)=5 mar 3/09:50:17.647 DEBUG2 : ISigCmdInterpreter::Execute('emu BoardDID') mar 3/09:50:17.647 INFO : Debug Log(user): AUTH0_J =a5a5a5aa mar 3/09:50:17.647 INFO : Debug Log(user): AUTH1_J =a5a5a5a5 mar 3/09:50:17.647 INFO : Debug Log(user): AUTH2_J =f0f0f0f mar 3/09:50:17.647 INFO : Debug Log(user): AUTH3_J =f0f0f0f mar 3/09:50:17.647 DEBUG2 : ) = 0 mar 3/09:50:17.652 INFO : Debug Log(info): CPU status - IN RESET mar 3/09:50:17.863 INFO : Debug Log(info): Processor did not stop on hardware reset. mar 3/09:50:17.863 INFO : Processor did not stop on hardware reset. mar 3/09:50:17.863 DEBUG2 : LowLevelReset(): Core 0: CpuStatus(status = <0x3: CPU_STATUS_MPOWER | CPU_STATUS_MRUN>) = 0 mar 3/09:50:17.863 INFO : Debug Log(minor): CPU status OK mar 3/09:50:17.863 DEBUG2 : Core 0: WaitForCpuResetToComplete(): CpuStop() mar 3/09:50:17.865 DEBUG2 : -> WaitForCpuToStop(core 0) mar 3/09:50:17.878 DEBUG2 : LowLevelReset(): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:17.878 DEBUG2 : <- WaitForCpuToStop(core 0) mar 3/09:50:17.878 DEBUG2 : <- LowLevelReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:17.879 DEBUG2 : ISigPcSampler::GetSample(SIGAPIARM_SAMPLE_CYCLE) = 0x0 mar 3/09:50:17.879 DEBUG2 : <- LowLevelReset(hardware, delay 200) mar 3/09:50:17.879 DEBUG2 : -> StartSession(): WaitForCpuResetToComplete(core 0) mar 3/09:50:17.880 DEBUG2 : StartSession(): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:17.880 DEBUG2 : <- StartSession(): WaitForCpuResetToComplete(core 0) mar 3/09:50:17.881 DEBUG2 : StartSession() checking powerCore 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:17.881 DEBUG2 : Core 0: IceInfo(0, ...) mar 3/09:50:17.884 DEBUG2 : LowLevelReset(1) mar 3/09:50:18.108 DEBUG2 : -> LowLevelReset(software, delay 200) mar 3/09:50:18.108 INFO : Debug Log(info): LowLevelReset(software, delay 200) mar 3/09:50:18.108 DEBUG2 : core 0: IsigEmu::ParamSet('JtagInitDelay', '200,r:300') mar 3/09:50:18.109 DEBUG2 : LowLevelSoftwareReset(): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:18.109 DEBUG2 : core 0: IsigEmu::ParamSet('ResetStyle', 'SOFTWARE') mar 3/09:50:18.109 DEBUG2 : Core 0: LowLevelSoftwareReset() mar 3/09:50:18.434 DEBUG2 : -> LowLevelSoftwareReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:18.444 DEBUG2 : LowLevelSoftwareReset(): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:18.444 DEBUG2 : <- LowLevelSoftwareReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:18.649 DEBUG2 : -> LowLevelReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:18.650 DEBUG2 : LowLevelReset(): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:50:18.650 DEBUG2 : <- LowLevelReset(): WaitForCpuResetToComplete(core 0) mar 3/09:50:18.651 DEBUG2 : ISigPcSampler::GetSample(SIGAPIARM_SAMPLE_CYCLE) = 0x0 mar 3/09:50:18.651 DEBUG2 : <- LowLevelReset(software, delay 200) mar 3/09:50:18.651 DEBUG2 : <- LowLevelReset(1) mar 3/09:50:18.651 DEBUG2 : CpuRegSet(Core 0, CPSR ->16) = 0x1da (474) mar 3/09:50:18.651 DEBUG2 : Write reg 1 of 1: PC[0x1f0] = 0x102000 (1056768) mar 3/09:50:18.651 DEBUG2 : CpuRegSet(Core 0, 15, 1056768) mar 3/09:50:18.651 DEBUG2 : CpuRegGet(Core 0, CPSR -> 16) = 0x1da (474) mar 3/09:50:18.651 DEBUG2 : Write reg 1 of 1: CPSR[0xa4] = 0x1da (474) mar 3/09:50:18.651 DEBUG2 : CpuRegSet(Core 0, 16, 474) mar 3/09:50:18.651 INFO : Debug Log(info): Target reset mar 3/09:50:18.651 DEBUG2 : , 1 units, 'Stack window trigger') mar 3/09:50:18.653 DEBUG2 : SetCodeBreak(): BreakSetAttr(bank 0, count 1, addr 0x4e8, attr <0x2000d: CPUMODE(THUMB) | SIGEMU_BRK_ATTR_SET | SIGEMU_BRK_ATTR_SW | SIGEMU_BRK_ATTR_HW>) mar 3/09:50:18.659 DEBUG2 : SetBreakpoint(): BreakGetAttr(bank 0, count 1, addr 0x4e8, attr <0x20405: CPUMODE(THUMB) | SIGEMU_BRK_ATTR_SET | SIGEMU_BRK_ATTR_SW | SIGEMU_BRK_ATTR_LITTLEENDIAN>) mar 3/09:50:18.662 DEBUG2 : -> SetupTrace() mar 3/09:50:18.662 DEBUG2 : -> AcquireXTrace() mar 3/09:50:18.662 DEBUG2 : ISigProbe::AcquireInterface('ISigXTrace') mar 3/09:50:18.662 DEBUG2 : ISigAPI::CreateInstance('ISigXTrace') mar 3/09:50:18.688 DEBUG2 : <- AcquireXTrace() mar 3/09:50:18.688 DEBUG2 : ISigXTrace::LinkAttach('SigTerminalLog',...) mar 3/09:50:18.688 DEBUG2 : ISigXTrace::LinkAttach('ISigXTraceClient',...) mar 3/09:50:18.688 DEBUG2 : ISigXTrace::LinkAttach('SigEmu',...) mar 3/09:50:18.688 DEBUG2 : ISigXTrace::LinkAttach('SigProbe',...) mar 3/09:50:18.688 INFO : Debug Log(user): DMAC:execPreConfigureTrace() mar 3/09:50:18.688 DEBUG2 : ISigCmdInterpreter::Execute('trace -opt +ETB,baseetb=0x80010001') mar 3/09:50:18.688 DEBUG2 : ISigCmdInterpreter::Execute('trace -mode 0x6') mar 3/09:50:18.689 DEBUG2 : -> SetupLowLevelTrace() mar 3/09:50:18.689 DEBUG2 : ISigXTrace::Init('SWO,ETB') mar 3/09:50:18.714 INFO : Debug Log(info): INFO: Configuring trace using 'Auto,size_limit=100%,ETB,baseetb=0x80010001' setting, mode=0x6... mar 3/09:50:18.714 INFO : INFO: Configuring trace using 'Auto,size_limit=100%,ETB,baseetb=0x80010001' setting, mode=0x6... mar 3/09:50:18.716 INFO : Debug Log(info): Trace: Using ETMv4 at address 0x80440000 mar 3/09:50:18.716 INFO : Trace: Using ETMv4 at address 0x80440000 mar 3/09:50:18.716 INFO : Debug Log(info): Trace: ETMv4 is already powered-up (TRCPDSR=0x23) mar 3/09:50:18.716 INFO : Trace: ETMv4 is already powered-up (TRCPDSR=0x23) mar 3/09:50:18.719 INFO : Debug Log(info): Trace: Using ETF at address 0x80010000, RAM size 0x1000 words (16KB) mar 3/09:50:18.719 INFO : Trace: Using ETF at address 0x80010000, RAM size 0x1000 words (16KB) mar 3/09:50:18.745 INFO : Debug Log(info): Trace: Configured as 'ETMv4 to ETB' (SW ver: Trace2=1.38 ETM=1.02 ETB=1.05 Deco=1.43) mar 3/09:50:18.745 DEBUG2 : <- SetupLowLevelTrace() mar 3/09:50:18.745 DEBUG2 : -> AcquireSWOInterface() mar 3/09:50:18.745 DEBUG2 : ISigProbe::AcquireInterface('ISigSWO') mar 3/09:50:18.745 DEBUG2 : ISigSWO::LinkAttach('SigEmu',...) mar 3/09:50:18.745 DEBUG2 : ISigSWO::LinkAttach('SigTerminalLog',...) mar 3/09:50:18.745 DEBUG2 : ISigSWO::Init('') mar 3/0918.745 ERROR : ISigSWO::Init() failed mar 3/0918.746 DEBUG2 : <- AcquireSWOInterface() mar 3/0918.746 DEBUG2 : -> CreateSigChanInterface() mar 3/0918.746 DEBUG2 : ISigProbe::AcquireInterface('ISigChan') mar 3/09:50:18.746 DEBUG2 : <- CreateSigChanInterface() mar 3/09:50:18.746 DEBUG2 : -> SetupSigChanInterface() mar 3/09:50:18.746 DEBUG2 : ISigChan::LinkAttach('SigEmu',...) mar 3/09:50:18.746 DEBUG2 : ISigChan::LinkAttach('SigTerminalLog',...) mar 3/09:50:18.746 DEBUG2 : ISigChan::LinkAttach('SigXTrace',...) mar 3/09:50:18.746 DEBUG2 : ISigChan::Init('null') mar 3/09:50:18.746 DEBUG2 : ISigChan::AcquireInterface('ISigChanReader') mar 3/09:50:18.746 DEBUG2 : ISigChanReader::GotoBegin() mar 3/09:50:18.746 DEBUG2 : <- SetupSigChanInterface() mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm portsize=4') -> This trace does not allow to define capture width mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm halfrate=off') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm portmode=1:1') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm data=none') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('ctrl stop=cpustop') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm stall=off') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm pc=all') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigXTrace::ExecuteCmd('etm update') -> Ok mar 3/09:50:18.748 DEBUG2 : ISigA2d::ChanCnt(0) = 1 mar 3/09:50:18.749 DEBUG2 : ISigA2d::ChanName(0) = ITrgPwr mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanAttr(0) = 311a1 mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanUnit(0) = 1 mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanMax(0) = 700000 mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanOffset(0) = 0 mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanOffset(0) = 12 mar 3/09:50:18.749 DEBUG2 : ISigA2D::ChanID(0) = 0x200 mar 3/09:50:18.750 DEBUG2 : ISigA2D::StreamAdd(0) = -5 [TdJetPower::SendLogsForId(0)] mar 3/09:50:18.750 INFO : Debug Log(warning): Could not measure 'ITrgPwr' when ETM/ETB mode is active. mar 3/09:50:18.750 DEBUG2 : ISigA2D::StreamEnumFreq(0,0) = 200000 mar 3/09:50:18.750 DEBUG2 : <- SetupTrace() mar 3/09:50:18.750 DEBUG2 : -> SetupProfiling() mar 3/09:50:18.751 DEBUG2 : <- SetupProfiling() mar 3/09:50:18.752 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c0, 4 bytes [by 4] = [ 00 20 13 41 ]) mar 3/09:50:18.752 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.752 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.754 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.754 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.755 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.755 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 01 00 00 00 ]) mar 3/09:50:18.757 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.757 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.758 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 01 00 00 00 ]) mar 3/09:50:18.758 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 02 00 00 00 ]) mar 3/09:50:18.760 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.760 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.761 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 02 00 00 00 ]) mar 3/09:50:18.761 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c5, 4 bytes [by 4] = [ 03 00 00 00 ]) mar 3/09:50:18.762 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.762 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090d1, 4 bytes [by 4] = [ 00 00 00 00 ]) mar 3/09:50:18.762 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c3, 4 bytes [by 4] = [ 00 00 00 80 ]) mar 3/09:50:18.764 DEBUG2 : ReadPostCache(): MemRead(core 0, 31:0x100090c0, 4 bytes [by 4] = [ 00 20 13 41 ]) mar 3/09:50:18.764 DEBUG2 : WritePostCache(): MemWrite(core 0, 31:0x100090c0, 4 bytes [by 4] = [ 04 20 13 41 ]) mar 3/09:50:18.766 DEBUG2 : SetCodeBreak(<0:0x8>, 1 units, 'C-SPY Terminal I/O && library support module') mar 3/09:50:18.766 DEBUG2 : SetCodeBreak(): BreakSetAttr(bank 0, count 1, addr 0x8, attr <0x1000d: CPUMODE(ARM) | SIGEMU_BRK_ATTR_SET | SIGEMU_BRK_ATTR_SW | SIGEMU_BRK_ATTR_HW>) mar 3/09:50:18.772 DEBUG2 : SetBreakpoint(): BreakGetAttr(bank 0, count 1, addr 0x8, attr <0x10405: CPUMODE(ARM) | SIGEMU_BRK_ATTR_SET | SIGEMU_BRK_ATTR_SW | SIGEMU_BRK_ATTR_LITTLEENDIAN>) mar 3/09:50:18.772 DEBUG2 : LowLevelGo(core 0) mar 3/09:50:18.795 DEBUG2 : CpuRegGet(Core 0, PC ->15) = 0x102000 (1056768) mar 3/09:50:18.795 DEBUG2 : CpuRegGet(Core 0, CPSR ->16) = 0x1da (474) mar 3/09:50:18.796 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x102000, 4 bytes [by 4] = [ 20 20 20 20 ]) mar 3/09:50:18.796 ERROR : MemRead() returned Failure while executing the operation ; ReadPostCache(): mar 3/09:50:18.796 DEBUG2 : ) = 0 mar 3/09:50:18.797 DEBUG2 : Core 0: LowLevelGo(core 0) [multi = false], CpuGo() mar 3/09:50:18.822 DEBUG2 : CpuRegGet(Core 0, PC -> 15) = 0x4e8 (1256) mar 3/09:50:18.822 DEBUG2 : LowLevelGo(core 0): errNo == ERR_OK, cpu status = not running, not sleeping, cpu power = 1 --> Exit LowLevelGo loop mar 3/09:50:18.822 DEBUG2 : LowLevelGo(core 0): Setting single mIsExecuting[0] = false [multi == false] mar 3/09:50:18.822 DEBUG2 : LowLevelGo(core 0): CPU core 0 is now stopped, after 2 polls in 0.001s mar 3/09:50:18.822 DEBUG2 : ok mar 3/09:50:18.836 DEBUG2 : ISigChan::Stop() mar 3/09:50:18.837 DEBUG2 : GetStopBreaks(): BreakGetAttr(bank 0, count 1, addr 0x4e8, attr <0x20405: CPUMODE(THUMB) | SIGEMU_BRK_ATTR_SET | SIGEMU_BRK_ATTR_SW | SIGEMU_BRK_ATTR_LITTLEENDIAN>) mar 3/09:50:18.837 DEBUG2 : LowLevelGo(core 0): Stopped at breakpoint mar 3/09:50:18.837 DEBUG2 : <- LowLevelGo(core 0) mar 3/09:50:18.837 DEBUG2 : PlDriver::Go(core 0): goStatus = 0 mar 3/09:50:18.839 DEBUG2 : ISigPcSampler::GetSample(SIGAPIARM_SAMPLE_CYCLE) = 0x0 mar 3/09:50:18.839 DEBUG2 : ClearCodeBreak(<0:0x4e8>, 1 units) mar 3/09:50:18.839 DEBUG2 : ClearCodeBreak(): BreakClr(bank 0, count 1, addr 0x4e8) mar 3/09:50:18.900 DEBUG2 : CpuRegGet(Core 0, CPSR -> 16) = 0x1f3 (499) mar 3/09:50:18.905 DEBUG2 : CpuRegGet(Core 0, SVR_SP -> 30) = 0x106f98 (1077144) mar 3/09:50:18.905 DEBUG2 : CpuRegGet(Core 0, SVR_LR -> 31) = 0x1023f8 (1057784) mar 3/09:50:52.920 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x400, 512 bytes [by 0] = [ 08 00 00 00 00 13 00 00 ... ]) mar 3/09:50:53.609 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040000, 512 bytes [by 0] = [ 00 00 00 00 54 52 4f 50 ... ]) mar 3/09:52:52.553 DEBUG2 : PlDriver::Go(core 0): mIsExecuting[0] = true mar 3/09:52:52.553 DEBUG2 : -> LowLevelGo(core 0) mar 3/09:52:52.553 DEBUG2 : CpuRegGet(Core 0, PC ->15) = 0x4e8 (1256) mar 3/09:52:52.553 DEBUG2 : CpuRegGet(Core 0, CPSR ->16) = 0x1f3 (499) mar 3/09:52:52.553 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x4e8, 2 bytes [by 2] = [ f3 01 ]) mar 3/09:52:52.553 ERROR : MemRead() returned Failure while executing the operation ; ReadPostCache(): mar 3/09:52:52.553 DEBUG2 : ) = 0 mar 3/09:52:52.554 DEBUG2 : Core 0: LowLevelGo(core 0) [multi = false], CpuGo() mar 3/09:52:54.107 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ 7e a6 4b 02 ]) mar 3/09:52:55.661 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ 3c 7d 9c 04 ]) mar 3/09:52:57.200 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ 12 cc e7 06 ]) mar 3/09:52:58.763 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ 31 a2 3b 09 ]) mar 3/09:53:00.298 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ c0 57 85 0b ]) mar 3/09:53:01.845 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ c0 bb d3 0d ]) mar 3/09:53:03.381 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040010, 4 bytes [by 4] = [ ae 3f 1d 10 ]) mar 3/09:53:04.511 DEBUG2 : LowLevelStop(0): mStoppedByLowLevelStop[0] = true mar 3/09:53:04.512 DEBUG2 : LowLevelGo(core 0): Stop requested by stop flag mar 3/09:53:04.512 DEBUG2 : Core 0: LowLevelGo(core 0) [multi = false]: ISigEmu::CpuStop() mar 3/09:53:04.513 DEBUG2 : -> WaitForCpuToStop(core 0) mar 3/09:53:04.525 DEBUG2 : LowLevelGo(core 0): Core 0: CpuStatus(status = <0x1: CPU_STATUS_MPOWER>) = 0 mar 3/09:53:04.525 DEBUG2 : <- WaitForCpuToStop(core 0) mar 3/09:53:04.525 DEBUG2 : LowLevelGo(core 0): WaitForCpuToStop(0) returned waitRes = 0 mar 3/09:53:04.526 DEBUG2 : LowLevelGo(core 0): Setting single mIsExecuting[0] = false [multi == false] mar 3/09:53:04.526 DEBUG2 : LowLevelGo(core 0): CPU core 0 is now stopped, after 1670 polls in 11.945s mar 3/09:53:04.526 DEBUG2 : ok mar 3/09:53:04.528 DEBUG2 : ISigChan::Stop() mar 3/09:53:04.528 DEBUG2 : CpuRegGet(Core 0, PC -> 15) = 0x4ea (1258) mar 3/09:53:04.529 DEBUG2 : LowLevelGo(core 0): Stopped at breakpoint mar 3/09:53:04.529 DEBUG2 : <- LowLevelGo(core 0) mar 3/09:53:04.529 DEBUG2 : PlDriver::Go(core 0): goStatus = 1 mar 3/09:53:04.530 DEBUG2 : ISigPcSampler::GetSample(SIGAPIARM_SAMPLE_CYCLE) = 0x0 mar 3/09:53:04.588 DEBUG2 : CpuRegGet(Core 0, CPSR -> 16) = 0x1f3 (499) mar 3/09:53:04.591 DEBUG2 : CpuRegGet(Core 0, SVR_SP -> 30) = 0x106f98 (1077144) mar 3/09:53:04.591 DEBUG2 : CpuRegGet(Core 0, SVR_LR -> 31) = 0x1023f8 (1057784) mar 3/09:53:04.608 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x400, 512 bytes [by 0] = [ 08 00 00 00 00 13 00 00 ... ]) mar 3/09:53:04.615 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x600, 512 bytes [by 0] = [ 00 00 00 10 00 00 00 00 ... ]) mar 3/09:53:04.637 DEBUG2 : ReadPostCache(): MemRead(core 0, 0:0x10040000, 512 bytes [by 0] = [ 00 00 00 00 54 52 4f 50 ... ]) mar 3/09:53:08.719 DEBUG2 : -> AboutToStopSession() mar 3/09:53:08.733 DEBUG2 : Exiting SWO reading thread mar 3/09:53:08.734 DEBUG2 : <- AboutToStopSession() mar 3/09:53:08.742 DEBUG2 : PrepareStopSession() mar 3/09:53:09.383 DEBUG2 : <- PrepareStopSession() mar 3/09:53:09.383 DEBUG2 : ClearCodeBreak(<0:0x8>, 1 units) mar 3/09:53:09.383 DEBUG2 : ClearCodeBreak(): BreakClr(bank 0, count 1, addr 0x8) mar 3/09:53:09.394 DEBUG2 : StopGui() mar 3/09:53:09.442 DEBUG2 : -> StopSession() mar 3/09:53:09.497 DEBUG2 : -> TerminateHardware() mar 3/09:53:09.497 DEBUG2 : ISigXTrace::Term() mar 3/09:53:09.497 DEBUG2 : ISigEmu::ReleaseInterface(pcSampler) mar 3/09:53:09.497 DEBUG2 : ISigEmu::ReleaseInterface(sigWpt) mar 3/09:53:09.497 DEBUG2 : ISigEmu::ReleaseInterface(sigVect) mar 3/09:53:09.498 DEBUG2 : ISigEmu::IceTerm() mar 3/09:53:09.510 DEBUG2 : ISigChan::ReleaseInterface(chanReader) mar 3/09:53:09.510 DEBUG2 : ISigChan::Term() mar 3/09:53:09.510 DEBUG2 : ISigXTrace::Term() mar 3/09:53:09.510 DEBUG2 : ISigAPI::ReleaseInstance(sigXTrace) mar 3/09:53:09.510 DEBUG2 : ISigA2D::Term() mar 3/09:53:09.510 DEBUG2 : ISigProbe::ReleaseInterface(sigA2D) mar 3/09:53:09.510 DEBUG2 : Core 0: sigEmu->LinkAttach(ISigProbe) mar 3/09:53:09.510 DEBUG2 : ISigApi::ReleaseInstance(sigEmu) mar 3/09:53:09.522 DEBUG2 : SigAPITerm() mar 3/09:53:09.523 DEBUG2 : <- TerminateHardware() mar 3/09:53:09.523 DEBUG2 : <- StopSession() mar 3/09:53:09.523 DEBUG2 : -> ~TdJetDriver() mar 3/09:53:09.523 DEBUG2 : -> TerminateHardware() mar 3/09:53:09.523 DEBUG2 : <- TerminateHardware()

提示

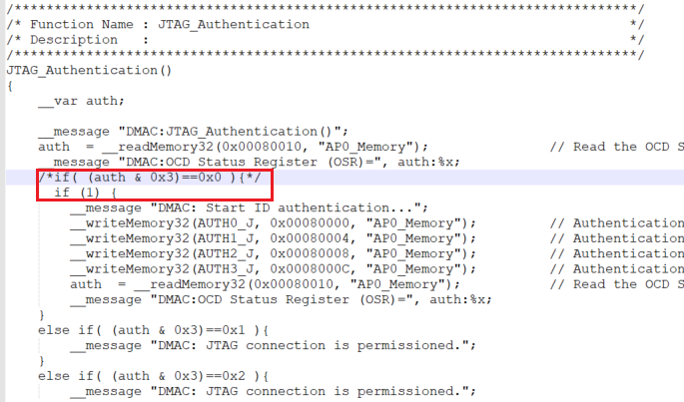

在烧写OTP之前,先修改DMAC文件,如下第一张图所示,测试如下第二张图所示的身份验证过程。

*开始测试之前,先看一下“EWARM_IjetConnectMacros.pdf ”,只有5页。完成测试后,请务必将dmac文件改回!

使用注意事项

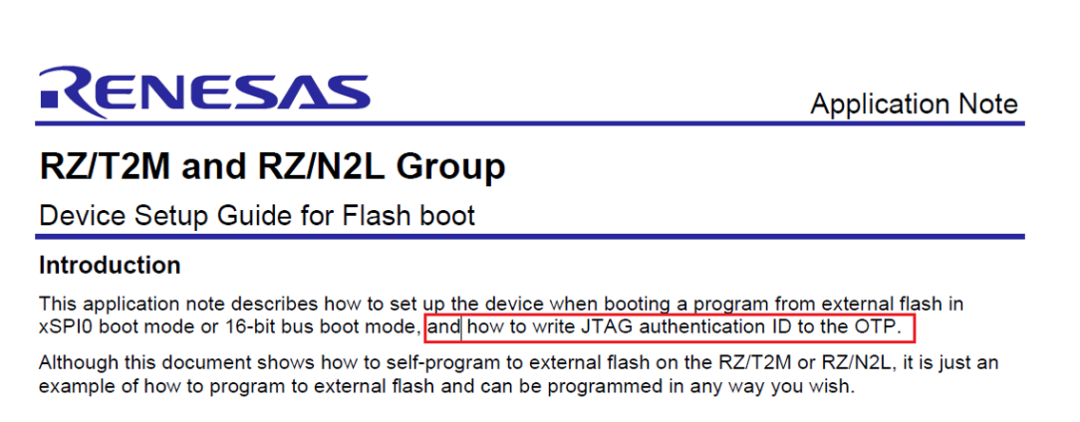

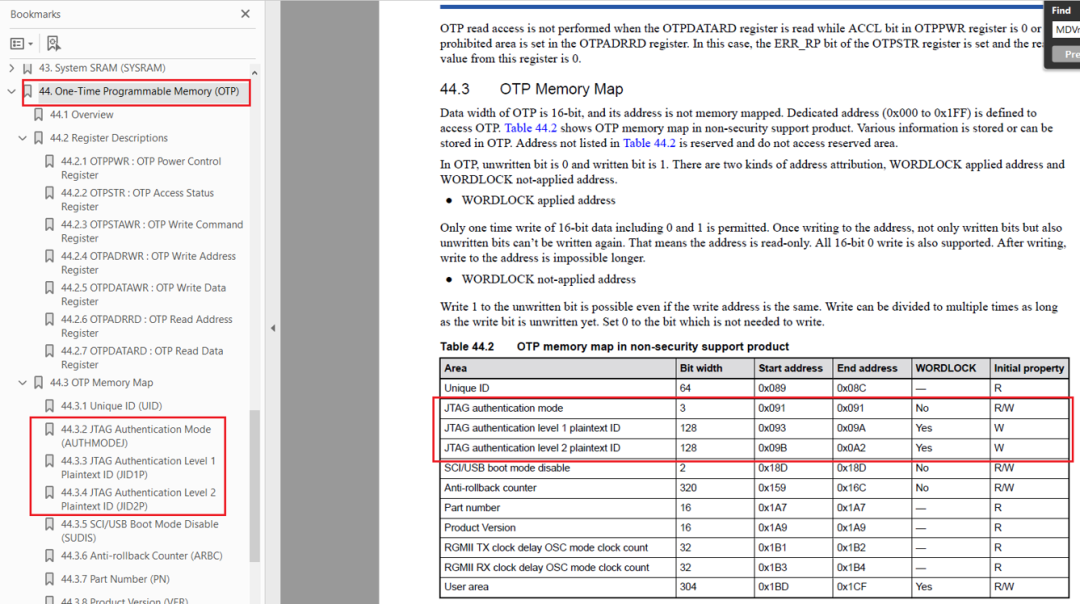

在JATG认证之前,请根据OTP应用注释“r01an6471ej0110”正确地将JTAG认证ID写入OTP

请参阅硬件用户手册来访问一次性可编程存储器

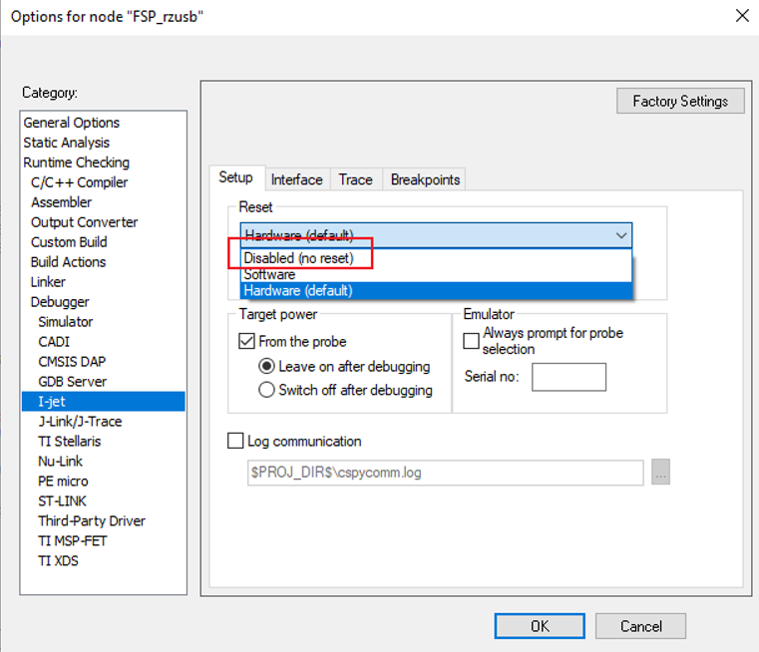

关掉I-jet的复位功能

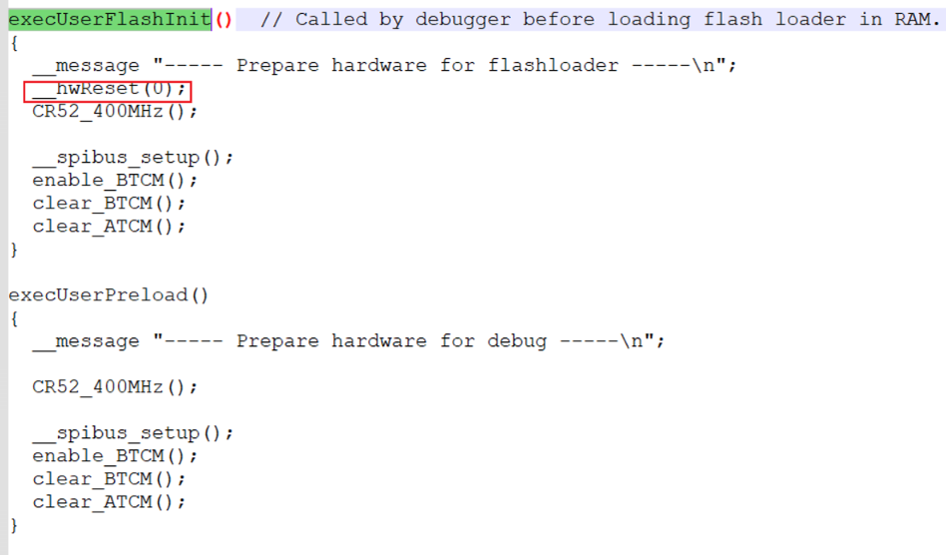

屏蔽Flashloader脚本的复位函数调用

审核编辑:刘清

-

编码器

+关注

关注

45文章

3715浏览量

135910 -

以太网

+关注

关注

40文章

5499浏览量

173402 -

JTAG

+关注

关注

6文章

403浏览量

72187 -

伺服系统

+关注

关注

14文章

578浏览量

39549 -

工业电机

+关注

关注

0文章

99浏览量

15827

原文标题:RZ/T2M和RZ/N2L的I-jet JTAG认证

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RZ/T2M 组 RZ/T2M Motor Solution Kit Startup 手册(for RZ/T2M Motion Control Utility)

RZ/T2M 组 RZ/T2M Motor Solution Board 硬件手册

RZ/T2M 组 RZ/T2M Motor Solution Board 硬件手册

RZ/T2M, RZ/T2L, RZ/N2L电机解决方案套件数据手册

瑞萨RZ/T2M和RZ/N2L的I-jet JTAG认证

瑞萨RZ/T2M和RZ/N2L的I-jet JTAG认证

评论