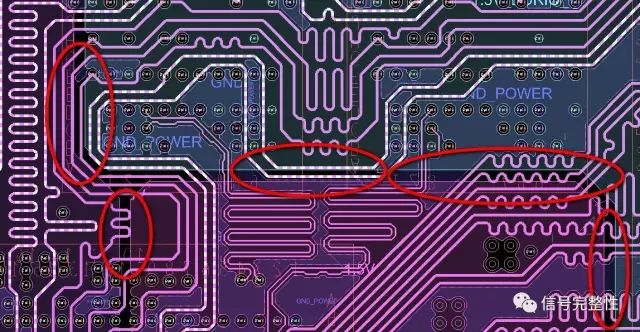

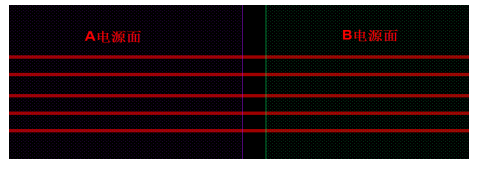

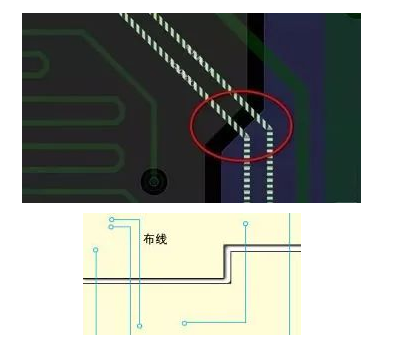

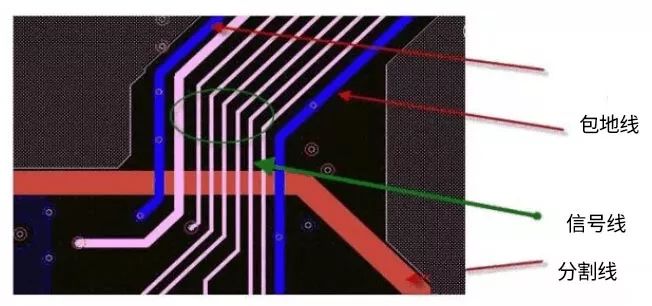

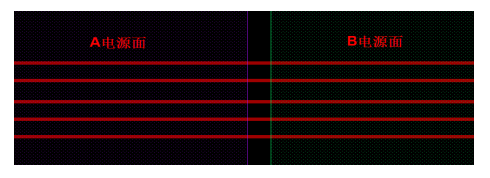

在PCB设计过程中经常会遇到高多层、高密度的设计,那么这种情况下就难免出现跨分割的情况,如下图所示:

这是一个HDI的项目,非常的密集,很多点都会出现跨分割,在设计之初,针对DDR3,经过仿真之后,觉得问题不大,所以设计工程师和我交流的时候,告诉他没有问题,结果一拿过来review的时候,傻眼。这哪是跨分割,简直就是分割嘛。来回在gap上绕线或者差分线有一根单线直接布在gap上,十有八九会造成问题,不是SI的问题,就有可能造成PI的问题,或者EMI的问题。

因为跨分割本身就会造成阻抗的不连续,阻抗不连续就会造成反射,反射过大就有可能造成辐射或者干扰,进而SSN、串扰、EMI,等等问题就有可能接踵而至。

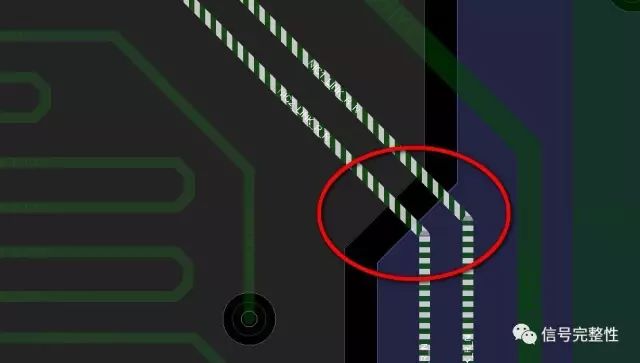

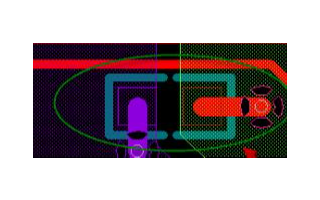

那么,如果信号一定要跨分割怎么办呢?其实这个也没有一个非常好的办法,只能说是“坏中选优”。比如:最短的距离跨分割、不要在gap上绕线:

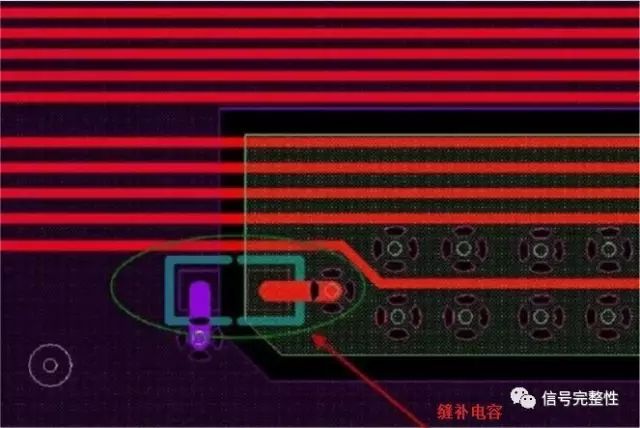

另外,缝补电容也是常用的一种手段,即为跨分割的信号提供较短的回流路径。通常在信号跨分割处摆放一个 0201 或者 0402大小的瓷片电容,电容的容值在 0.01uF 或者是 0.1 uF,这个参数并不是一成不变的,需要根据信号的频率的变化而改变。

当然,在低速的时候,在EMI的处理方法上,还可以利用跨接的方式,即在信号线经过gap的区域加一颗0ohm的电阻。

审核编辑:刘清

-

DDR3

+关注

关注

2文章

290浏览量

44296 -

emi

+关注

关注

54文章

3921浏览量

136160 -

PCB设计

+关注

关注

396文章

4944浏览量

96028 -

信号线

+关注

关注

2文章

189浏览量

22297 -

瓷片电容

+关注

关注

0文章

84浏览量

15364

原文标题:在高速电路设计中,如何应对PCB设计中信号线的跨分割

文章出处:【微信号:SI_PI_EMC,微信公众号:信号完整性】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB中的平面跨分割

什么是ICT测试点 PCB设计信号线跨分割的影响

PCB设计工程师一定要了解的“跨分割”

如何处理PCB设计中“跨分割”问题

为什么高速PCB设计中信号线不能多次换孔

PCB信号跨分割线需要怎么处理?

如何应对PCB设计中信号线的跨分割呢?

如何应对PCB设计中信号线的跨分割呢?

评论