所谓设计复用,就是在电子电路设计中将已有的、经过验证的设计功能模块,形成专有的、可在不同的电子产品中重复使用的IP,将这部分IP以原理图和PCB板图形式应用于新的设计中,以提高设计效率和可靠性。接下来我们将向大家演示Cadence SPB 23.1版本下进行Design Reuse Module创建流程。

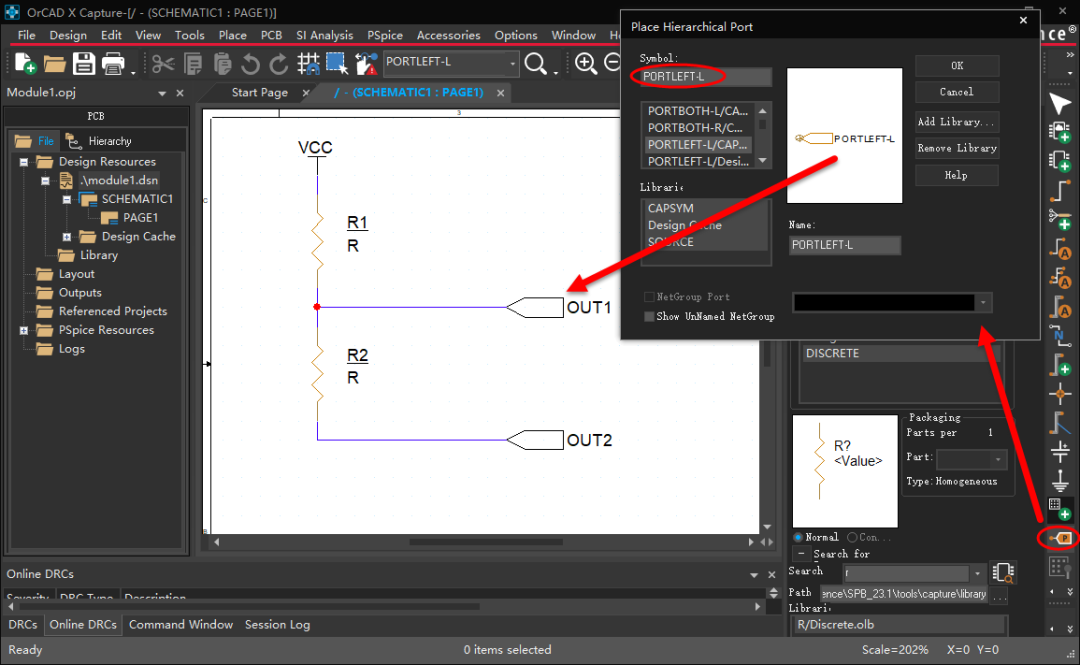

01首先,打开经过验证的设计功能模块的原理图,并为所有需要与外部信号连接的网络添加HierarchicalPort,如果在功能模块中,有全局变量,如VCC符号,可以不用添加HierarchicalPort。但是如果该功能模块的全局变量VCC,在不同的设计中调用时,需要与外部的不同全局变量进行连接时,功能模块中全局变量VCC就不能使用VCC符号进行绘制原理图,需要删除VCC符号,添加HierarchicalPort,定义局部变量名为VCC。

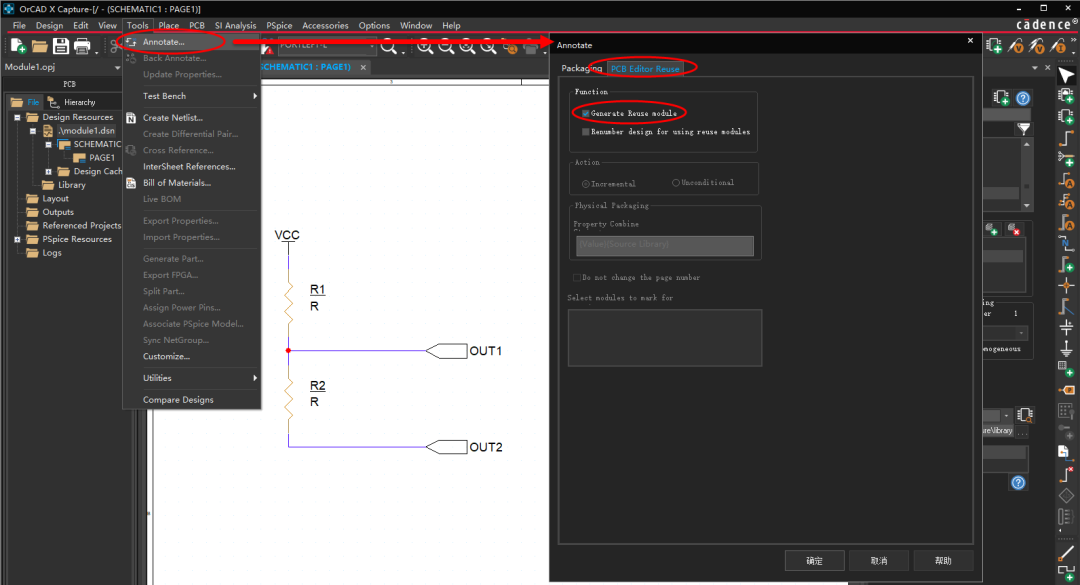

02在产生网表文件前,需要先定义该设计功能模块的原理图为Reuse Module属性。点击Tools—Annotate,选择PCB Editor Reuse,勾选Generate Reuse module,点击确定,为设计功能模块生成复用属性。

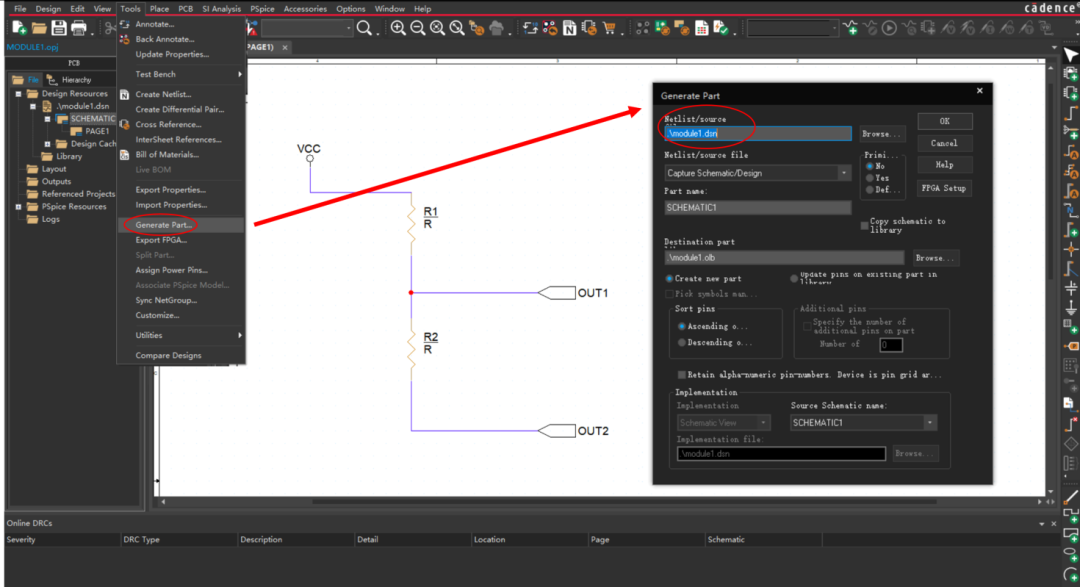

03在已经定义了Reuse Module属性的原理图下,为原理图生成可复用的IP。点击Tools—Generate Part,浏览到源文件下的设计文件module1.dsn,确保未勾选Copy schematic to library。点击OK创建可复用的IP。

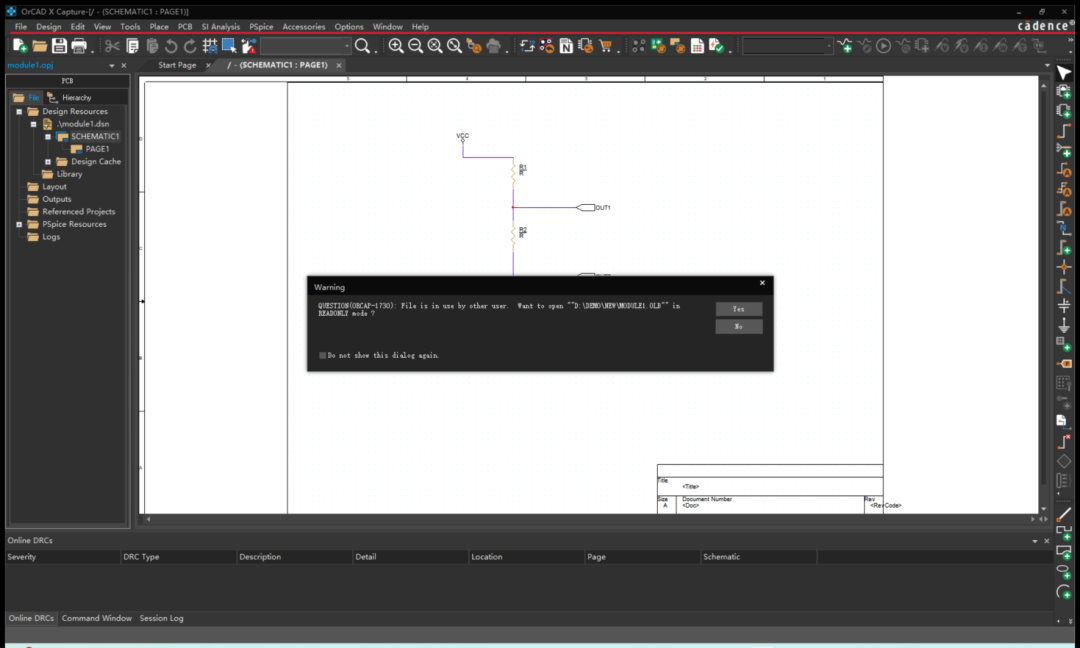

软件会提示我们,复用的IP将被其他使用者使用,会为这个模块创建一个.OLB文件来保存。点击yes。

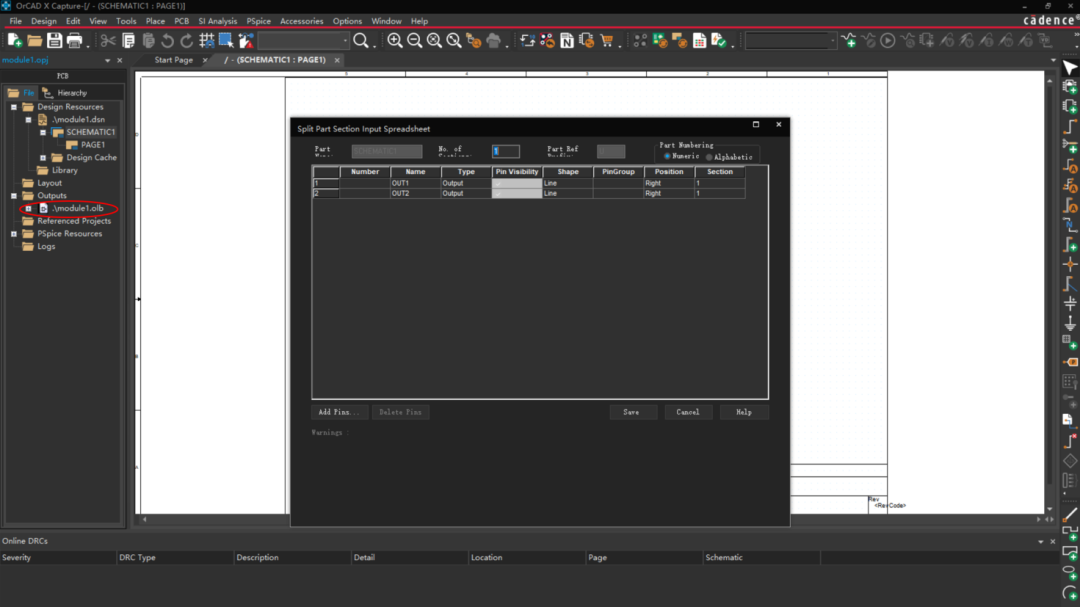

04复用的IP输出了两个外部信号连接的网络,分别是OUT1和OUT2,点击Save进行保存。

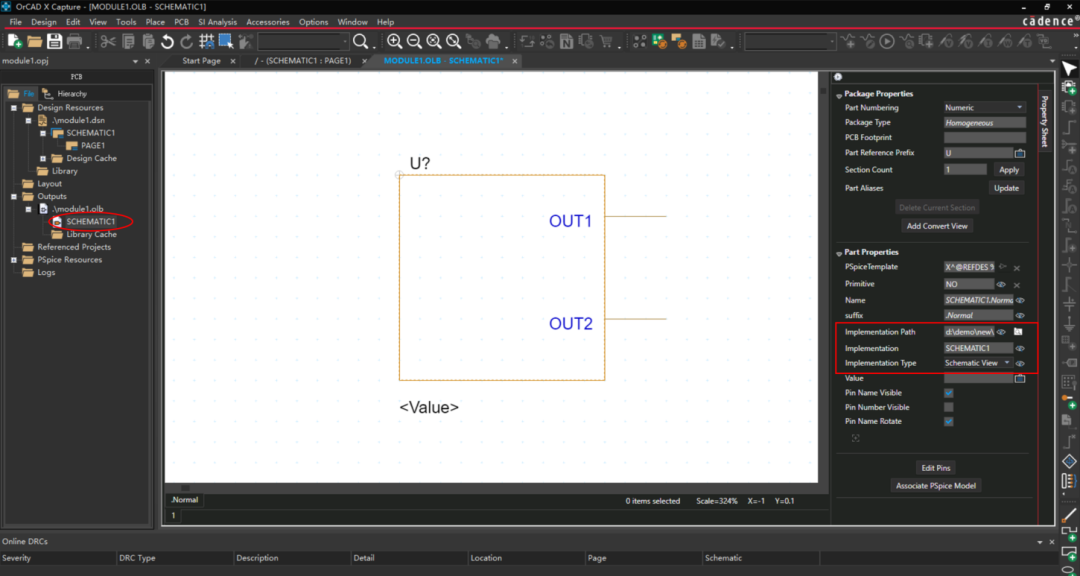

05双击左侧Output—module—SCHEMATIC1。观察到原理图就整合为一个symbol模块,在后续使用的时候直接调用这个库文件。在右侧栏Part Properties查看复用的symbol属性。

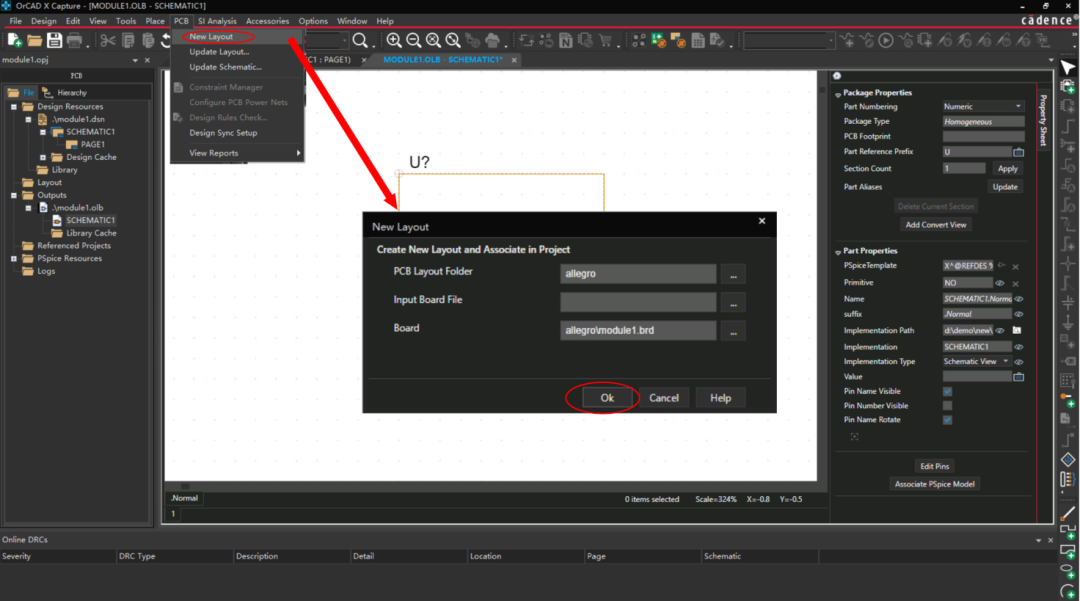

06为PCB板图创建可复用的IP。点击PCB—New Layout,在弹出的框中点击OK按钮。

07

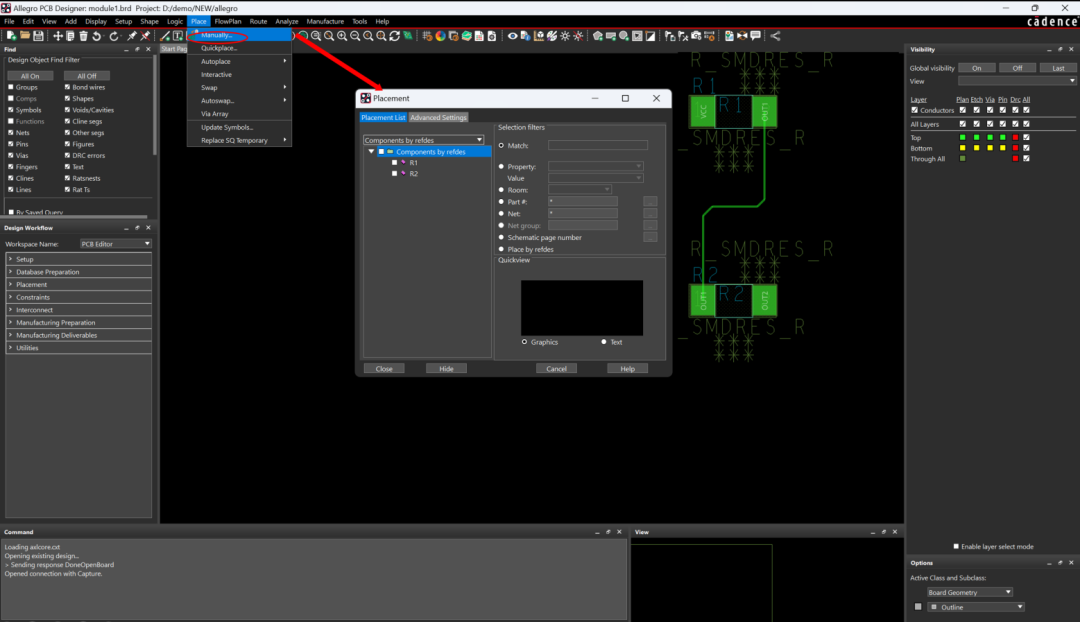

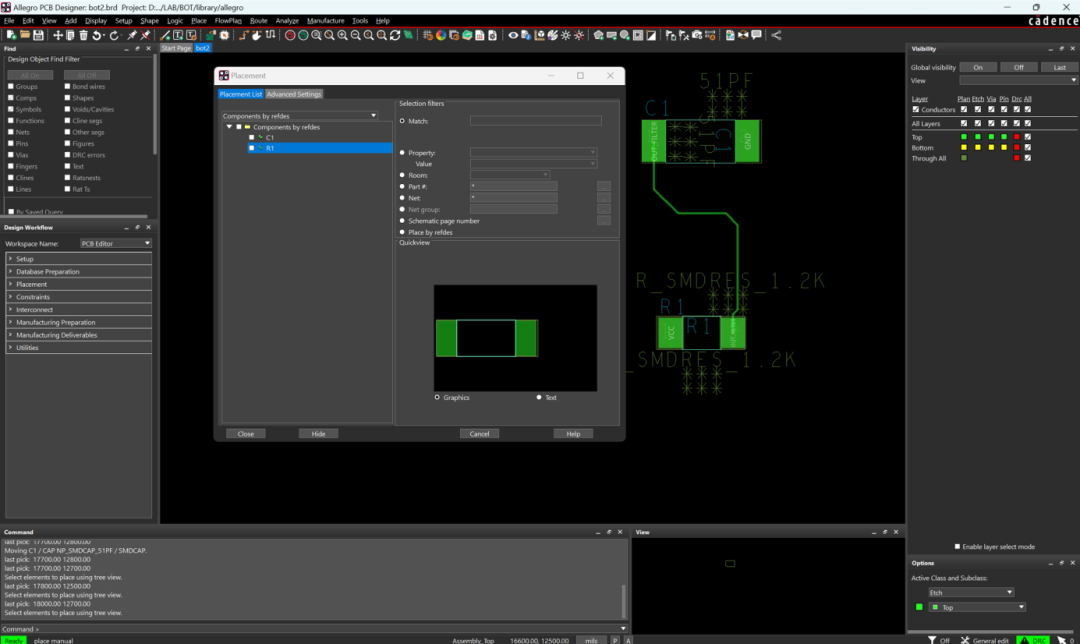

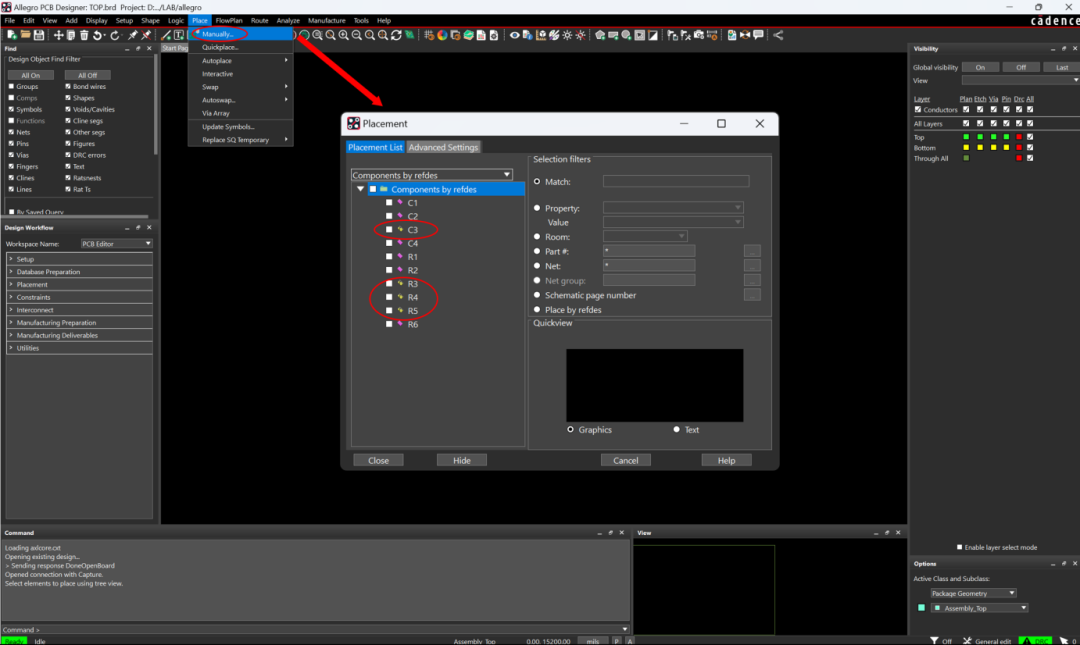

接下来进入Allegro界面,进行复用模块的创建。点击Place—Manually,在Placement List—Components by refdes选择放置的元器件并进行连线。

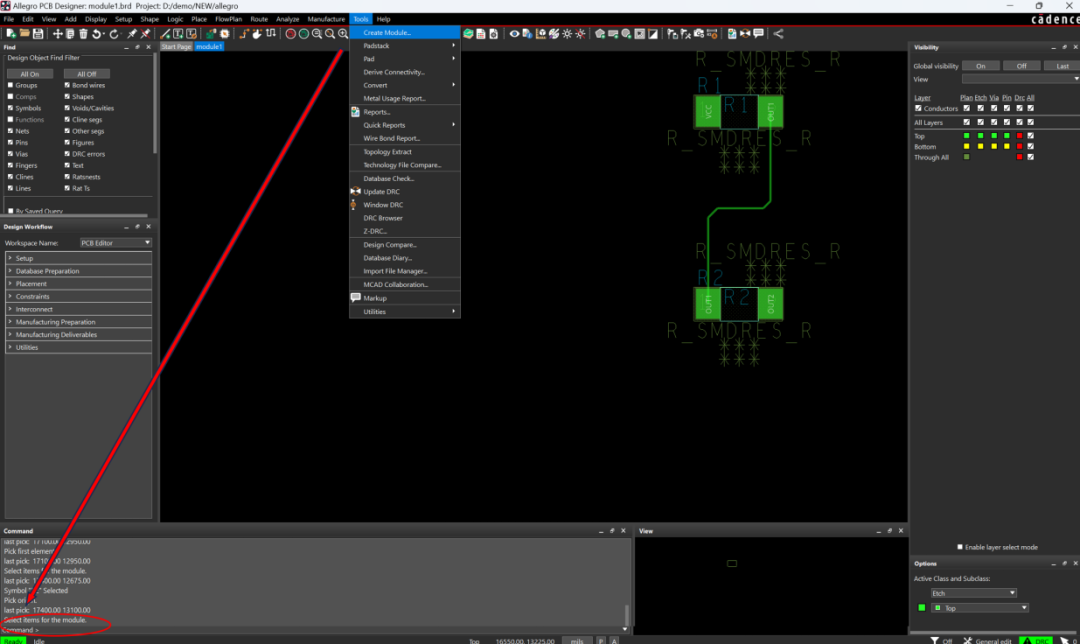

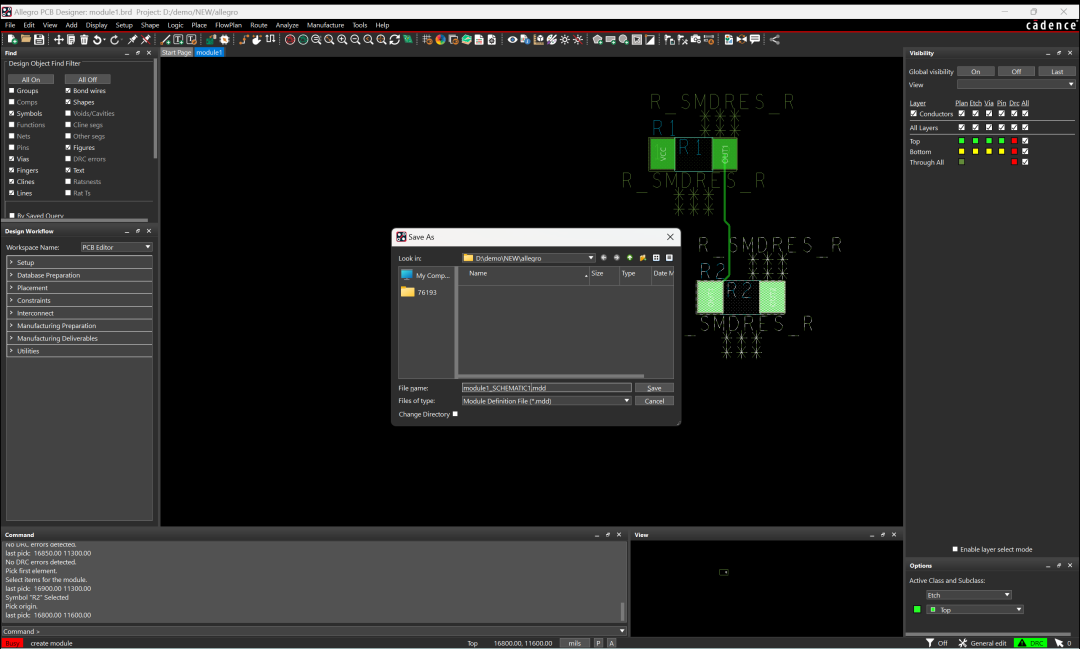

08选择Tools→Creat Module,然后命令框就会提示你选择组件,选好后,在选中区域点击,定义.mdd文件的原点。再保存mdd文件。

这里的命名必须是特定格式<花样命名>_.mdd。并将它保存在Allegro文件中。

09第二个Symbol的建立,与上述步骤相同,新建一个PCB板,点击Place—Manually,在Placement界面,选择放置的元器件并进行连线。

在将元器件放置在板子上面,点击Place—Manully,此时Placement中元器件已放置完。

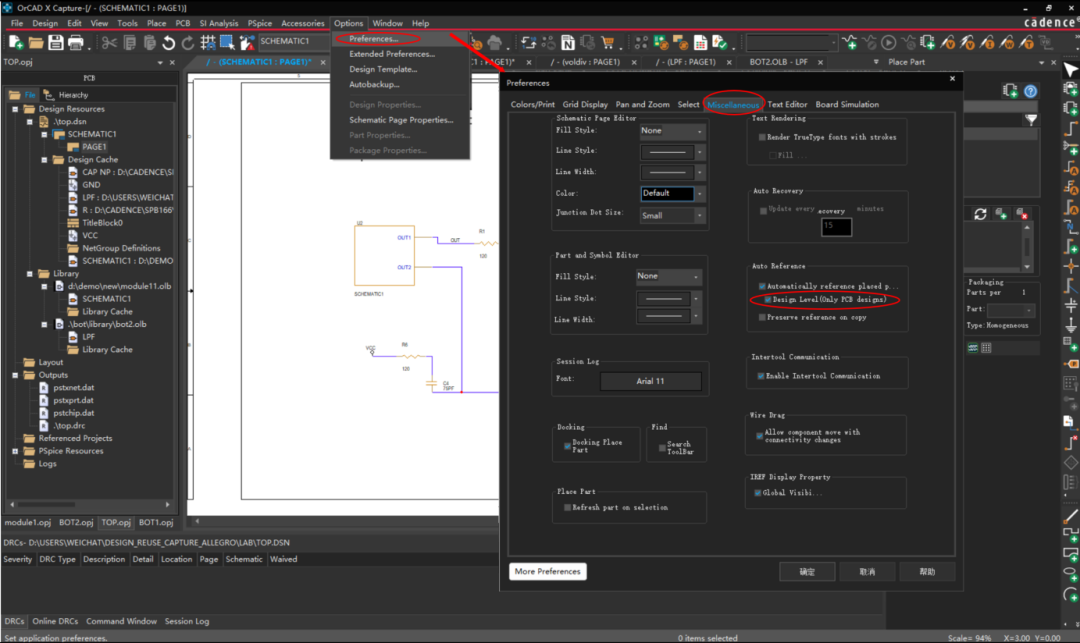

为bot2.dsn创建复用模块,MDD的名称为bot2_lpf.mdd。 10打开经过验证的设计模块的功能原理图top.dsn。为确保主设计能够使用自动引用功能,需要对top.dsn使用Design Level注释。

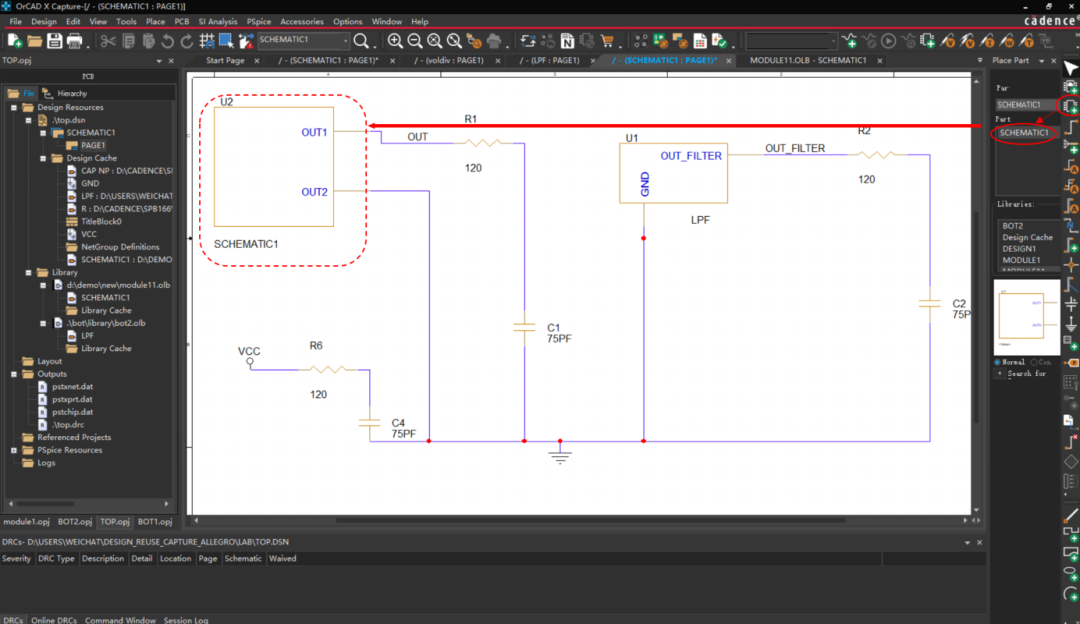

11在top文件中调用前面两个Symbol,将重复使用的IP以原理图和PCB板图形式应用于新的设计中。

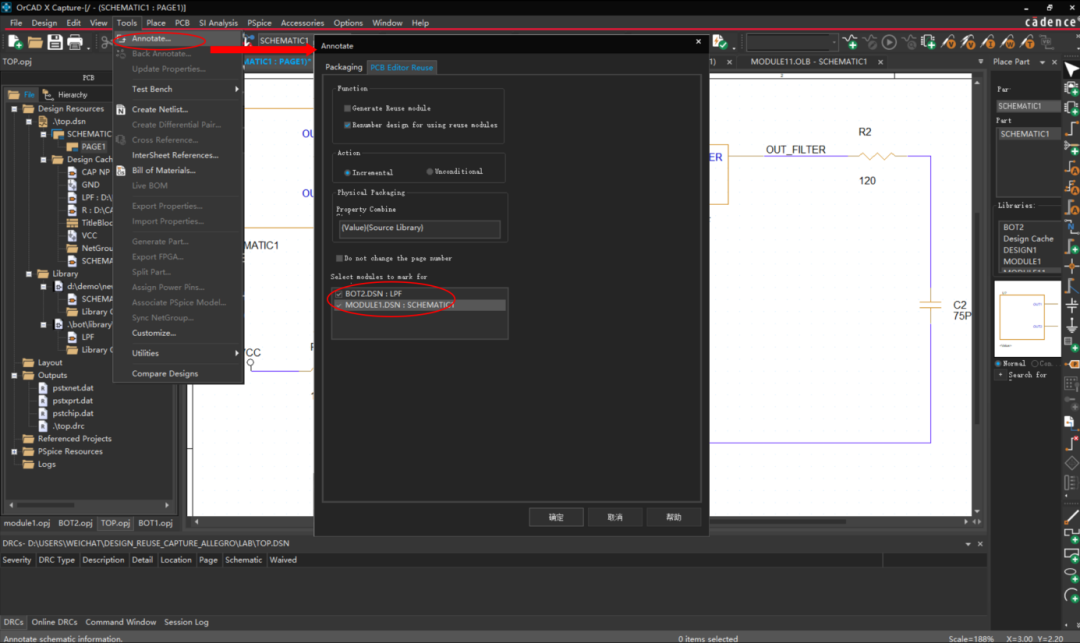

12选择Tools→Annotate,选择PCB Editor Reuse,检查Rennumber design是否使用Reuse模块,点击确定。

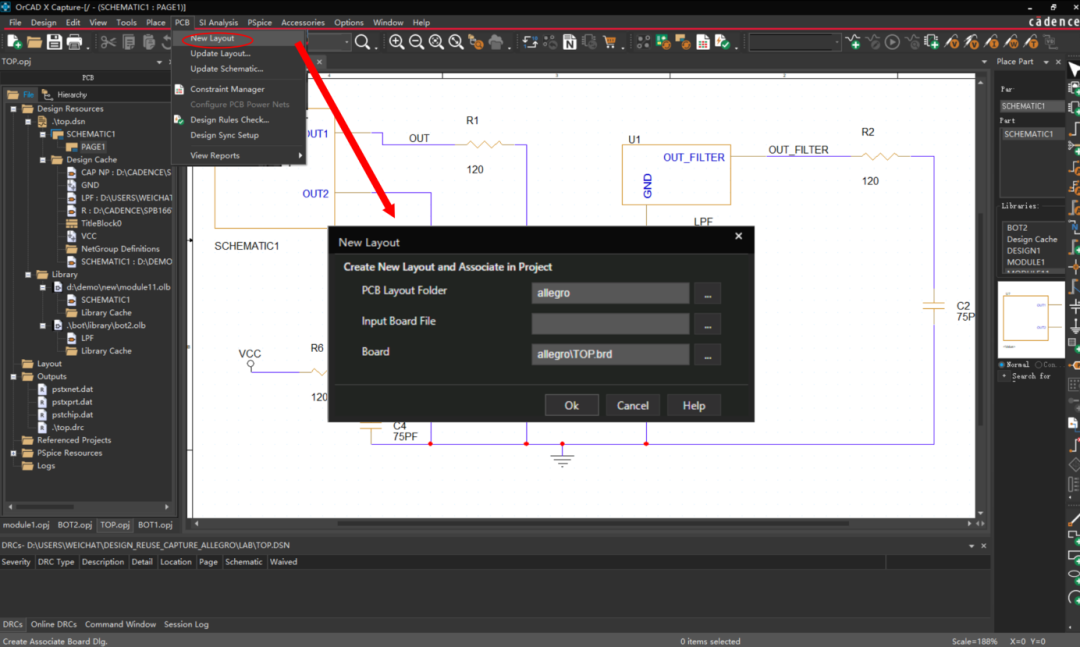

13点击PCB—New Layout,新建一个PCB板,点击OK。

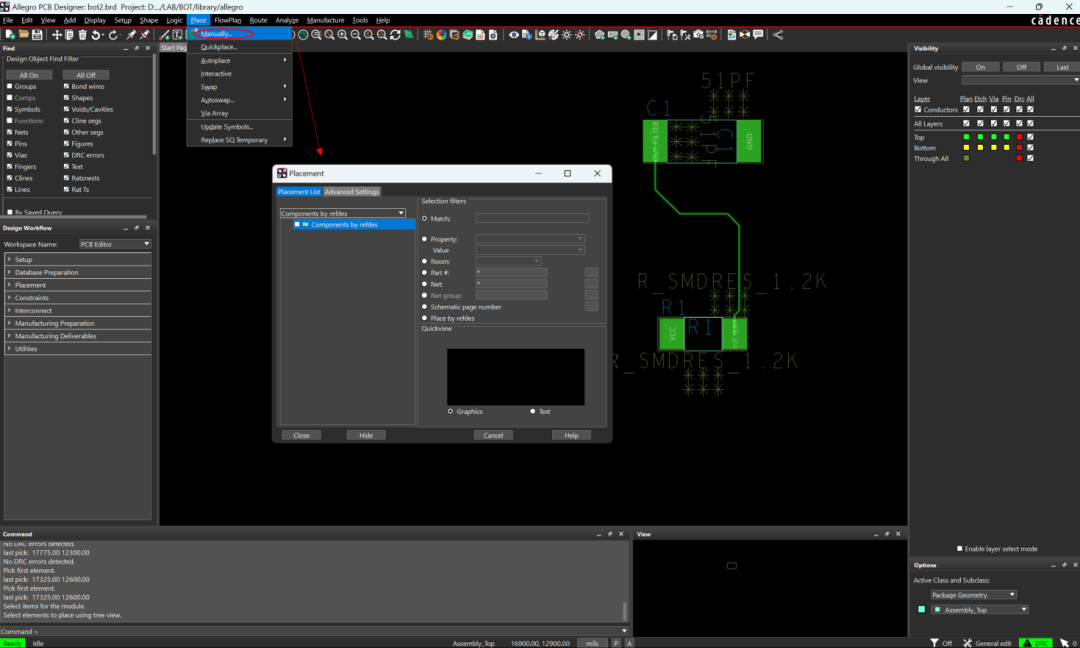

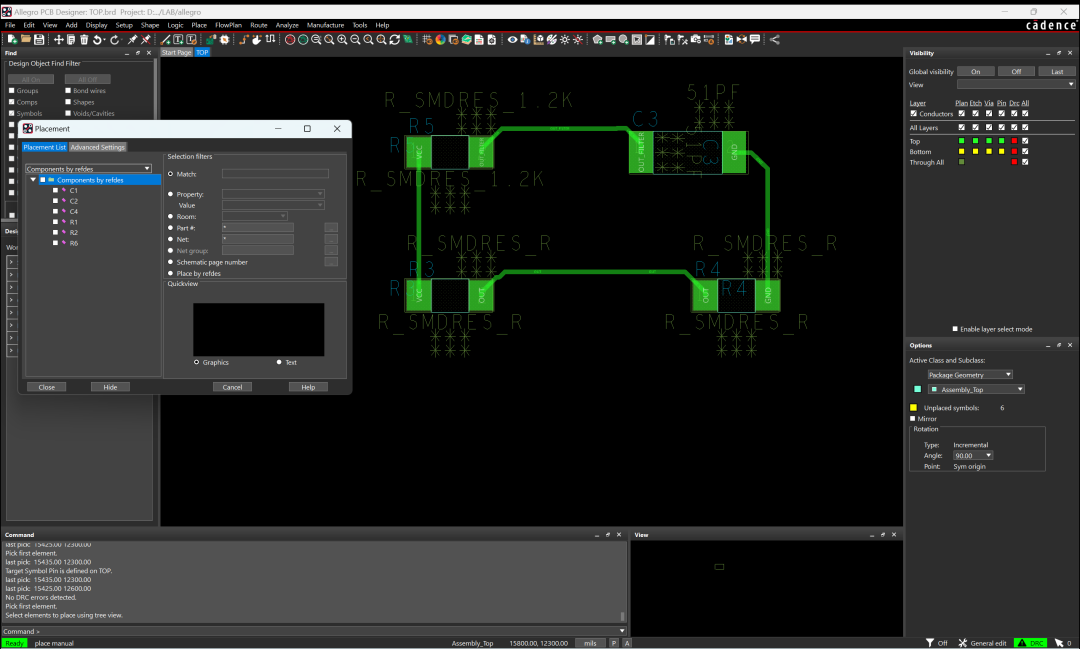

14在pcb板中放置复用元器件。选择Place—Manually,图片中标记的模块为复用模块,先将复用模块放置完成,就能够看到Placement界面中放置模块未出现在面板中了,剩下的就为非复用模块,就可以继续放置非复用模块了。

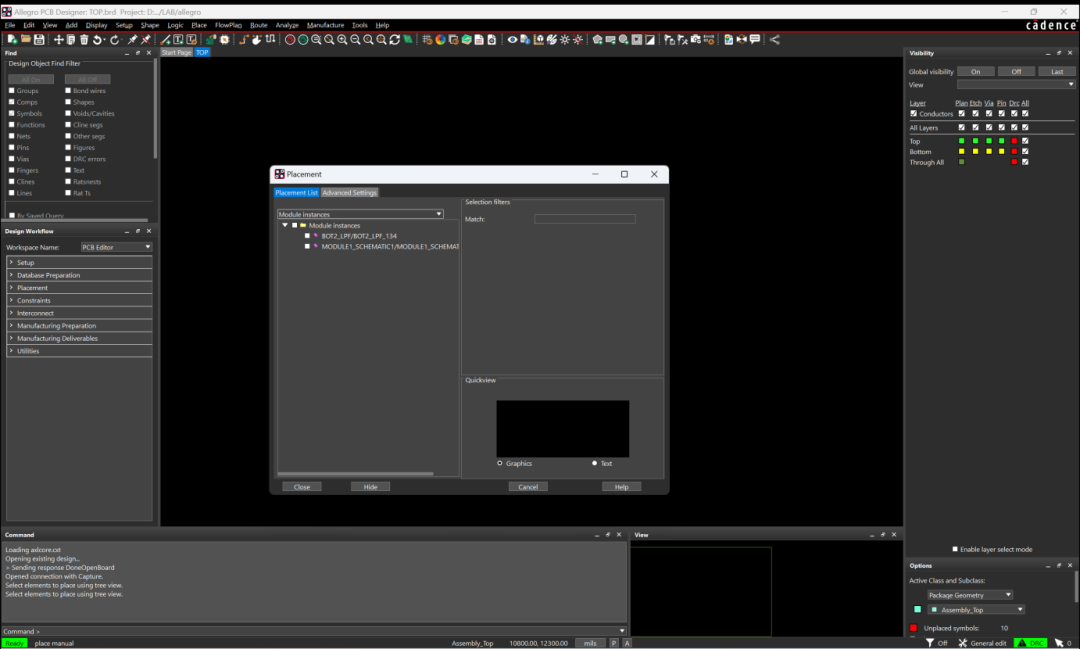

观察模块,从下拉菜单中选择Module instances,我们可以看到复用的两个模块。

15将复用模块放置到PCB板上,在Placement栏内就不会出现已经放置的元器件。

以上就是Design Reuse Module创建使用过程。谢谢大家!

总结通过上面的学习让我们看到了Cadence SPB 23.1进行模块复用的使用办法,通过模块复用的方式可以快速完成布局,这对于复杂的多通道电路效果会更明显。利用这个功能提高布局的效率,从而大大的减少了工程师重复手动操作的次数和难度。该方法相对于其他方法来说,操作简单,功能强大。对于提升设计效率以及设计的准确性都有很大的帮助,阅读完这篇文章的小伙伴可以自己去试一试这个功能,为己所用提高工作效率。

-

Cadence

+关注

关注

64文章

915浏览量

141849 -

Vcc

+关注

关注

2文章

305浏览量

35840 -

电子电路设计

+关注

关注

0文章

26浏览量

9947

发布评论请先 登录

相关推荐

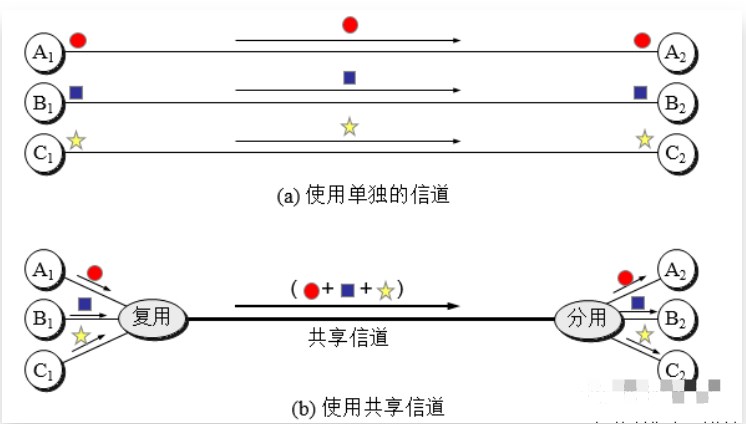

密集波分复用和稀疏波分复用的区别

Cadence安装使用问题

关于复用和映射的疑问求解

光纤是波分复用还是频分复用?波分复用和频分复用有什么不同?

波分复用的特点 波分复用(WDM)和频分复用(FDM)的区别

如何使用Cadence SPB 23.1进行设计复用

如何使用Cadence SPB 23.1进行设计复用

评论