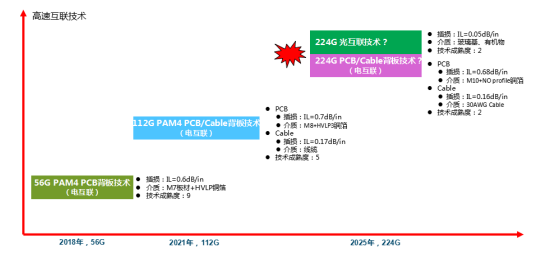

随着电子设备越来越先进,集成电路封装尺寸也变得越来越小,但这不仅仅是为了提高引脚密度。较高的引脚密度对于具有许多互连的高级系统非常重要,但在更高级的网络器件中,还有一个重要的原因是要为这些系统中运行的互连器件设定带宽限制。224G 系统和 IP 正在从概念过渡到商业产品,这意味着封装设计需要满足这些系统的带宽要求。

封装中的“高带宽”并不是一个新概念,而且封装设计人员知道如何构建可在极高频率下工作的互连。例如,在 MMIC 中,接口能以相对较高的功率提供高频率,即使没有高密度封装也能做到这一点。这些封装并不是新兴事物,它们已经在某些实例中使用了几十年。

224G 系统和这些系统的未来一代产品所面临的挑战是,需要实现从直流到极高频率的高带宽。这意味着 BGA 封装、封装基板、封装中介层和内部封装布线的设计必须能在最低阶的模式传播机制下运行。

1

高速接口的封装布线方式

新一代数据中心架构的正常运行离不开正确的封装,这种封装能够支持基本 (TEM) 模式下的超高频模式传播。根据传输线理论,在传输线设计中,假定相关信号以 TEM 模式传播,这在信道的最低带宽要求下依然适用。这些因素尤其会影响信号在封装中的传播行为:

封装底部 BGA bump 之间的间距

半导体晶粒上 bump 之间的间距

封装内部的布线(即跨层布线)

再分布层 (RDL) 中内部走线的尺寸

对封装中内部布线的每个部分进行分析,可以发现这些因素在何处收敛,以确定封装的带宽限制。要知道,这些因素中的任何一个都会限制封装的总带宽,从而限制从封装到 PCB 或连接器的频率。

考虑到 224G 信道的带宽限制,应使用焊球间距不超过 0.8 mm 的封装尺寸来支持 56 GHz 宽带信道。这与英特尔公司提供的仿真数据以及利用过渡过孔周围的整体空腔面积得出的基本计算结果相吻合。

使用封装底部的焊球排列进行简单计算,可以估算出 TEM 模式的频率限制。计算过程如下——

首先,利用 4 焊球 x 3 焊球的方形区域、封装基底材料的介电常数和 0.8 mm 的焊球间距限制,得出半波长截止频率:

F =(真空中的光速)/[sqrt(Dk) * 0.8mm * 2 * 2]

如果基板材料是 ABF,则 Dk = 3.5,近似截止频率为 F = 50 GHz。这与 802.3 工作组的仿真数据和测试数据中的估计值相似,他们将 0.8 mm 间距封装的截止频率设定为 59 GHz。

对于封装内部,可以使用类似的计算方法来确定一阶(TE 或 TM)模式——

假设我们在差分对与接地平面之间使用上下各约 40 微米的带状线,在封装的过孔栅栏之间使用 120 微米的带状线。这些带状线的 TEM 截止频率大约为:

F =(真空中的光速)/[sqrt(Dk) * 0.12mm * 2]

由此得出的结果是 667 GHz。封装内部的实际布线要复杂一些,但这一基本估计值说明了封装设计可以支持的高带宽。在这个简单的例子中,即使带状线与接地平面的距离大一个数量级,也能轻松支持 224G PAM-4 信号。

2

封装如何达到带宽限制

接下来的两节中,我们将详细介绍如何达到上述 TEM 模式传播的频率限制。

封装传输线中的 TEM 和非 TEM 模式

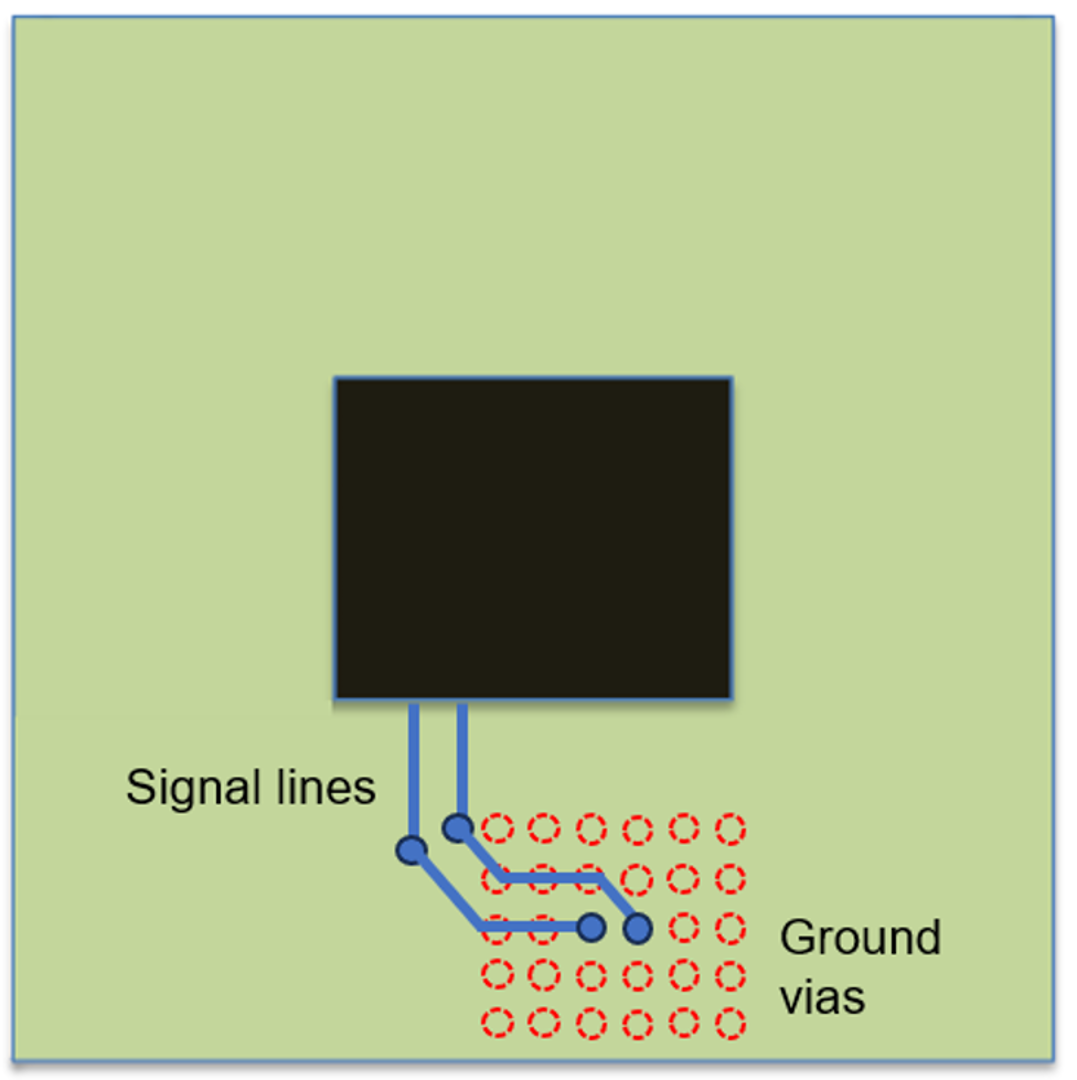

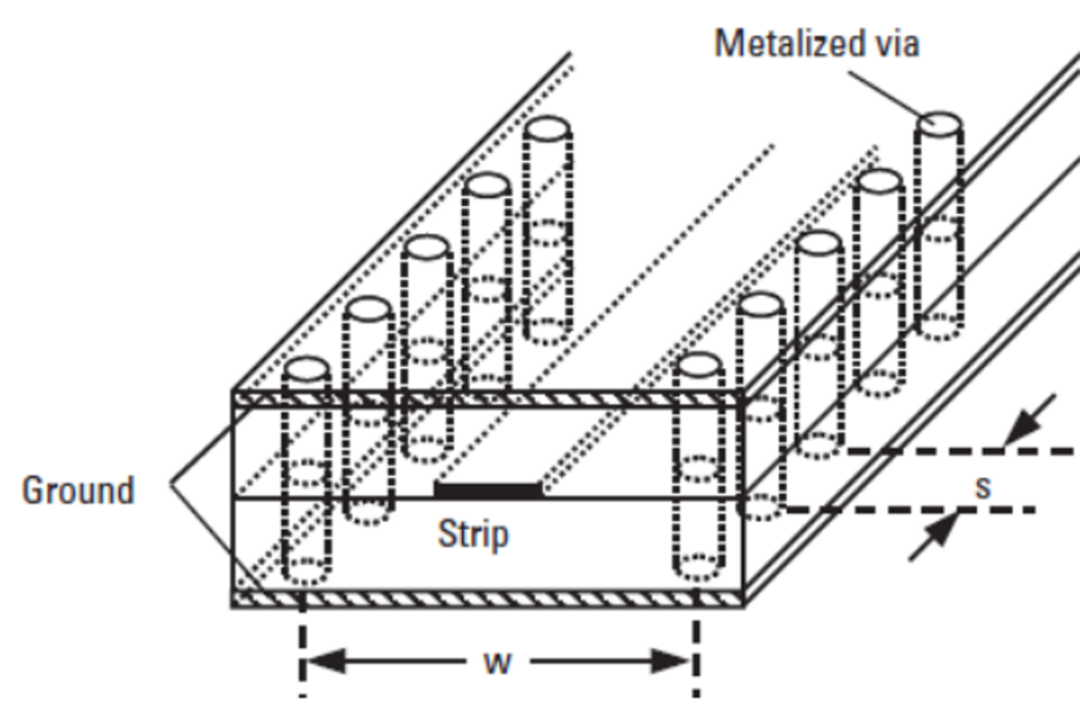

传输线(特别是用于封装布线的带状线)的尺寸非常小,可以实现非常高的 TEM 模式带宽截止频率。下图是这些传输线的典型布线方式;其中包括在过孔栅栏之间布线(通常是差分布线),以设置线路阻抗并在附近线路之间提供屏蔽。

确定封装中使用的带状线带宽截止频率的参数。

在用于封装的带状线中,决定单根带状线中 TEM 模式带宽截止频率的因素同样适用于差分带状线。将差分带状线用于速度极高的 224G 通道,是为了使封装不会从封装基板边缘产生强烈辐射。因为 W 的尺寸较小(约 0.1 mm),TEM 带宽限制非常高,所以传统封装在高频率下也能很好地工作。

焊球间距造成的 TEM 限制

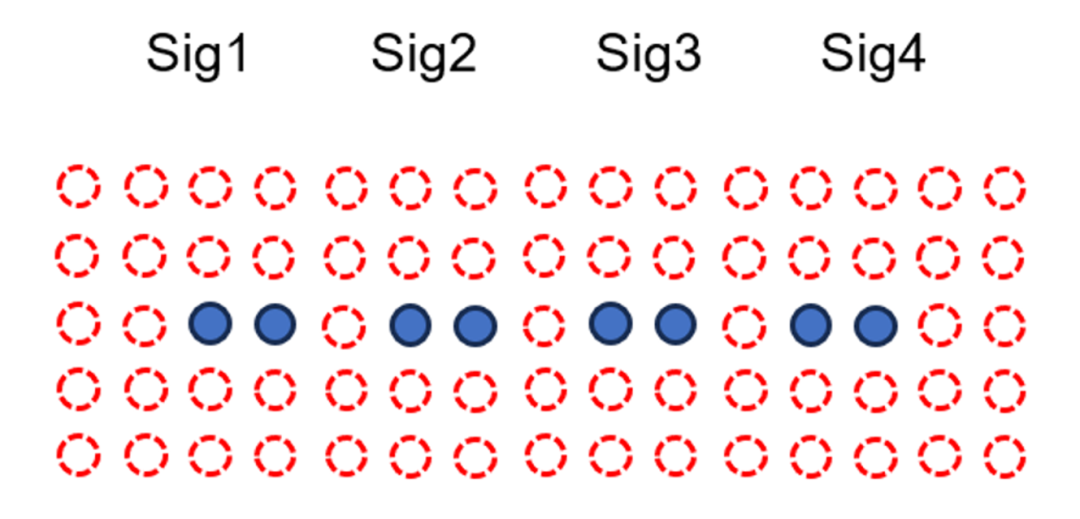

在封装中,焊球间距也会产生类似的带宽限制效应。这是因为高级处理器和 FPGA 高数据速率接口的封装会用接地引脚将信号引脚包围起来。这些引脚在封装底部形成了一个同轴差分对。典型的引脚排列如下图所示,标红的引脚是与 PCB 的接地连接。

典型的封装焊球排列。

封装底部的每个信号引脚都是差分对的一部分。信号引脚周围距离最近的接地引脚负责确定 TEM 模式截止频率,因为这些信号焊球周围的区域看起来就像一个矩形封闭空腔,所以对于较小的空腔,其最低谐振模式的截止频率通常更低。这是因为过孔的作用类似于过孔栅栏,它们有两种功能:

将信号功率限制在过孔周围,以减少串扰

影响连接封装和 PCB 的差分过孔的阻抗

一旦信号带宽超过 TEM 截止频率,部分信号将以高阶模式(TE 或 TM 模式)传播,该模式将在不同封装区域的导体周围呈现出一定的波形。首先,在跨层区域,每根铜线周围都可能存在 TEM 模式,这种模式会阻碍信号在 56 GHz 以上的带宽中进行宽带传播。在封装底部的焊球区域,可能会存在一种 TEM 模式,位于进入 PCB 焊盘的成对焊球周围。对于在 224G 下使用差分对的现代 ASIC 而言,这两种情况都不太理想。

3

如何评估封装带宽

上述计算只是一种粗略的计算方法,将带状线或封装 bump 对近似为矩形波导。但由于过孔/焊球间距和中心导体的影响,封装布线实际上并不是以这种方式工作的。

确定信号行为和信号导体周围电磁场的唯一方法是使用电磁场求解器。使用场求解器计算出的数据,为 224G 封装的每个部分建立仿真模型。这些仿真工具的基本流程如下:

使用电磁场计算结果来确定封装互连 (bump-to-bump) 各部分的 S 参数

将 S 参数回归到网络各部分的线性网络中

可以修改从 S 参数数据中提取的线性网络,以优化信道模型

可将其他因素(如均衡和 PCB 上的传输线)添加到模型中

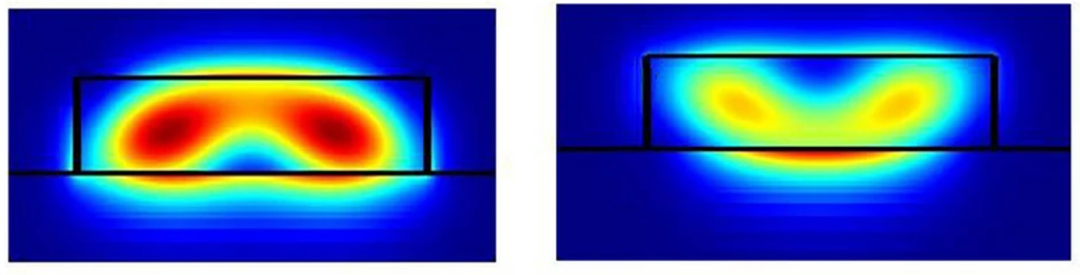

可以通过观察强度模式(通常是二维平面上的彩色强度图)来观察从 TEM 行为到非 TEM 行为的过渡。下图是一个矩形介质波导的简单示例,其中电磁波进入了两种不同的模式(TE 和 TEM)。

总之,在设计互连几何结构时,封装设计人员不仅要考虑低损耗,还要考虑高带宽。目前,限制信道带宽的主要因素是封装上的焊球间距。这意味着按照摩尔定律,如果带宽再增加一倍,封装尺寸就可能达到传统封装制造技术的极限。在考量封装设计时,应该对整个互连过程进行仿真,从封装内的 bump-to-bump 开始。

封装是确保器件正常运行的最后一步。如果您的设计团队需要了解封装设计与涉及 PCB 和连接器的互连之间的相互作用,Cadence Allegro X Advanced Package Designer(Allegro X APD)为集成电路封装提供了先进的设计和分析工具,可以设计和仿真 224G PAM-4 系统,用于实现高效的引线键合设计技术、约束感知基板互连设计以及详细的互连提取、建模和信号完整性/供电分析,同时集成了用于热分析的多物理场求解器,助力设计人员有效验证在散热方面要求严苛的芯片和封装设计。

-

集成电路

+关注

关注

5387文章

11540浏览量

361701 -

asic

+关注

关注

34文章

1200浏览量

120463 -

封装

+关注

关注

126文章

7887浏览量

142920 -

MMIC

+关注

关注

3文章

413浏览量

24302

发布评论请先 登录

相关推荐

HPC需求高速增长推动224G以太网SerDes技术发展加速

古希腊掌管224G 的神 | Samtec 224G PAM4 高速互连大合集!

0805封装尺寸/0402封装尺寸/0603封装尺寸/1206封装尺寸

展望未来英特尔FPGA设计,介绍新型224G PAM4收发器

ASIC,ASIC是什么意思

Molex莫仕推出业界首个芯片到芯片224G连接器组合

CIOE参展手札 | Samtec 224Gbps PAM4性能演示精彩亮相

浅谈下一代数据中心中的224G PAM-4架构

Samtec技术前沿 | 全新224G互连产品系列现场演示

TE AdrenaLINE 224G连接器产品组合介绍

224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(上)

224G 高速互联对 PCB 及覆铜板需求及激光锡球植球机的助力(下)

224G 系统需要多大的 ASIC 封装尺寸?

224G 系统需要多大的 ASIC 封装尺寸?

评论