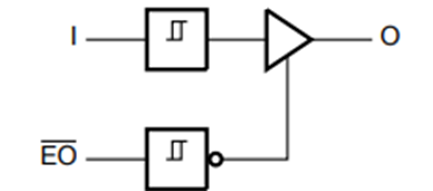

TTL三态输出门与“线与”功能

TTL三态输出门是一种特殊的数字逻辑门,它具有高电平、低电平和高阻抗(三态)三种输出状态。三态门的设计初衷是为了实现多路信号的复用,允许多个设备共享同一总线而互不干扰。而“线与”是一种在总线上实现逻辑与功能的技术,它利用了TTL电路的高阻抗状态。

“线与”功能的实现原理

在TTL电路中,当一个输出处于高阻抗状态时,它相当于一个开路,不对总线产生影响。如果多个TTL三态门的输出都连接到同一总线上,并且它们的使能控制信号是独立的,那么总线的最终状态将由所有使能的三态门共同决定:

- 如果所有使能的三态门输出高电平,总线将呈现高电平状态。

- 如果至少有一个使能的三态门输出低电平,总线将呈现低电平状态。

- 如果所有连接到总线上的三态门都处于高阻抗状态,总线将处于不确定状态,这取决于外部电路或上拉/下拉电阻。

这种通过多个三态门的输出共同决定总线状态的方式,实现了逻辑与的功能,即“线与”。

TTL三态门实现“线与”的条件

- 独立控制 :每个三态门的使能信号需要独立控制,以确保它们可以独立地贡献高电平或低电平。

- 高阻抗状态 :当三态门不使能时,它们应该能够将输出置于高阻抗状态,不对总线产生影响。

- 足够的驱动能力 :至少需要一个三态门在使能时能够提供足够的驱动能力,以确保总线上的逻辑电平能够被识别。

- 适当的总线结构 :总线需要设计为能够处理多个三态门的输出,包括适当的终端电阻和避免反射和串扰。

- 信号完整性 :在高速应用中,需要考虑信号完整性问题,确保总线上的信号在所有设备中都能被正确识别。

TTL三态门实现“线与”的应用场景

- 总线通信 :在多个设备共享数据总线的场景中,使用TTL三态门可以实现高效的数据传输和控制。

- 多路复用器 :TTL三态门可以构建多路复用器,通过选择不同的输入信号来控制总线。

- 控制逻辑 :在复杂的控制逻辑中,TTL三态门可以用于实现条件信号的逻辑与功能。

- 接口电路 :在微控制器和外部设备之间的接口电路中,TTL三态门可以用于数据方向的控制。

结论

TTL三态输出门确实能够实现“线与”功能,这得益于它们的高阻抗状态和独立控制的使能信号。通过合理设计电路和考虑信号完整性,TTL三态门在实现多路信号复用和控制逻辑方面具有显著优势。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

TTL

+关注

关注

7文章

507浏览量

70671 -

逻辑门

+关注

关注

1文章

142浏览量

24217 -

信号完整性

+关注

关注

68文章

1418浏览量

95829

发布评论请先 登录

相关推荐

SN74AVC2T244的使能引脚OE到底是OE=低电平时输出三态,还是OE=高电平时输出三态?

SN74AVC2T244的使能引脚OE到底是OE=低电平时输出三态,还是OE=高电平时输出三态?

TI的手册也能漏洞百出?

发表于 12-04 07:48

三态缓冲器在总线控制中的应用

三态缓冲器在总线控制中的应用是计算机系统设计中的一个关键环节,其独特的三态输出特性使得它在实现多设备间数据共享和传输时显得尤为重要。以下将详细探讨三

三态缓冲器的工作原理和应用

三态缓冲器(Three-state buffer),又称为三态门、三态驱动器,是一种特殊的逻辑门电路,其工作原理主要基于三态输出控制。

三态输出门可以实现线与功能吗

三态输出门(Tri-State Output Gate)是一种特殊类型的逻辑门,它具有三个状态:高电平、低电平和高阻抗状态(也称为高阻抗或浮空状态)。这种门在数字电路设计中非常有用,因为它可以

三态门电路的输出有哪三种状态

三态门电路是一种特殊的数字逻辑电路,其输出可以有三种状态:高电平、低电平和高阻抗状态。这种电路在数字系统中有着广泛的应用,如数据总线、地址总线等。 一、三态门电路的工作原理

三态缓冲器的三种状态分别是什么

三态缓冲器之所以得名,是因为它具备三种不同的工作状态:正常逻辑状态输出、高阻状态和使能状态。这三种状态赋予了三态缓冲器强大的功能和灵活性。

TTL三态门电路的输出状态?

TTL(晶体管-晶体管逻辑)三态门是一种特殊类型的数字逻辑门,它具有三种输出状态:高电平、低电平和高阻抗状态(也称为三态或高阻

TTL三态门的特点及应用都有哪些呢

TTL(晶体管-晶体管逻辑)三态门是一种特殊类型的逻辑门,它具有三个状态:高电平、低电平和高阻抗状态(也称为“三态”或“浮动”状态)。

TTL三态输出门能否实现“线与”?为什么?

TTL三态输出门能否实现“线与”?为什么?

评论