电子发烧友网报道(文/周凯扬)随着摩尔定律失效,高性能计算芯片的规模进一步扩大,数据中心集群庞大的功耗已经成为我们不得不面临的问题。早在2015年SIA的预测中,到2040年全球计算资源的能源供给就不再具有可持续性,而如今随着人工智能的爆发,计算资源的需求更是猛涨。

以用于训练AI大模型的计算资源为例,每六个月翻倍的速度已经远超高性能计算集群的组建速度。无需等到2040年,到了2030年训练单个大模型所需的资源就将超过TOP500所有超算的算力总和,而所需要的电力供应也将达到国家级。解决能源可持续的问题已经避无可避了,但除非我们放缓发展速度,或是颠覆计算方式,是很难实现这一目标的。

对于应用层还没进入商业模式成熟和完全盈利的人工智能来说,放缓发展速度自然是不可取的。那么也就只剩下颠覆计算方式一途,而大幅降低能耗的超导计算,也就理所当然地成了多数研究的重点方向。

显著降低功耗,最大开销成为冷却

2020年,日本国立横滨大学的一个研究小组就展示了一个超导CPU,并成功实现了流片。该处理器主要采用约瑟夫森结架构打造,这是一种经典的超导三层器件架构,也是超导逻辑单元中取代晶体管的基础元件。因为其独特的物理特性,该器件工作时的开关功耗只有10-21J左右,这样一来动态功耗相比传统CMOS器件极大降低,加之超导体无电阻的特性,静态功耗无限趋近于零。

超导体的出现为降低功耗提供了最大的可能性,因为其在通过电流时并不会消耗能量。最大的能耗开支莫过于需要在低温下工作的冷却方案供电,比如超导芯片的处理单元,往往需要低至4K的冷却温度。但即便如此,几乎零电阻的互联、基于超短脉冲构建的数字逻辑,都为现代计算资源大规模扩展提供了足够的优势。

而且随着计算资源规模的扩大,冷却方案开销的边际成本也会越小,据imec研究表明,一旦达到数十petaflops,超导计算机相比传统的计算机就要节能了,而这样的算力要求,TOP500中排名前30的超算已经可以做到了。

而Imec近期发布了他们采用标准CMOS工艺制造的超导计算单元,基于该技术打造的处理器能效将是当下最高效芯片的100倍,甚至可以将一个数据中心级别的计算资源塞进鞋盒大小的系统中。

将超导带出实验室的方法——兼容现有的CMOS制造技术

尽管超导可以降低功耗提高计算密度,但对于目前的大部分研究来说,都只停留在实验室阶段,要想真正实现大规模量产无异于痴人说梦。比如上文提到的横滨国立大学超导CPU,就是基于超导铌实现的,这种材料在可预测的实验室环境中表现良好,但要想用于制造工艺中就存在不少难题了。

铌对传统半导体加工温度及其周围材料都很敏感,一加热就会失去超导能力,因此与标准CMOS工艺流程不兼容。为此,imec改用了氮化铌钛作为基础超导材料。氮化铌钛可以承受CMOS制造工艺所用的温度,而且与周围层的反应较少。

同时imec还为约瑟夫森结的势垒层选择了一个新材料,无定形硅。传统的约瑟夫森结势垒层材料,比如氧化铝等,可以在可控的条件下生长,但为了达到远高于CMOS工艺芯片的密度,就必须进一步压缩其厚度,可这么薄的氧化物已经到了无法制造的程度。无定形硅的出现,则允许使用更厚的势垒层,实现210nm这样的临界尺寸。

在电路层面,同样需要对逻辑和存储结构重新设计。Imec设计出了一种全新的逻辑架构,名为脉冲守恒逻辑,输入和输出的数量保持一致,且SFQ(单通量量子)的总数保持守恒。通过不同约瑟夫森结和电容的组合将SFQ引导至不同输出,从而产生我们常见的逻辑OR和AND。在Imec的设计中,SRAM也是基于约瑟夫森结重新设计的,不过DRAM还是采用传统的硅工艺,但也需要从室温降低至77K的低温环境,用于提高效率。

鞋盒大小的数据中心,也需要3D堆叠实现

在基于CMOS工艺打造的数字芯片上,随着缩小晶体管变得越来越困难,我们已经开始广泛利用3D堆叠技术提高性能。但由于芯片内部的超大功率和热量,堆叠方案已经逐渐面临更大的挑战,如何做好散热成了多数3D堆叠方案必须解决的首要问题。

对于基于超导体的芯片设计而言,同样可以借助3D堆叠来实现更高的密度。结合硅中介层和玻璃基板这样的先进封装技术,将超导处理单元与嵌入式超导SRAM和DRAM堆叠在一起。芯片的大部分都将浸没在液氮中,冷却至4K。

在imec的模拟中,他们将100块超导体芯片板打造堆叠在一起,中间只留出极小的空间,整个系统的体积大小只有20x20x12厘米,与一个鞋盒大小近似。但正是这样一个鞋盒大小的系统,总功耗只有500kW,却可以提供将近20exaflops(BF16)的算力。

而这仅仅是Imec路线图中第一套方案,在后续的产品中,会进一步缩小约瑟夫森结和互联的尺寸。未来通过进一步提高逻辑芯片的密度,芯片板的数量也会随之减少,这样提高性能的同时,也会降低工艺复杂性和成本。

写在最后

尽管超导计算让我们看到了可行的技术路线,但即便是imec也不认为超导数据技术会取代传统的CMOS计算,而只是作为部分特定应用补充。这一技术的主要应用场景还是在大型的数据中心,为人工智能和机器学习处理提供基于云端的训练推理等,因为只有这样的环境内才能有条件实现超导所需的冷却技术。在消费电子领域,传统的CMOS硅工艺依然不可取代。

值得一提的是,这一技术与Imec基于CMOS制造工艺的超导量子比特技术同样可以做到无缝集成,可以说是电子计算与量子计算的完美结合。但即便搞定了基础材料工程设计,以及架构的设计,还有电路开发设计这一环目前没有打通,需要EDA厂商为其开发特定的流程工具。

-

处理器

+关注

关注

68文章

19661浏览量

232501 -

CMOS

+关注

关注

58文章

5870浏览量

237465 -

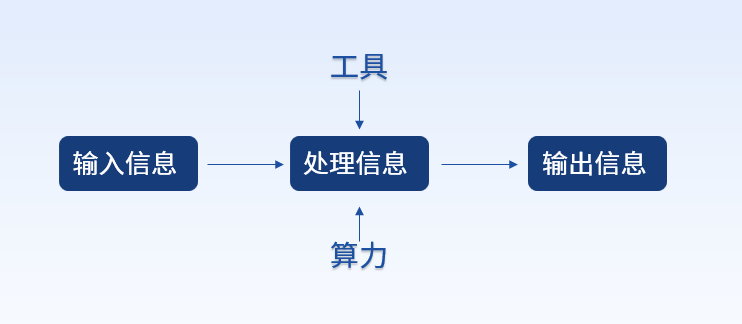

算力

+关注

关注

1文章

1087浏览量

15313

发布评论请先 登录

相关推荐

走进北大 | 算能RISC-V通用处理器设计成功开课

盛显科技:拼接处理器如何实现高效数据拼接操作?

【「算力芯片 | 高性能 CPU/GPU/NPU 微架构分析」阅读体验】--全书概览

名单公布!【书籍评测活动NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架构分析

用ARMxy ARM工业控制器自带的1Tops算力实现高性能图像处理

20exaflops算力只有鞋盒大小,靠CMOS技术就能实现的超导处理器

20exaflops算力只有鞋盒大小,靠CMOS技术就能实现的超导处理器

评论