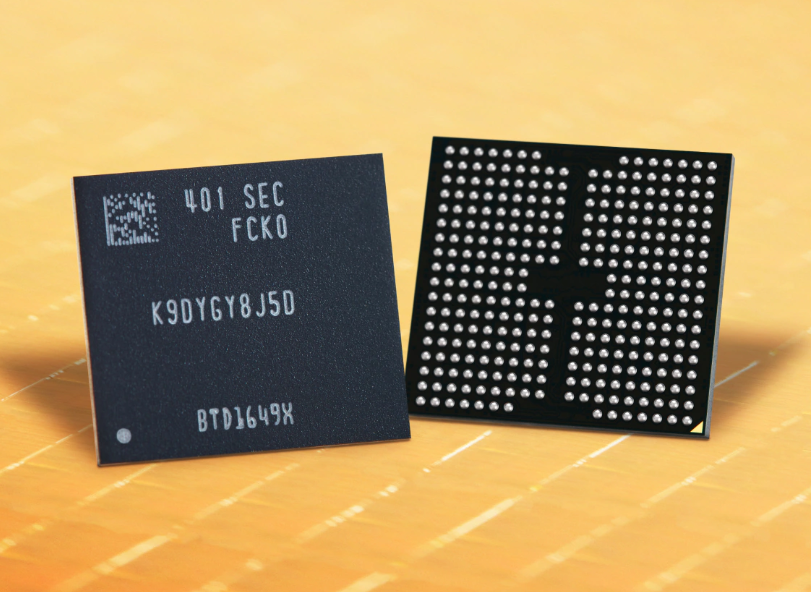

在近日举行的IEEE IMW 2024活动上,三星DRAM部门的执行副总裁Siwoo Lee宣布了一个重要里程碑:三星已与其他公司合作,成功研发出16层3D DRAM技术。同时,他透露,竞争对手美光也已将其3D DRAM技术扩展至8层。

然而,Siwoo Lee强调,尽管取得了这一显著成就,但三星目前并未计划立即进行大规模生产。相反,公司正专注于研究3D DRAM或垂直堆叠单元阵列晶体管(VS-CAT)技术的可行性和潜在应用。他强调,这项技术可能在未来对DRAM市场的格局产生深远影响。

Siwoo Lee去年加入三星,此前他在美光负责未来存储芯片的研发。他丰富的行业经验和深厚的技术背景为三星在DRAM领域的技术创新和战略布局提供了有力支持。随着3D DRAM技术的不断发展,我们有理由期待三星将在这一领域取得更多突破。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

459文章

51732浏览量

431019 -

DRAM

+关注

关注

40文章

2337浏览量

184588 -

三星

+关注

关注

1文章

1657浏览量

31967

发布评论请先 登录

相关推荐

预期提前,铠侠再次加速,3D NAND准备冲击1000层

电子发烧友网报道(文/黄山明)近日,铠侠再次宣布,将在2027年实现3D NAND的1000层堆叠,而此前铠侠计划是在2031年批量生产超1000层的3D NAND存储器。

三星否认重新设计1b DRAM

问题,在2024年底决定在改进现有1b nm工艺的同时,从头设计新版1b nm DRAM。 不过,三星通过相关媒体表示相关报道不准确。尽管三星否认了重新设计,但有业内人士透露,三星的目

三星1c nm DRAM开发良率里程碑延期

据韩媒MoneyToday报道,三星电子已将其1c nm(1-cyano nanometer)DRAM内存开发的良率里程碑时间从原定的2024年底推迟至2025年6月。这一变动可能对三星

三星电子实现低功耗LPDDR5X DRAM的量产

三星电子于6日正式宣布,其已成功实现业内领先的12纳米级低功耗双倍数据速率动态随机存储器(LPDDR5X DRAM)的量产,这款存储器以惊人的0.65毫米封装厚度引领行业,同时提供12GB及1

三星电子否认HBM3e芯片通过英伟达测试

韩国新闻源NewDaily近日发布了一则报道,声称三星电子的HBM3e芯片已成功通过英伟达的产品测试,预示着即将开启大规模生产并向英伟达供货的序幕。然而,

SK海力士5层堆叠3D DRAM制造良率已达56.1%

在全球半导体技术的激烈竞争中,SK海力士再次展示了其卓越的研发实力与创新能力。近日,在美国夏威夷举行的VLSI 2024峰会上,SK海力士宣布了其在3D DRAM技术领域的最新研究成果,其中5层堆叠的

SK海力士五层堆叠的3D DRAM生产良率达到56.1%

)提交了一份关于3D DRAM(三维动态随机存取存储器)的详细研究论文。该论文不仅揭示了SK海力士在3D DRAM领域取得的显著进展,更向世

三星将于今年内推出3D HBM芯片封装服务

近日,据韩国媒体报道,全球领先的半导体制造商三星即将在今年推出其高带宽内存(HBM)的3D封装服务。这一重大举措是三星在2024年三星代工论坛上正式宣布的,同时也得到了业内消息人士的证

3D NAND闪存来到290层,400层+不远了

电子发烧友网报道(文/黄晶晶)早在2022年闪存芯片厂商纷纷发布200+层 3D NAND,并从TLC到QLC得以广泛应用于消费电子、工业、数据中心等领域。来到2024年5月目前三星第

三星电子研发16层3D DRAM芯片及垂直堆叠单元晶体管

在今年的IEEE IMW 2024活动中,三星DRAM业务的资深副总裁Lee指出,已有多家科技巨头如三星成功制造出16

3D DRAM进入量产倒计时,3D DRAM开发路线图

目前,各大内存芯片厂商,以及全球知名半导体科研机构都在进行3D DRAM的研发工作,并且取得了不错的进展,距离成熟产品量产不远了。

发表于 04-17 11:09

•961次阅读

三星电子:2025年步入3D DRAM时代

据分析师预测,DRAM行业将于2030年前缩减工艺至10nm以下,然而当前的设计已无法在此基础上进行延伸,故而业内开始寻求如3D DRAM等新型存储器解决方案。

三星2025年后将首家进入3D DRAM内存时代

在Memcon 2024上,三星披露了两款全新的3D DRAM内存技术——垂直通道晶体管和堆栈DRAM。垂直通道晶体管通过降低器件面积占用,实现性能提升;

三星已成功开发16层3D DRAM芯片

三星已成功开发16层3D DRAM芯片

评论