电子发烧友网报道(文/周凯扬)随着EDA市场的竞争加剧,越来越多的供应商开始在工具中引入AI/ML,从而帮助芯片制造商和系统供应商区分其产品。去年是AI EDA工具陆续推出的一年,所以业内对于AI深入设计的做法都持以谨慎态度,但伴随着AI工具对于改善设计效率的效果逐渐显现,近一年以来AI驱动EDA工具辅助流片的产品也在不断增加,这一趋势也反映到了EDA巨头的财报表现上。

新思:AI EDA工具成为抢单利器

新思于5月22日发布了今年Q2的财报,其季度营收达到14.55亿美元,同比增长15%,非GAAP营业利润率为37.3%,同比增长约3%。为此,新思再度上调了全年收入和非GAAP每股收益的指引。

在这样一个人工智能芯片和软件定义系统普及的时代,新思认为这些技术趋势推动了研发的系统复杂性,却也为其带来了不少机遇。如今其芯片客户竞相设计和制造复杂的专用芯片,而这些客户已经不再局限于芯片设计公司,还包括不少系统方案公司。

AI工具的快速采用也给新思带来了前所未有的竞争力,其设计自动化业务营收同比增长14%,得益于整体业务的强劲表现和Synopsys.AI在客户内的快速采用,包括DSO.ai、ASO.ai等一系列AI套件。比如第二季度,多家亚洲设计服务厂商借助DSO.ai突破了最高频率目标,而一家领先的美国GPU厂商通过部署DSO.ai提高了生产力等。

新思也提到,在模拟与混合信号设计中,客户希望借助新思的解决方案尽快实现流程现代化,并迁移到更先进的工艺节点。新思在本季度赢得了10个替代设计,包括一家领先的美国系统方案公司改用了新思的全流程方案,一家领先的亚洲存储公司为其下一代存储产品设计改用了新思的模拟设计环境等。在验证工具上,VSO.ai也得到了30多家客户的广泛应用,将周转时间最高缩短了10倍。

不过,新思对于今年中国市场的业绩持谨慎态度,虽然上半年的营收表现不错,但由于宏观经济挑战和一些限制原因,新思预计今年来自中国市场营收依然会呈现增长的态势,但占比可能会略低于去年。

Cadence:AI自动化的普及才刚刚开始

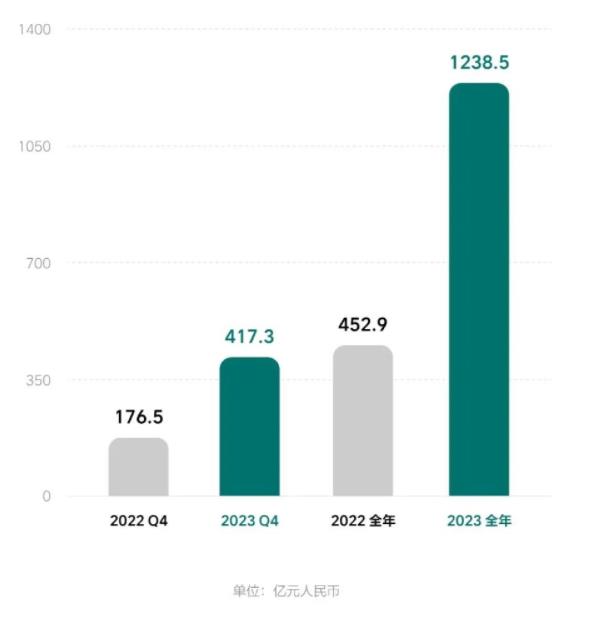

Cadence于4月底发布了今年Q1的财报成绩,该季度总营收达到10.09亿美元,相较去年同期的10.22亿美元几乎没有变化。Cadence预计第二季度的营收在10.3亿美元至10.5亿美元之间,2024财年的总营收在45.6亿至46.2亿美元之间,高于去年的40.9亿美元总营收。之所以能有不俗的Q1表现和全年营收预期,Cadence将其归功于去年与今年发布的多款新品,以及其AI设计引擎收获的巨大成功。

在不久前举办的CadenceLive大会上,高通公司就表示,他们借助Cadence的Verisium AI验证平台,将验证时间缩短了20倍。而Cadence的另一个大AI工具Cerebrus在数字全流程设计上也得到了广泛使用,提供一流PPA和效率的同时,已经成为大客户设计流程以及多个晶圆代工厂新工艺节点DTCO流程中不可或缺一部分,目前已经用于350多个设计项目的流片,同时有50多家客户在3nm及以上工艺的设计中部署了Cadence的解决方案。

Cadence指出,除了数字设计领域AI的普及之外,未来PCB和封装领域也会迎来更多的AI自动化,而Cadence的Allegro X AI将成为其中的佼佼者,目前已经在300多家客户中得到使用。比如英特尔就提到在PCB设计上使用Allegro X AI后,实现了4倍到10倍的效率提升。

西门子:EDA撑起DI业务

相较另外两家EDA巨头,西门子的EDA业务被归为其数字化工业集团,与其他工业自动化、电气自动化等业务并列。从西门子近期发布的Q2财报来看,其整个数字化工业集团的业务营收为45.05亿欧元,同比下滑13%。

这是由于市场环境挑战较大,客户库存较高,自动化业务订单量整体下降造成的,尤其是在中国市场。其软件业务却从去年Q2的11.65亿欧元增长至13.66亿欧元,订单数量也有两位数的增长。西门子表示这主要是由EDA业务增长驱动的,得益于美国地区的半导体客户高涨的EDA需求,西门子在EDA业务上实现了50%以上的营收增长。对于今年下半年的预期,西门子表示在软件业务上将迎来更加强劲的客户活动,且集中在EDA和授权业务上。

目前西门子已经将不少AI功能导入其EDA工具中,比如Solido DE,就是一个全面由AI驱动的SPICE级设计环境,集成了AI和云部署技术。Solido DE可以借助AI来帮助用户确定优化途径,改进电路PPA并提供良率分析,比传统的蒙特卡罗分析法要快上几个数量级。

目前不少大客户已经引入了西门子的AI EDA工具,比如SK海力士。为了进一步提高验证精度和周转时间,SK海力士已经在下一代存储器技术的设计中用到了Solido DE,并大幅缩短了从初始设计到生产所需的时间。除此之外还有Forza Silicon这一CMOS图像传感器厂商,也将Solido DE作为其仿真环境,为机器视觉、汽车、XR等应用设计高分辨高速CMOS图像传感器。

近日,西门子发布了全新的Catapult AI NN软件,用于ASIC和SoC上神经网络加速器的高级综合,可以将AI框架中的神经网络描述转换成C++,并综合成Verilo或VHDL,用于ASIC、FPGA或SoC上的实现。这样可以使得AI开发人员在软件开发的过程中,在芯片设计上获取最佳的PPA表现。

写在最后

相较EDA巨头,国产EDA厂商对于AI的导入进度则略显落后。虽然这并不影响其在设计活动频繁的去年和今年营收快速增长,但同样快速增长的研发投入也在进一步压缩其利润空间。而目前主流芯片设计厂商已经将AI EDA工具引入了最先进芯片的设计流程中,并在PPA和设计效率上展现了前所未有的优势。相信这也是国内EDA厂商在全力打造全流程工具的同时,加大在AI引擎上研发投入的原因。

-

eda

+关注

关注

71文章

2764浏览量

173360 -

AI芯片

+关注

关注

17文章

1889浏览量

35074

发布评论请先 登录

相关推荐

世界先进9月营收大幅增长34%

台积电8月营收大增33%,AI芯片需求强劲

韩企存储芯片在华热销,营收翻倍增长

2024年全球半导体营收预计迎来20%增长

阿里巴巴季报出炉 阿里云二季度营收增长6%

世芯聚焦HPC、AI领域,预计营收持续增长

高温来势汹汹,光伏电站如何应对

AI芯片设计来势汹汹,EDA巨头营收顺势增长

AI芯片设计来势汹汹,EDA巨头营收顺势增长

评论