从理论上讲,碳化硅 (SiC) 技术比硅 (Si) 具有优势,这使得它看起来可以作为电力电子中现有 MOSFET 的直接替代品。这在一定程度上是正确的,但只要关注该技术与硅的不同之处,以及如何优化电路技术(例如软开关),超越硅的实际应用,就可以从 SiC 中获得更多收益。

与硅相比,SiC 的带隙更宽,因此击穿电压和电子迁移率更高,从而降低了导通电阻。与硅相比,SiC 的开关速度也更快,从而提高了效率,并能够设计出体积更小的电力电子系统。SiC 的热导率也明显高于硅,因此可以设计出在更高温度下运行的电力电子设备,而不会牺牲性能或可靠性。

基于传统硅超结MOSFET的电路只需考虑简单的软开关技术,但高典型工作频率意味着SiC需要仔细分析何时和何处出现损耗。从而,该分析可以导致新颖解决方案,避免了传统MOSFET电路设计固有的损耗。

例如,SiC等宽禁带技术的一个关键优势是能够为给定通态电阻保证更高的击穿电压。这允许使用比体硅器件所需更薄的漂移层,从而比所需厚的层的体硅器件具有更低的电阻。同时,晶体格子的组成提供了更高的载流子迁移率。结果是更高的导电性。

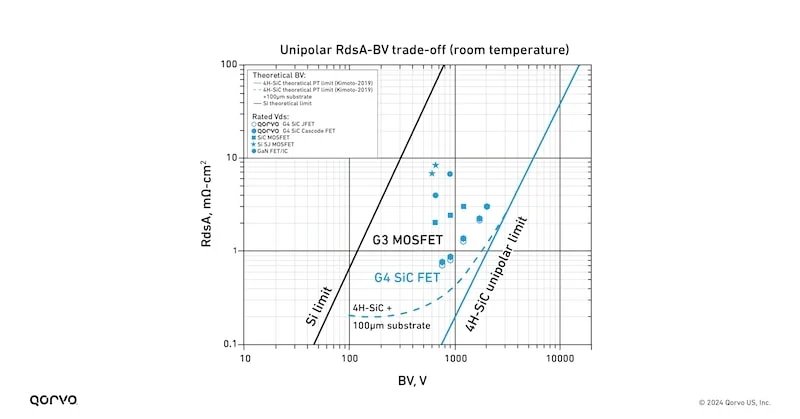

图1

图1结型场效应晶体管(JFET)是最好的选择来最小化漏源电阻。在MOSFET中,载流子必须通过p基(p井)区域的表面通过MOS界面处的电阻性反转通道进入n型漂移区域。然而,在JFET中,没有这样的反转通道。通过使用高体多数载流子迁移率,JFET接近于通态电阻的理论限制,相比击穿电压而言。Qorvo的SiC JFET器件允许与MOSFET设计相比,具有更大的击穿电压安全裕度和约一半的通态电阻的晶体管设计。

传统上,仅使用耗尽型JFET会带来电路设计挑战。作为一个常开设备,它需要负电压完全关闭。然而,SiC MOSFET具有低阈值电压,因此在真实电路中,负门电压并不少见。应用负电压可以防止在温度极端时发生意外开启,因为阈值电压可能低于名义水平。

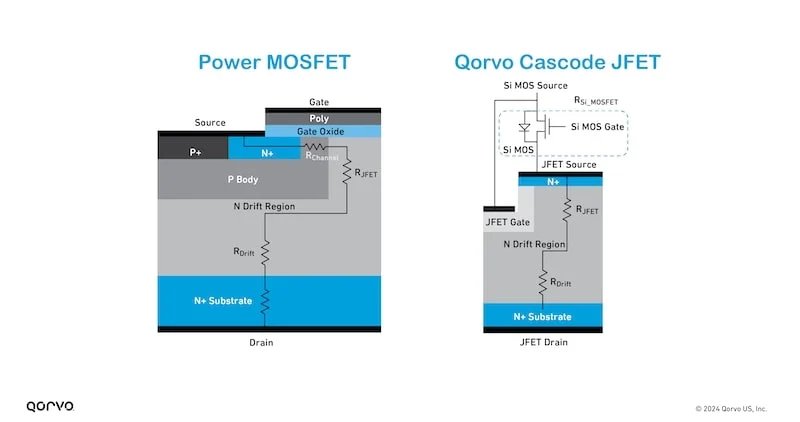

Qorvo的解决方案将SiC JFET与低压硅MOSFET结合在串联结构中,其中SiC JFET的栅源电压是Si MOSFET漏源电压的反向。该串联结构如图2所示。在串联配置中,外部栅驱动器控制低压Si MOSFET漏源电压,间接驱动高压SiC JFET。这种串联配置为习惯于使用硅超结MOSFET的工程师提供了熟悉的控制方式。MOSFET的较低工作电压对该设备对的整体通态电阻的贡献不到10%。为了方便集成,Qorvo以单个封装提供此配置。

图2

图2串联结构通过Si低压MOSFET控制开关,将控制逻辑与高压JFET分离。这种分离提供了优化栅控电压范围和栅电荷以实现低压Si MOSFET的机会,同时不损害SiC JFET的全部性能优势。

与传统SiC MOSFET通常需要高达18V的栅电压来完全激活器件并获得低通态电阻的全部优势相比,串联架构允许更低的最大栅控电压,并且无需负电压用于关断状态。电压范围的缩小减少了栅电荷约50%(从18V / -4V到10V / 0V),在轻负载下,特别是对于软开关应用,减少了开关过程中的损耗。

采用JFET结构的SiC转换器大大缩小了芯片尺寸。Qorvo的器件与硅超结器件相比,具有近十倍的芯片面积减小,但具有相同的功率处理能力。SiC的热导率和优越性能抵消了由于芯片尺寸显著减小而带来的热阻增加。通过使用银浸渗来增加散热片连接的热导率,与传统焊料相比,提供了6倍的热导率改进,以抵消进一步增加的热阻。

将串联结构应用于SiC JFET进一步改善了效率,通过减小影响硅超结器件和SiC MOSFET的杂散电容提高了密度。较低的杂散电容使开关频率高于硅器件甚至SiC MOSFET实际可行的范围。

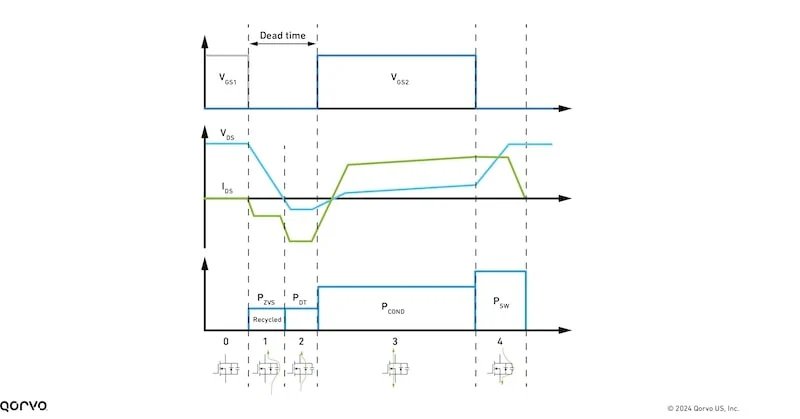

图3

图3这些优势在软开关电路结构中最为明显。尽管使用硅器件的软开关技术解决了开启和关闭阶段的一些明显损耗来源,但最新一代SiC晶体管的快速开关能力解决了通常被忽视的更微妙问题。

许多基于硅器件的电路采用零电压开关(ZVS)。它的主要目的是在电流开始自由通过晶体管通道之前,减少漏源电压(IDS)和漏源电压(VDS)之间的电压,以消除开启开关损耗。输出电容(即漏源电容和栅与漏之间的电容之和)通常在上一个周期中关闭设备时完全充电到直流链路总线电压,并在下一个ZVS开启事件期间重新用于负载以避免损耗。

传统Si器件使用ZVS开启可能导致开关周期中的死时间长达300ns,这是由于硅器件的高输出电容。对于500kHz(2µs周期)的开关频率,开启和关闭转换期间的300ns死时间占占空比的30%。

与Si MOSFET相比,SiC JFET具有更低的输出电容,清除时间较短,特别是在漏源电压偏差较低的情况下,Si MOSFET的输出电容会显著增加。硅超结器件在低漏源电压偏差下的CV曲线具有较强的非线性,这导致半桥拓扑中在总线电压和0V附近的高压过渡时间。这缩短了ZVS所需的死时间,可以用于更高频率的操作或更多功率传递到负载。

由于较长的电压过渡时间和相对较高的关断开关损耗,使用Si器件设计的ZVS电路的开关频率限制在150kHz以下。借助Qorvo SiC FET的快速开关能力,开关频率边界被推动到500kHz以上。与开启开关损耗类似,如果尽量减小关断期间电流下降和漏源电压上升之间的重叠,效率将得到改善。

但是,随着开关速度的增加,电磁干扰变得更具挑战性。设计师必须在设计阶段尽早地,通过小心减少PCB上的有意义的电流换位环的寄生参数,充分利用SiC的快速开关能力。但是,在考虑到安全要求(例如间隙放电等)时,优化的空间有限。一旦电路设计完成,有两种常见的方法可以进一步微调关断漏源电压尖峰和谐振。

一种方法是使用高栅电阻(Rg)来减慢器件开关速度。一种更有效且高效的方法是使用嗡嗡声电路,如图4所示,其中使用低栅电阻。换句话说,使用小的栅电阻来允许SiC器件快速开关,并使用嗡嗡声RC来控制VDS峰值和谐振。器件嗡嗡声电容Cs提供VDS峰值过冲控制,而Cd通过靠近快速开关半桥来最小化功率回路寄生电感。Rs和Rd为VDS谐振提供阻尼。

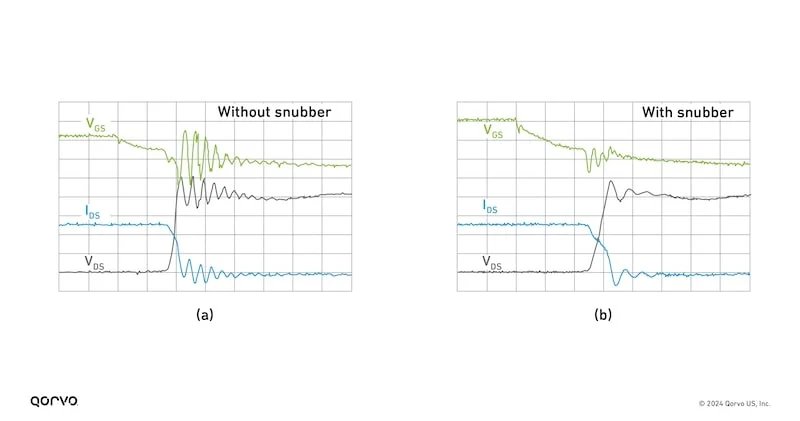

图4

图4一个常见的误解是使用嗡嗡声电路效率低下。对于半桥拓扑结构(通常用于LLC或PSFB等ZVS应用),与使用高栅电阻相比,使用嗡嗡声电路的效率要高得多,因为额外的漏源电容在开启阶段不会产生任何开启损耗。在关断dv/dt阶段,自由轮设备的位移电流将进一步减少已主动关断的设备的关断电流,从而减少电压和电流的重叠,从而大大减少关断损耗(Eoff)。位移电流水平由方程I = C*dv/dt确定。C是等效输出电容,包括器件输出电容(Coss)和并联在器件漏源之间的额外嗡嗡声电容Cs。

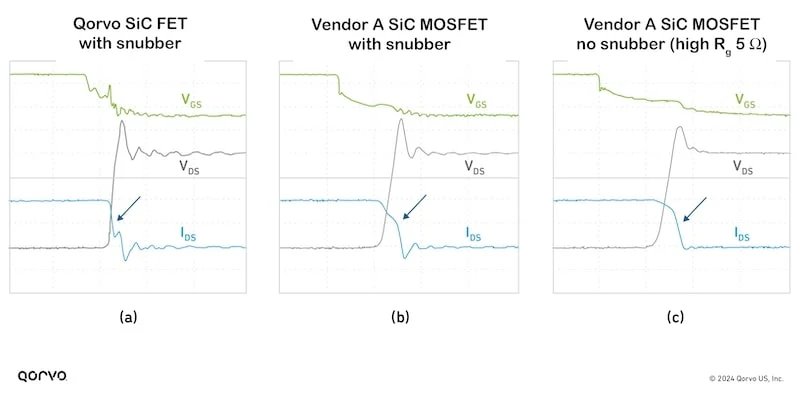

图5

图5具有额外嗡嗡声电容的漏源和高dv/dt(即低栅电阻)时,位移电流将更高。这样,留给活动关断设备与VDS重叠的电流就更少,从而减少关断开关损耗。这种方法允许我们在不牺牲太多器件开关速度的情况下控制VDS的谐振和峰值,而如果我们使用高Rg解决方案,可能更多地使用设备开关速度。图5显示了带有和不带嗡嗡声电路的双脉冲测试关断波形,直观地显示了使用低栅电阻的嗡嗡声电路可以大大减少电压和电流的重叠,从而减少了关断开关损耗。

使用嗡嗡声电路的节省强调了在使用SiC时利用软开关电路结构来最大化效率的重要性。在硬开关设计中,嗡嗡声电路的好处较小,因为在开关周期中从关断周期中存储在Cs中的能量通常作为热量浪费在下一个开启周期中的器件通道中。然而,即使在使用嗡嗡声电路时存在开启损耗的惩罚,总体开关损耗(即开启和关断开关损耗的总和)仍远低于仅使用高栅电阻在满负荷(即设备额定电流)下的情况。

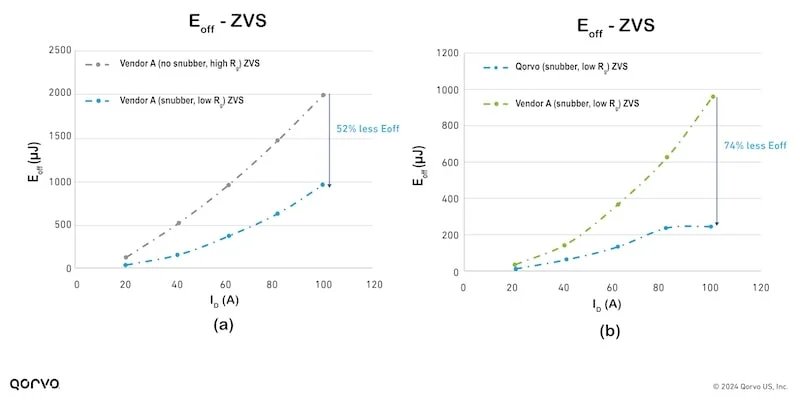

图6

图6参考图5中用800V总线电压和100A负载电流进行的双脉冲测试的波形,图6总结的分析显示,添加嗡嗡声电路可以使来自A供应商的SiC MOSFET模块的损耗减少50%。

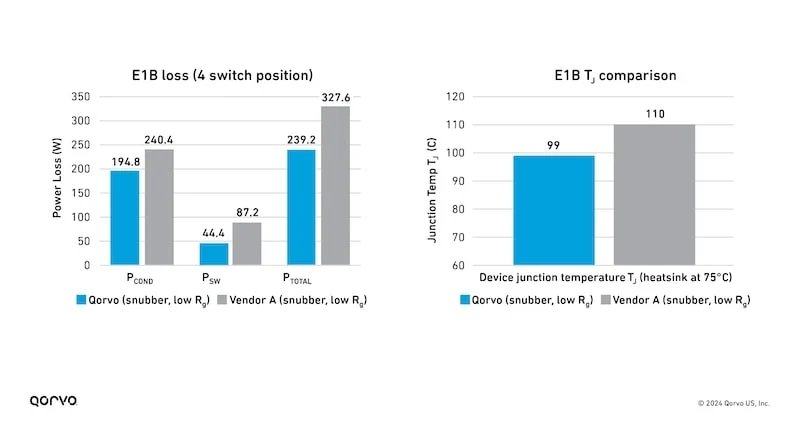

使用Qorvo的基于JFET的器件与嗡嗡声电路相结合,可以额外减少74%的关断开关损耗。这使得可能将开关速率提高三倍,并减小外部被动元件的尺寸。引用50 kW PSFB(相移全桥)的仿真,关断开关损耗减少74%还有助于降低10%的结温(图7)。最终,更好的热性能导致更小的散热器和冷却结构,两者合起来可减小转换器体积。

图7

图7尽管SiC在功率电子设计中相对于硅具有固有优势,但重新评估设备选择和电路拓扑以获得最佳性能。结合嗡嗡声电路和Qorvo SiC串联JFET配置的内在低漏源电阻,快速开关能力可以大大提高ZVS软开关应用的效率和功率密度。

-

电阻

+关注

关注

86文章

5522浏览量

172207 -

MOSFET

+关注

关注

147文章

7189浏览量

213529 -

SiC

+关注

关注

29文章

2832浏览量

62703 -

碳化硅

+关注

关注

25文章

2775浏览量

49105

发布评论请先 登录

相关推荐

用碳化硅(SiC)重新思考软开关效率

用碳化硅(SiC)重新思考软开关效率

评论