我们以T20F256为例来做一个实验。

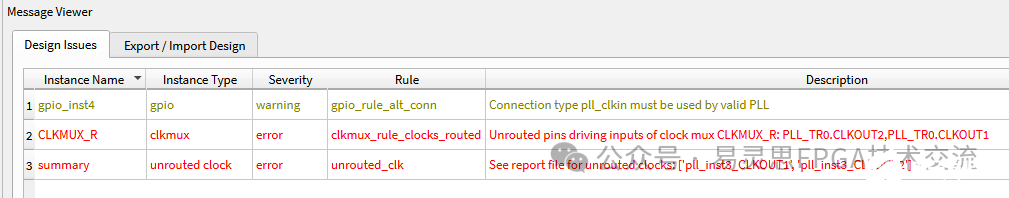

我们把T20F256的5个PLL全部打开,每个PLL的三路输出也全面打开。在生成约束时会报以下错。

Unrouted pins driving inputs of clock muxCLKMUX_R:PLL_TR0.CLKOUT2,PLL_TR0.CLKOUT1.

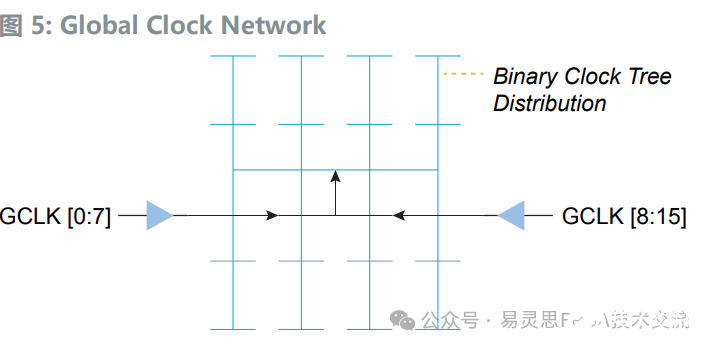

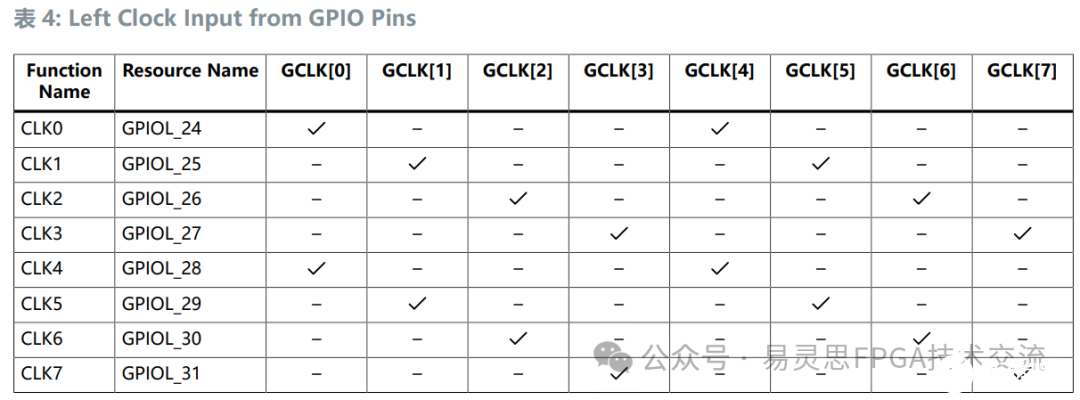

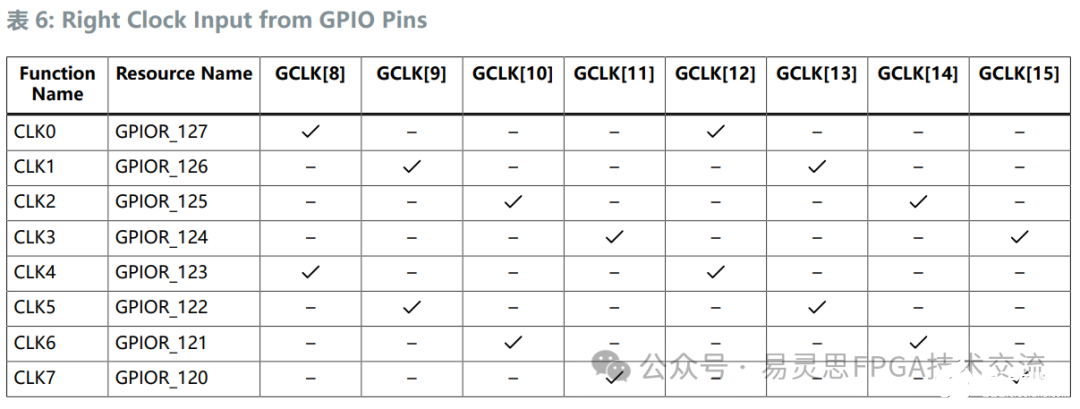

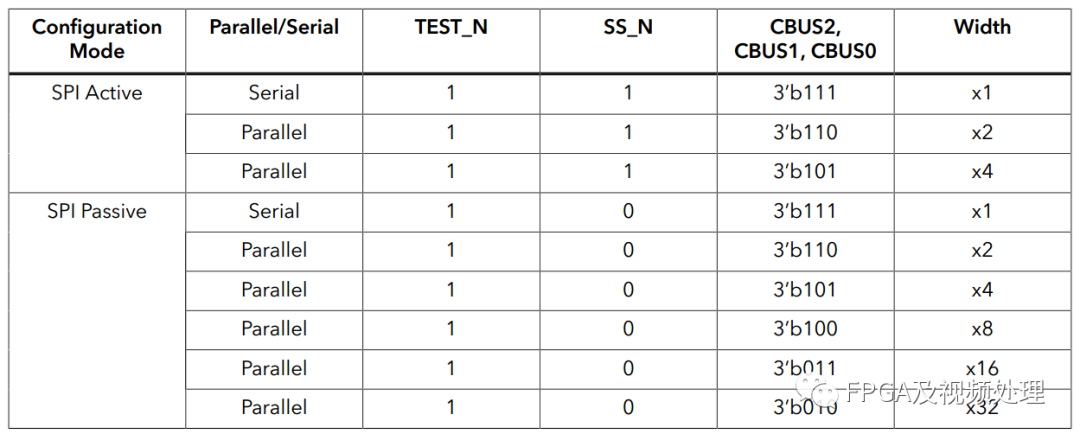

在T20中有16个全局时钟网络GCLK。在芯片的左右两侧各8个。全局时钟管脚或者PLL的输出时钟通过左右两个CLKMUX上全局网络。左侧的PLL(包括PLL_TL0和PLL_TL1)上左侧的CLKMUX_L;右侧的PLL(包括PLL_TR0,PLL_TR1和PLLBR0)上右侧的CLKMUX_R。

当两侧要上全局时钟网络的时钟超过8个时就会报错。

拿上面的例子来分析报“Unrouted pins driving inputs of clock muxCLKMUX_R:PLL_TR0.CLKOUT2,PLL_TR0.CLKOUT1"错误的原因。

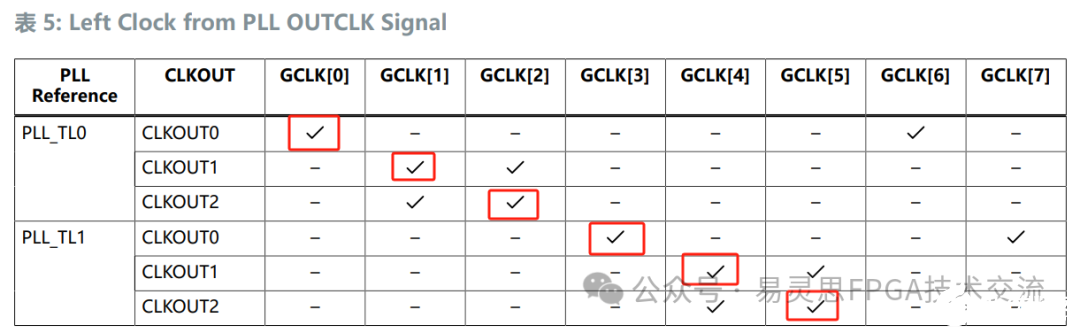

当我们把所有PLL及其输出都打开后,先来分析左侧的CLKMUX_L的使用情况。如下图左侧的GCLK的编号为0~7。而PLL_TL0和PLL_TL1只有6个时钟,那么按红色标注,PLL_TL0.CLKOUT0上GCLK0;PLL_TL0.CLKOUT1上GCLK1;PLL_TL0.CLKOUT2上GCLK2...,按红色的标记是每个时钟都会有GCLK可以走的。

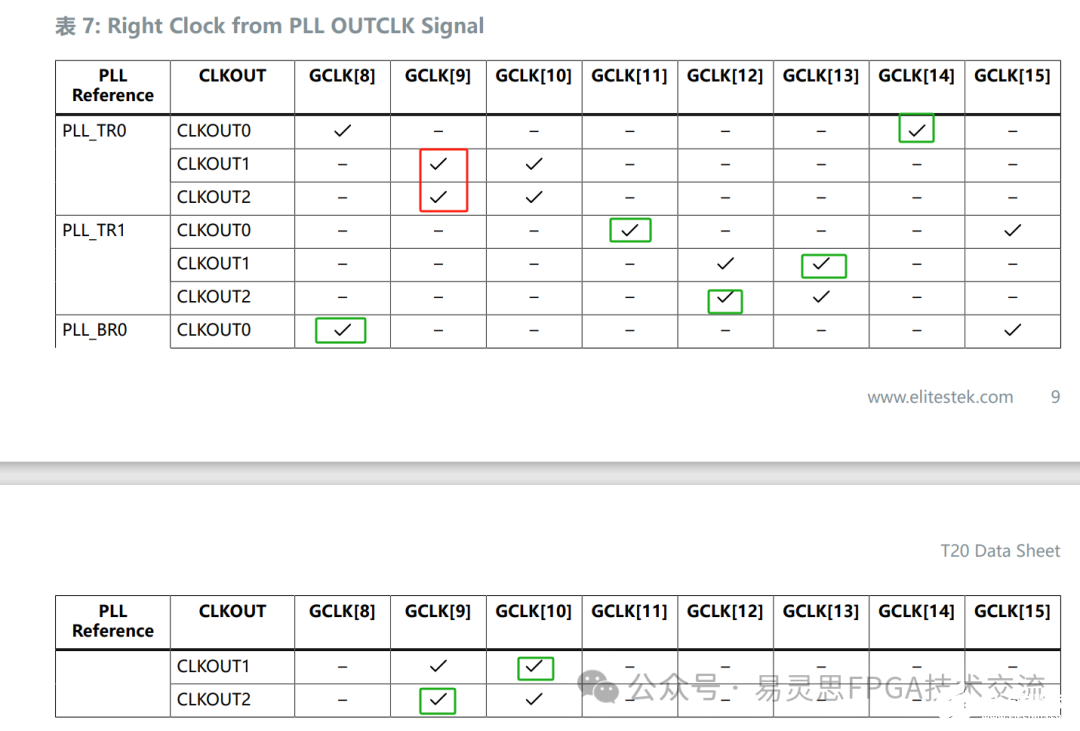

同样的,当我们把所有PLL及其输出都打开后,先来分析右侧的CLKMUX_L的使用情况。如下图左侧的GCLK的编号为8~15。右侧有三个PLL分别为PLL_TR0,PLL_TR1和PLLBR0。按绿色框分配之后,PLL_TR0的CLKOUT1和2是没有网络可以走的。虽然它们可以走GCLK9和GCLK10,但是这两个网络已经被PLL_BR0的CLKOUT1和2占用了。所以就会报出上面的负错误。

可能有人会问。为什么GCLK15及GCLK6,GCLK7都没有用到呢。这是因为我们这里只谈到了PLL的输出时钟,另外还有没有专用时钟管脚没有考虑。如下图。

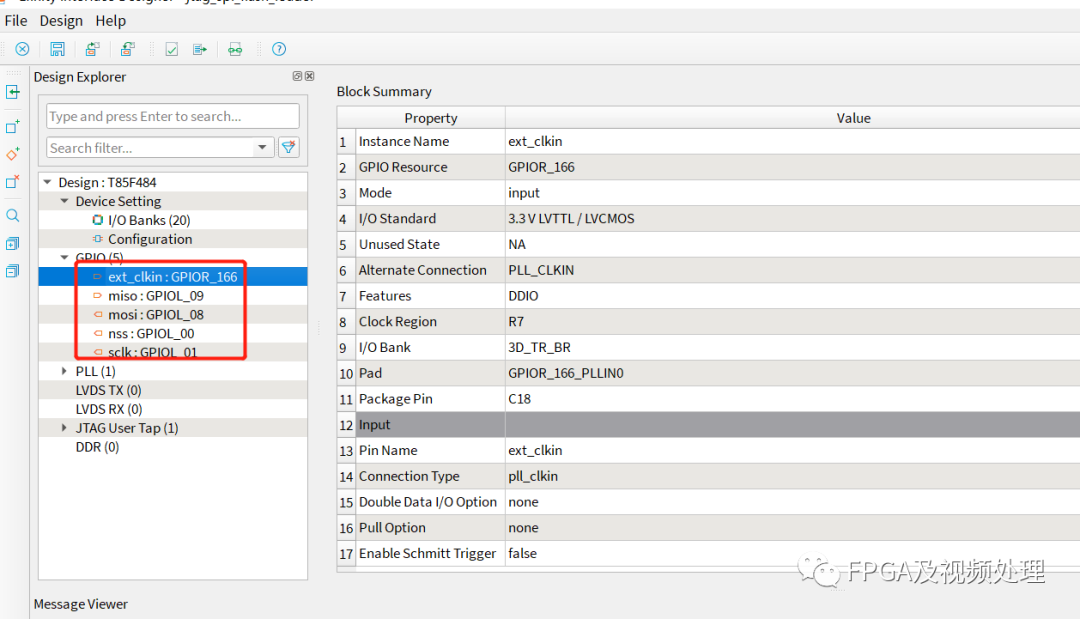

钛金系列的器件也有相似的问题。具体大家可以先看下时钟网线的说明。

-

时钟网络

+关注

关注

0文章

16浏览量

6580 -

易灵思

+关注

关注

5文章

48浏览量

4921

发布评论请先 登录

相关推荐

基于赛灵思FPGA的卷积神经网络实现设计

易灵思推Trion Titanium FPGA,采用 “Quantum™ 计算架构”

易灵思FPGA产品帮助安防领域创新和突破

易灵思IDE更新ROM可以不用全编译了

易灵思FPGA软件更新的节奏,也许能磨出一个好产品

易灵思RAM使用--Update3

易灵思FPGA产品的主要特点

易灵思的时钟网络问题

易灵思的时钟网络问题

评论