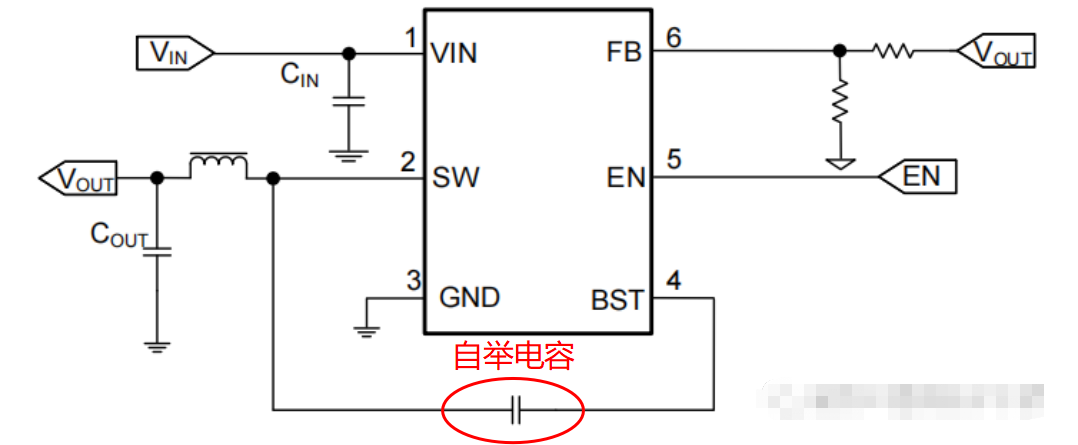

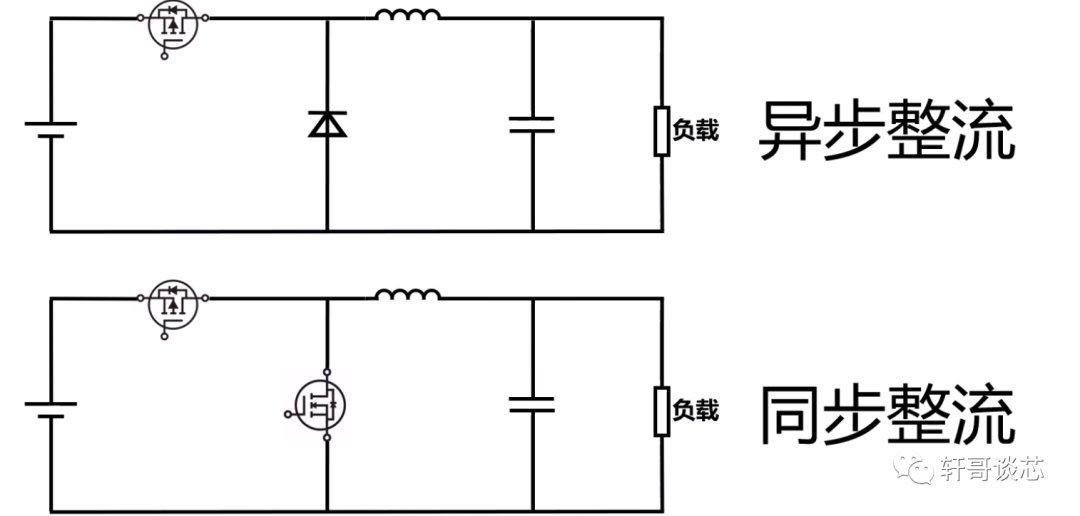

NMOS管的主回路电流方向为D极到S极,导通条件为VGS有一定的压差,即VG-VS>VTH;PMOS管的主回路电流方向为S极到G极,导通条件为VSG有一定的压差,即VS-VG>VTH。故一般把NMOS作为下管,S极接地,只要给G极一定电压即可控制其导通关断;把PMOS作为上管,S极接VIN,G极给个低电压即可导通。当然NMOS管也可作为上管,但需要增加自举驱动电路。

对于一些拓扑,比如Buck、Boost、Buck-Boost这些用NMOS作为上管的拓扑,就没办法直接用刚才说的只给G极一个电平来驱动。假如此时D极接VIN,S极的电压不定,NMOS管截止时为低电平,导通时接近高电平VIN,需要板子上给G极一个更高的电压,但此时板子已无比VIN更高的电平了,那么就可以采用自举驱动电路。

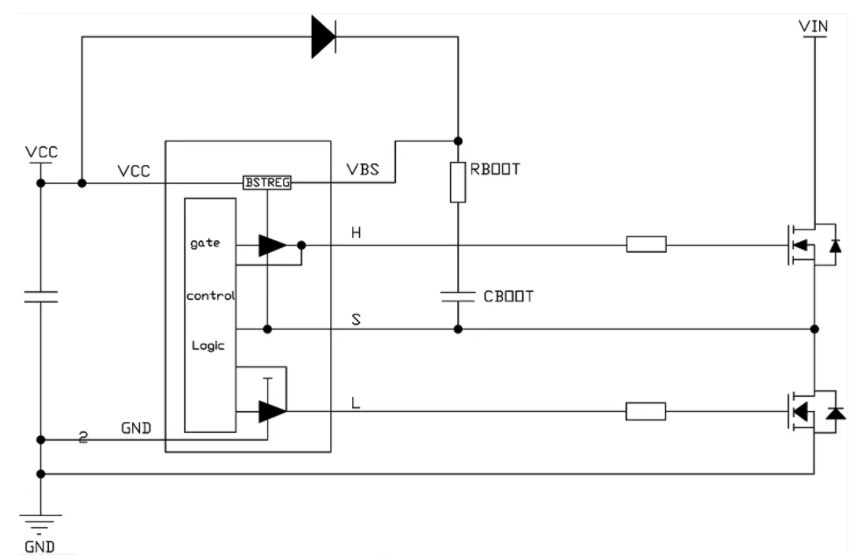

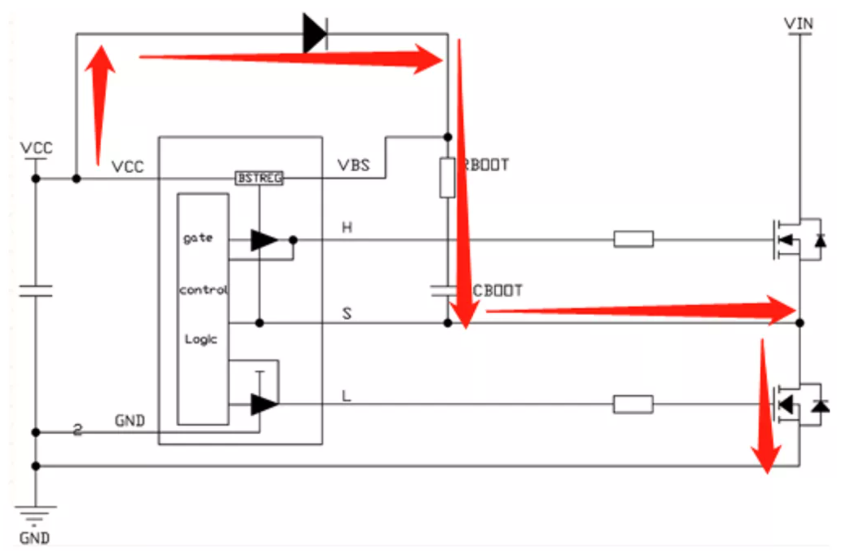

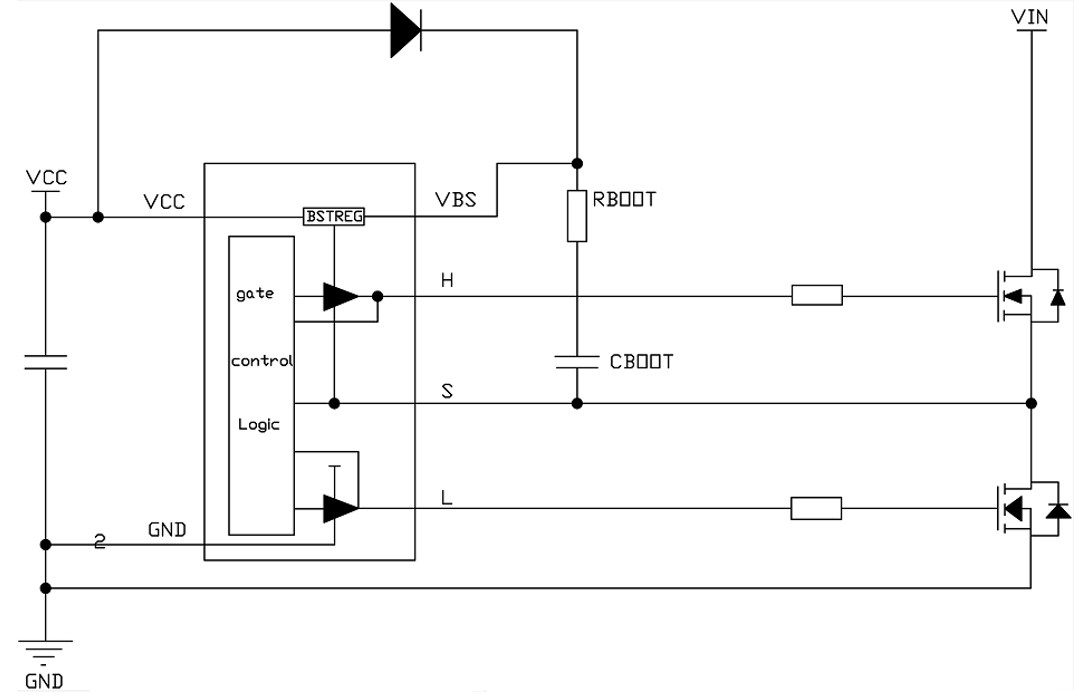

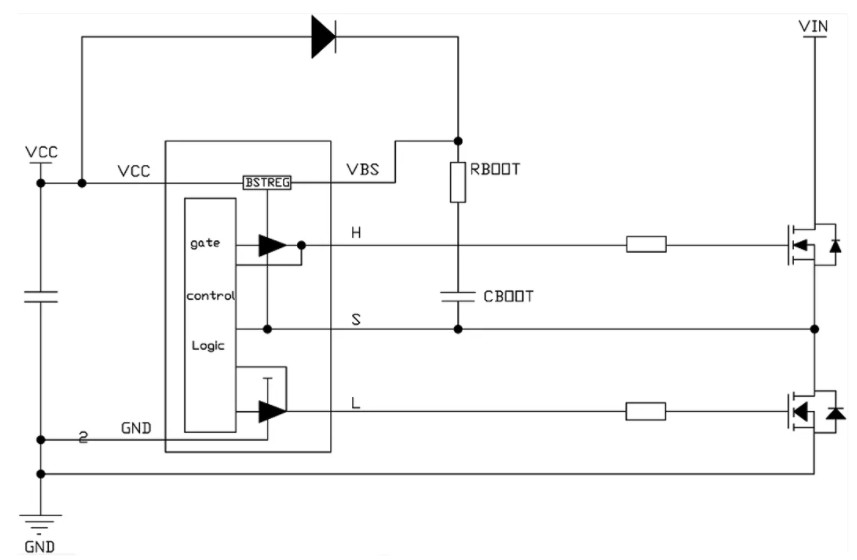

如图为用于驱动上MOS管的电容自举驱动电路。该自举电容通过二极管接到VCC端,下接上MOS管的S极。当驱动电路驱动下MOS管导通时,VCC通过二极管、RBOOT、下MOS管,对CBOOT充电。充电时间为下MOS管的导通时间,我们定为Toff(上MOS管);当下管关断后,驱动电路导通上MOS管,CBOOT的下端电压变为VIN,由于电容两端电压不能突变,所以CBOOT上的电压自然就被举了起来。这样驱动电压才能高过输入电压,就能保持上管持续导通,此时VBOOT的电压通过RBOOT和内部电路放电,放电时间为Ton(上MOS管)。

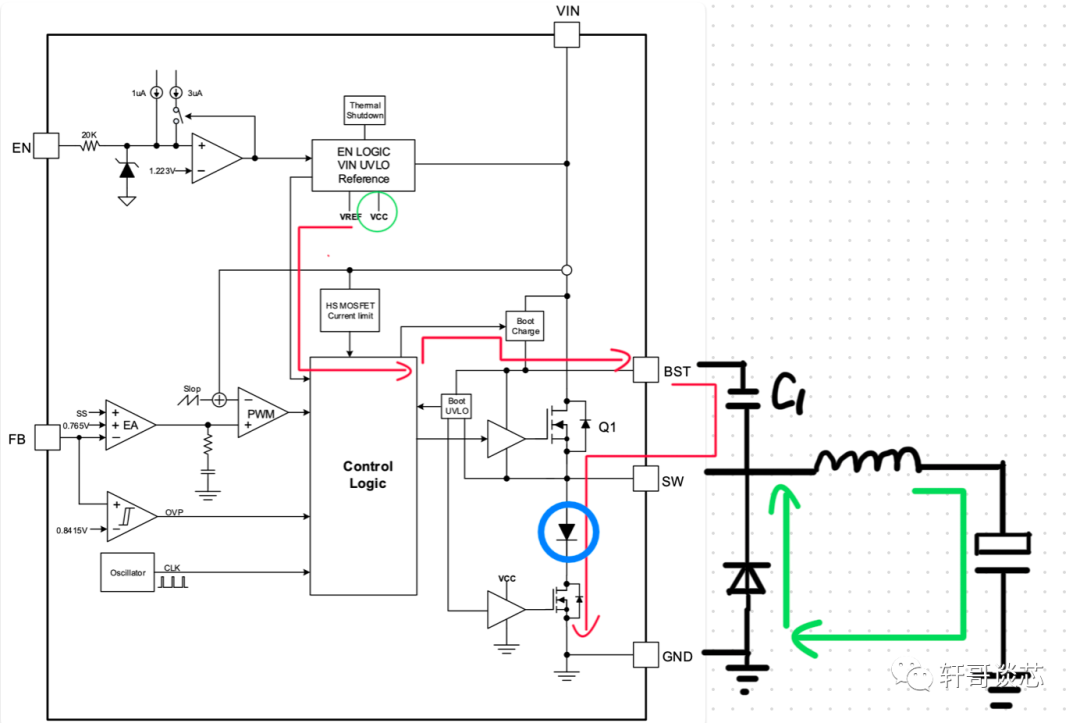

自举电容充电过程如图:

下MOS管导通时开始充电,充电电压对时间的关系如公式一所示:

Vcboot_max = V0 + VCC x [1–exp (-Toff/RC)];

充电电流对时间的关系如公式二所示:

I = CdU/dT = C x △Vcboot/Toff。

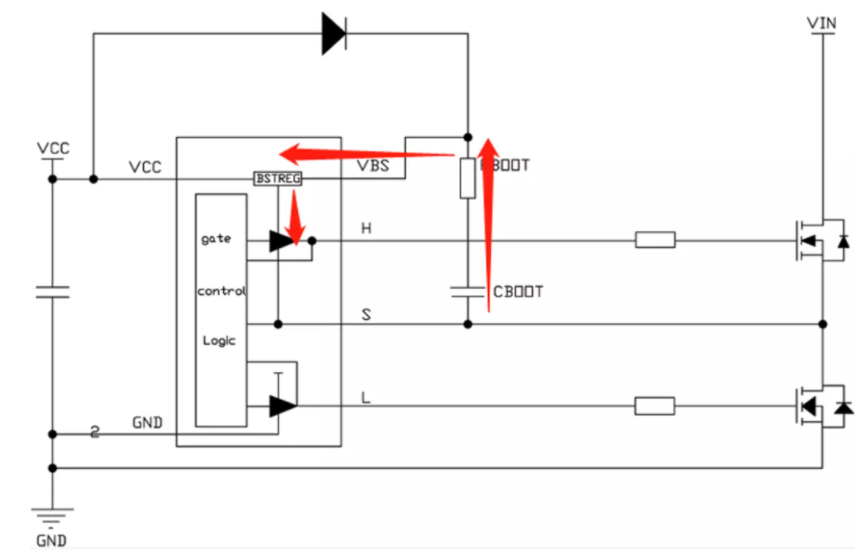

接下来看一下其放电过程:上MOS管导通时开始放电,放电电压对时间的关系如公式三所示:

Vcboot_min = exp [ -Ton/ (Rtotal x C) ] x Vcboot_max

放电电流对时间的关系如公式四所示:

I = CdU/dT = C x △Vcboot/Ton

至此我们已经掌握自举驱动电路的“窍门”。

应该如何正确地选择合适的电容、电阻呢

电容的选型主要基于其耐压值和容量大小。耐压值要大于等于VCC减去二极管和下MOS管的导通电压。驱动电路上有其他功耗器件由该电容供电,所以要求电容上的电压下跌最好不要超过原先值的10%,这样才能保证驱动电压。

由以上限制和公式三可推出需要Ton <= (Rtotal x C)x ln0.9。由该式可知Ton的最大值与自举电容和自举电阻的大小有关。如果容值太小,其两端的电压降会过大,会出现占空比无法展开的情况。但是容值也不能太大,太大的电容会导致最小Toff变大,电容充不满电也会导致占空比无法展开,并且会导致二极管在充电的时候冲击电流过大。

了解完电容后,自举电阻该怎么选型呢?

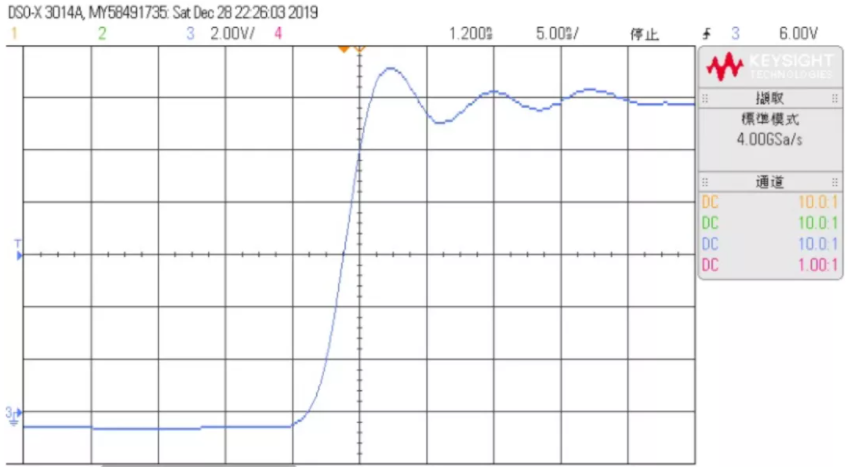

自举电阻的电压等于充电电流乘以其阻值,所以其耐压值要大于最大充电电流乘以其阻值;同样自举电阻的阻值会影响自举电容充电时间,也会影响占空比, R越大,所需充电时间越长。同时自举电阻阻值的增加会降低上MOS管的驱动电压,增加Cgs的充电时间,从而降低上MOS管导通时的电压电流的变化率和SW波尖峰。

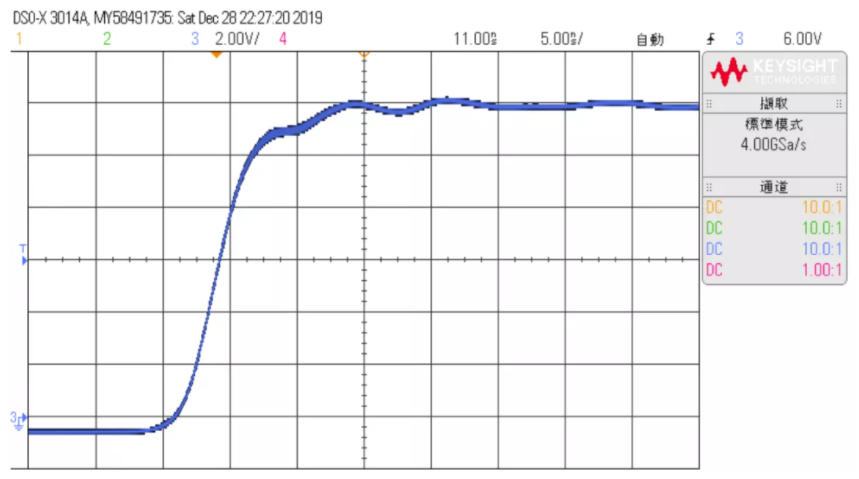

图注:自举电阻为0Ω时,SW的测试波形

将电阻增大到45Ω时,可以明显看出自举电阻越大,SW波上升斜率越小,同时SW的尖峰越小,验证了前面的结论。

图注:电阻增大到45Ω时,SW的测试波形

审核编辑 黄宇

-

NMOS

+关注

关注

3文章

294浏览量

34350 -

自举

+关注

关注

1文章

24浏览量

25113 -

DCDC

+关注

关注

29文章

813浏览量

71263

发布评论请先 登录

相关推荐

DCDC芯片自举电容原理详解

大家能Get到DCDC高端NMOS的自举秘诀吗?

请问如何用NMOS管设计高端输出电路?

关于NMOS高端输出的设计问题

DC-DC上管为什么用NMOS的多

nmos高端驱动自举电路

DC/DC电路自举电容作用

Boot自举电容的充放电过程及应用

DCDC芯片中的自举电容是什么

MPS | DCDC 高端 NMOS 的自举秘诀

DCDC 高端 NMOS 的自举秘诀

DCDC 高端 NMOS 的自举秘诀

评论