业界唯一完整PCIe 7.0 IP,包含控制器、IDE安全模块、PHY和验证IP,可实现高达512 GB/s的数据传输速度;

预先验证的PCIe 7.0控制器和PHY IP在保持信号的完整性的同时,可提供低延迟数据传输,功耗效率比以前的版本最多可提高50%;

新思科技PCIe 7.0 IDE安全模块与控制器IP进行预验证,提供数据保密性、完整性和重放保护,能够有效防止恶意攻击。

该解决方案以新思科技20多年的PCIe IP经验和3000多项成功设计为基础,可提供一条低风险的流片成功之路。

新思科技(Synopsys)近日宣布,推出业界首款完整的PCIe 7.0 IP解决方案,包括控制器、IDE安全模块、PHY和验证IP。该解决方案可以助力芯片制造商满足计算密集型AI工作负载在传输海量数据时对带宽和延迟的严苛要求,同时支持广泛的生态系统互操作性。大型语言模型对算力的需求正在以惊人的速度增长,数据中心需要尽可能快速且可靠地处理数以万亿计的参数。新思科技提供业界唯一一款基于PCIe标准的解决方案,可在x16配置中实现高达512 GB/s双向安全数据传输,从而缓解AI工作负载的数据瓶颈。新思科技在2024年6月12日至13日在圣克拉拉举办的PCI-SIG DevCon大会上展示了这项全球首创技术。

作为全球领先的接口IP提供商,新思科技持续为开发者提供先进工艺节点的最新接口,帮助他们满足计算密集型芯片设计的需求。新思科技PCIe 7.0 IP将为合作伙伴提供一个完整的、基于标准的解决方案,使他们能够尽早开始下一代HPC和AI设计,并加速实现流片成功。

John Koeter

IP市场营销与战略资深副总裁

新思科技

全球首个PCIe 7.0 IP Over Optics技术演示亮相2024 PCI-SIG开发者大会

新思科技在2024年6月12-13日举办的PCI-SIG开发者大会上进行了两项全球首次演示:新思科技PCIe 7.0 PHY IP电光电(E-O-E)发送(TX)转接收(RX),与OpenLight的光子集成电路一起以128 Gb/s的速度运行;新思科技PCIe 7.0控制器IP展示通过FLIT传输成功实现的复杂根到端点连接。此外,新思科技还展示了其PCIe 7.0 IP生态系统与是德科技(Keysight)、Samtec和Teledyne LeCroy等多家合作伙伴的互操作性。

业界首款完整的新思科技 PCIe 7.0 IP解决方案

新思科技PCIe 7.0 IP解决方案包含控制器、IDE安全模块、PHY和验证IP,可降低AI和HPC网络芯片的集成风险。该IP解决方案可满足不断发展的标准,与上一代PCIe相比,可将互连功耗效率提高多达50%,并使相同芯片周长的互连带宽翻倍。新思科技PCIe 7.0控制器IP可实现低延迟、高带宽链路,提供完整的端点到根复合的解决方案,支持后向兼容所需的所有功能。新思科技PCIe 7.0 PHY IP提供出色的信号完整性,每通道速度高达128 Gb/s,并可与新思科技CXL控制器IP解决方案无缝集成。新思科技PCIe 7.0的完整性和数据加密(IDE)安全IP提供保密性、完整性和重放保护,能够有效防止硬件攻击。新思科技PCIe 7.0验证IP和硬件加速验证解决方案提供内置协议检查以及控制器和PHY器件的多种配置,以加速验证收敛。

新思科技面向HPC领域的广泛IP组合

新思科技可为HPC SoC设计提供业界广泛的高速接口IP产品组合,包括PCIe 7.0、1.6T/800G以太网、CXL和HBM的完整、安全的IP解决方案。基于新思科技广泛的互操作性测试、全面的技术支持和强大的IP性能,开发者可以加速流片成功和投产。

全球行业领导者支持PCIe 7.0用于AI数据中心设备

新思科技PCIe 7.0 IP解决方案可满足市场对先进、可信互连技术的急迫需求,助力开发团队满怀信心地加速启动下一代HPC和AI芯片设计,已经得到了全球多家领先科技公司的大力支持。

加速数据中心各个互连环节,包括PCIe,对于满足大规模AI集群性能需求可谓至关重要。新思科技PCIe 7.0 IP与英特尔未来一代产品的结合,将为系统架构师提供数据中心严苛工作负载所需的带宽和无缝的生态系统集成。

Debendra Das Sharma

高级研究员兼首席I/O架构师

英特尔

PCIe作为我们专用连接解决方案组合的核心,已被众多超大规模计算提供商和AI平台提供商广泛采用。PCIe 7.0可将带宽翻倍并降低延迟,这对于快速发展的生成式AI和HPC应用而言至关重要。感谢新思科技能够支持PCIe 7.0生态系统,持续推动前沿技术发展。

Casey Morrison

首席产品官

Astera Labs

PCIe技术对于数据中心服务器I/O的发展、性能和互操作性至关重要。采用新思科技PCIe 7.0 IP,Enfabrica的加速计算Fabric芯片能够面向下一代AI计算设备提供高度集成、可靠和高性能的扩展/横向互连。

Rochan Sankar

总裁兼首席执行官

Enfabrica

为满足深度学习和AI工作负载,超大规模计算提供商需要可靠的行业标准接口,以提供高性能、低延迟的连接。借助Kandou的PCIe重定时器和新思科技PCIe 7.0 IP,系统开发者将能够实现高带宽、安全的连接,这对数据密集型、延迟敏感型工作负载至关重要。

Amin Shokrollahi

首席执行官

Kandou

数据中心解耦合和不断发展的服务器架构需要广泛的生态系统互操作性,以便高效地传输海量数据。XConn的PCIe/CXL交换机和新思科技PCIe 7.0 IP将成为这些新兴架构应用的关键,加速推动高性能、符合标准的系统实现大规模部署。

Gerry Fan

首席执行官

XConn

为训练大语言模型,我们必须比以往更快地处理海量数据。PCIe 7.0支持扩展高带宽、安全和低延迟的互连,以满足未来的AI数据需求。Rivos基于RISC-V的AI系统解决方案采用了新思科技PCIe 7.0 IP等先进接口,助力系统架构师能够实现高效、高性能和安全的连接,这对于为AI工作负载提供全新一代芯片至关重要。

Mark Hayter

创始人兼首席战略官

Rivos

Microchip致力于推动HPC和AI技术的发展。将新思科技先进的PCIe 7.0 IP解决方案整合于我们的下一代PCIe产品线,将使系统架构师能够把显著增强的带宽和效率用于先进的HPC和AI应用中。

Bob Divivier

数据中心解决方案事业部副总裁

Microchip

凭借高带宽和低延迟,PCIe 7.0将为AI数据中心设备带来性能上的巨大提升。为了推动生态系统建设并让开发者获得早期测试,Samtec和新思科技在2024 PCI-SIG开发者大会进行了互操作性测试,展示Samtec的NovaRay I/O面板安装电缆系统、NovaRay电缆系统和新思科技PCIe 7.0 IP的长距离性能结果。Samtec广泛的高性能互连系统产品线可提供出色的热效率、小尺寸、极高的数据速率和密度以及信号完整性优化性能,能够应对当前和下一代数据中心应用的瓶颈挑战。

Matthew Burns

技术营销全球总监

Samtec

上市时间和更多资源

新思科技PCIe 7.0控制器(带IDE安全功能)和PHY IP面向先进工艺,计划于2025年初全面上市。新思科技PCIe 7.0验证IP现已上市。

-

芯片

+关注

关注

456文章

51157浏览量

426574 -

PCIe

+关注

关注

15文章

1258浏览量

83063 -

新思科技

+关注

关注

5文章

807浏览量

50405

原文标题:新思科技推出业界首款PCIe 7.0 IP解决方案,加速万亿参数领域的芯片设计

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

新思科技推出超以太网与UALink IP解决方案

新思科技推出业界首款连接大规模AI加速器集群的超以太网和UALink IP 解决方案

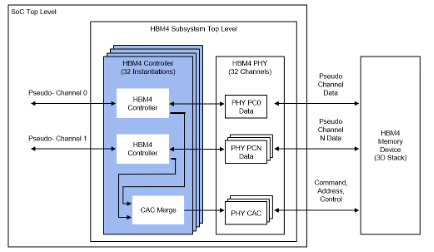

Rambus推出业界首款HBM4控制器IP

Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

Cadence展示完整的PCIe 7.0 IP解决方案

新思科技推出业界首款PCIe 7.0 IP解决方案

新思科技推出业界首款PCIe 7.0 IP解决方案

评论