来源:中国科大微电子学院

近日,中国科大微电子学院石媛媛教授课题组设计并实现了一种直接在硅片上制造大规模单层(Monolayer, ML)单晶 MoS₂高性能晶体管阵列的集成方法,相关研究成功入选2024 Symposium on VLSI Technology and Circuits(以下简称VLSI Symposium)。

VLSI Symposium是集成电路领域最具盛名的三大国际顶级会议(IEDM, ISSCC和VLSI)之一,今年VLSI Symposium于6月16日至20日在美国夏威夷举行,会议汇集了世界各地行业和学术界的工程师和科学家,讨论超大规模集成电路制造和设计中的挑战和难题。

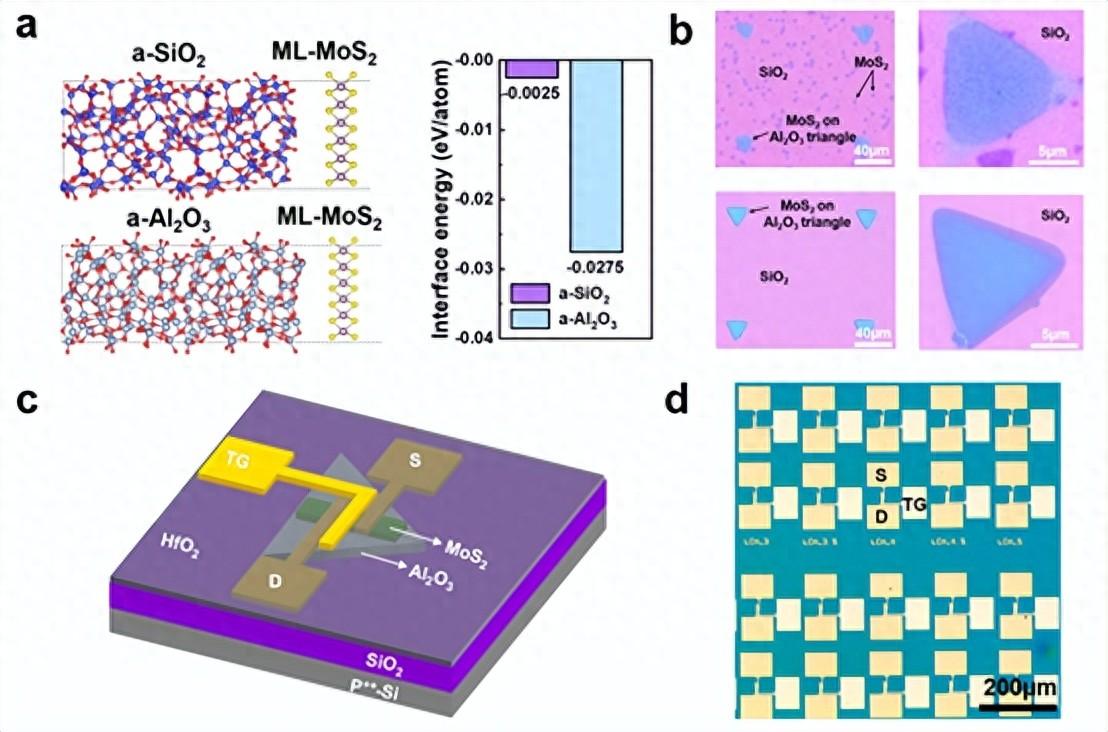

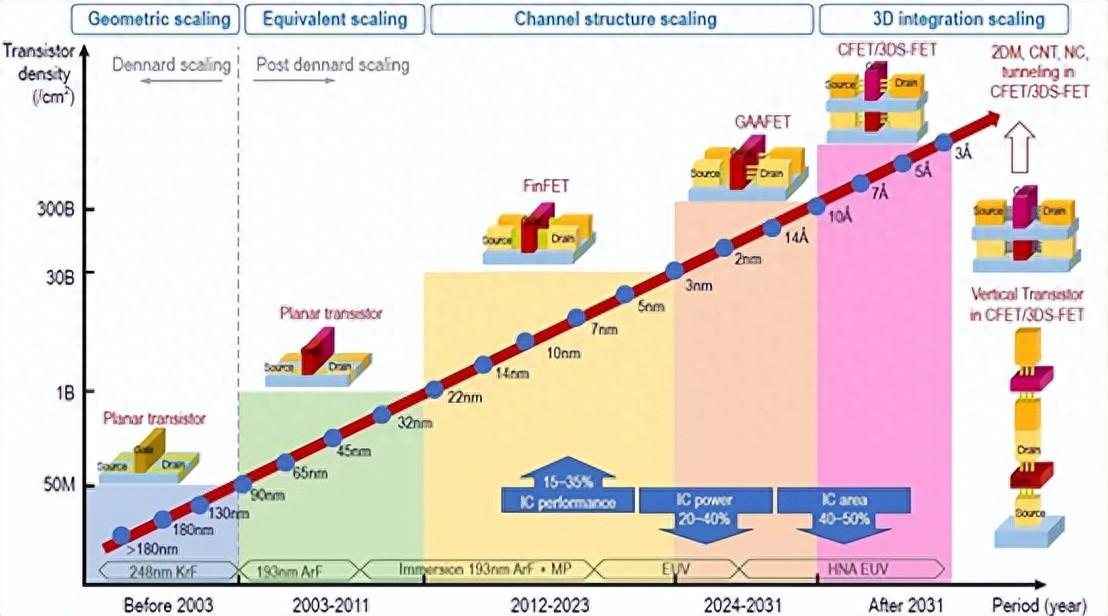

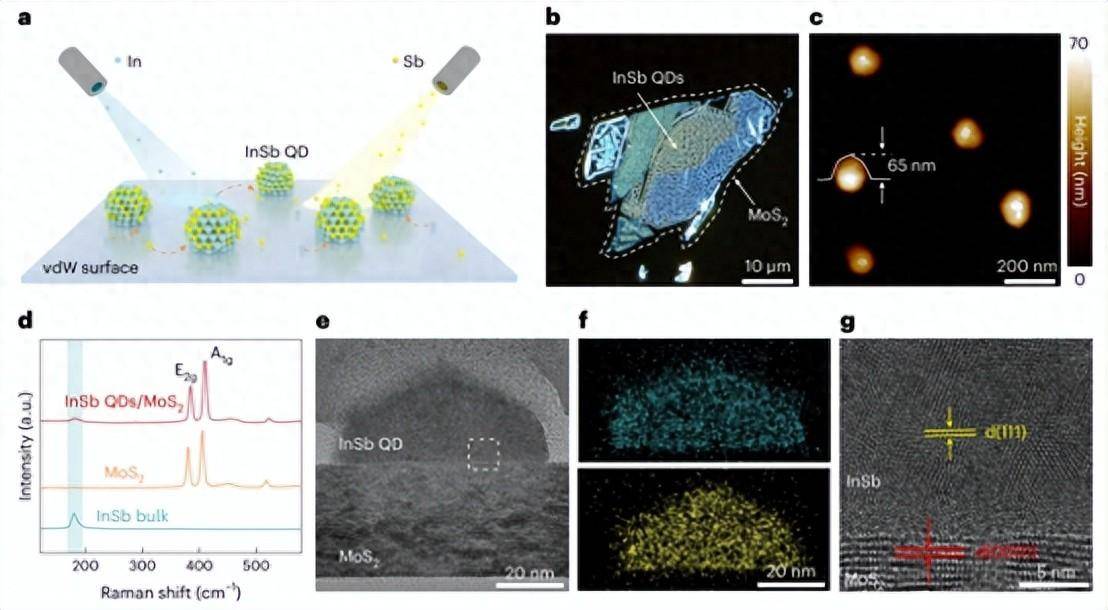

随着先进工艺节点的持续推进,二维半导体晶体管的研发有助于延续摩尔定律,持续推进晶体管特征尺寸的微缩,不断提升芯片算力。在基于二维半导体沟道的晶体管中,沟道的质量至关重要,常规直接生长方法沉积的多晶沟道存在大量晶界,导致器件较低的载流子迁移率。而通过单晶衬底外延生长的二维半导体成本较大,制备器件所必需的转移过程也会带来污染与缺陷等。此研究受单晶衬底外延生长的启发,在硅片上设计了非晶Al₂O₃三角形类台阶图案,同时利用二维半导体在非晶Al₂O₃和SiO₂上吸附能的差异性(图1a),促进单晶ML-MoS₂阵列的选择性区域生长(Selective area growth, SAG)(图1b)。同时在SAG单晶ML-MoS2上直接(无需转移过程)进行了大规模双栅晶体管的制备(图1c-d)。

图1. SAG MoS₂ 晶体管概念与集成。(a) DFT计算二维半导体MoS₂在不同非晶衬底上的吸附能;(b) 图案化工艺辅助的SAG单晶ML-MoS₂;基于SAG ML-MoS₂ 沟道的双栅晶体管 (c) 三维示意图和 (d) 阵列显微镜图

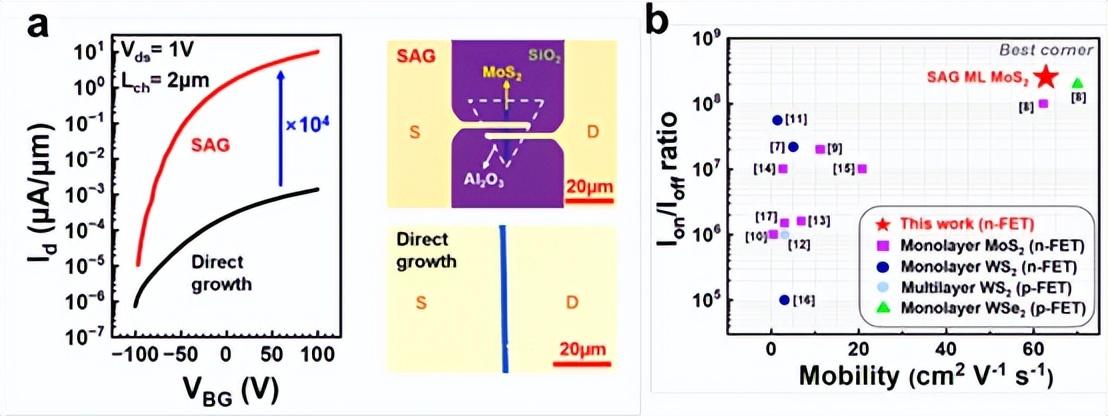

图2. SAG MoS₂ 晶体管性能。(a) 基于SAG ML-MoS₂沟道的背栅晶体管与直接生长制备的MoS₂背栅晶体管转移特性曲线对比;(b) 本工作中SAG ML-MoS₂晶体管性能与相关文献对比的基准图

基于SAG ML-MoS₂沟道的背栅晶体管开态电流较直接生长的MoS₂沟道晶体管提升10⁴倍,亚阈值摆幅减小2倍(图2)。晶体管阵列中器件最大载流子迁移率可达62.8 cm²/Vs,电流开关比>10⁸。此晶体管性能随着点缺陷、栅介质等的调控可以进一步提升。该研究成果以“Single-crystalline monolayer MoS₂ arrays based high-performance transistors via selective-area CVD growth directly on silicon wafers”为题在大会作报告。

中国科大微电子学院硕士研究生朱贵旭为该论文第一作者,石媛媛教授为通讯作者,该项研究得到了国家自然科学基金的资助,同时也得到了中国科大何力新教授、曾华凌教授和安徽大学宋东升教授课题组的合作与支持。

审核编辑 黄宇

-

半导体

+关注

关注

335文章

28334浏览量

229963 -

晶体管

+关注

关注

77文章

9909浏览量

140156

发布评论请先 登录

相关推荐

纳芯微与复旦大学微电子学院ICD实验室合作研发新突破,多项成果亮相JSSC

芯海科技携手复旦微电子学院研发成果亮相国际权威期刊IEEE JSSC

纳芯微与复旦大学微电子学院合作研发成果亮相JSSC

雷钰团队及合作者在二维材料缺陷调控及生物应用等领域取得新进展

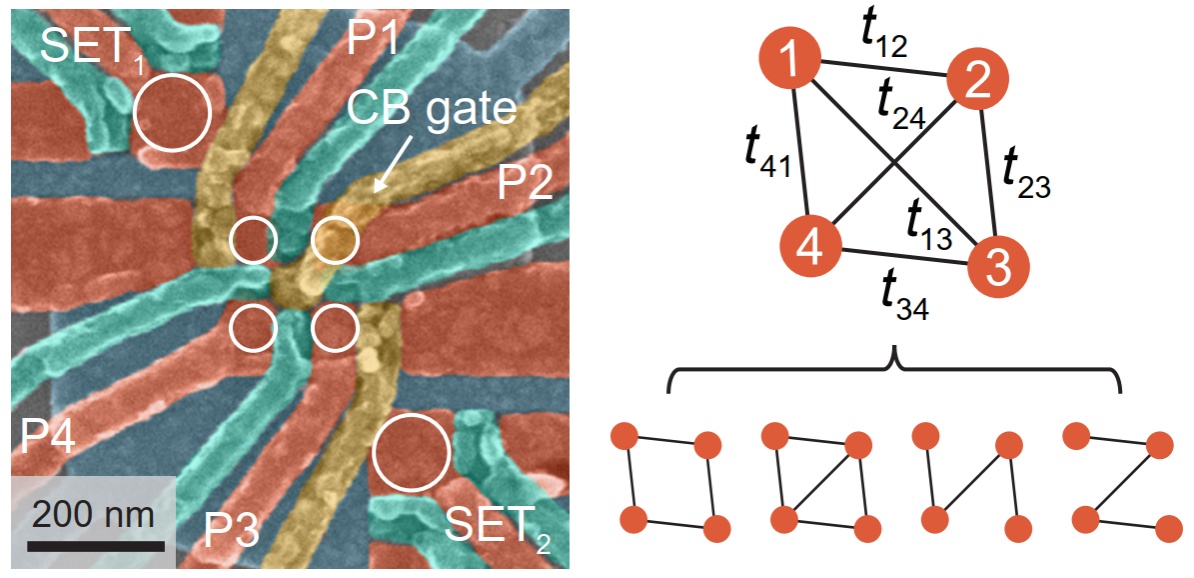

中国科大实现耦合高度可调的二维硅基量子点阵列

半导体研究所在量子点异质外延技术上取得重大突破

中国半导体的镜鉴之路

二维材料 ALD 的晶圆级集成变化

微电子所在《中国科学:国家科学评论》发表关于先进CMOS集成电路新结构晶体管的综述论文

VLSI Symposium 中国科大微电子学院在高性能二维半导体晶体管领域取得重要进展

VLSI Symposium 中国科大微电子学院在高性能二维半导体晶体管领域取得重要进展

评论