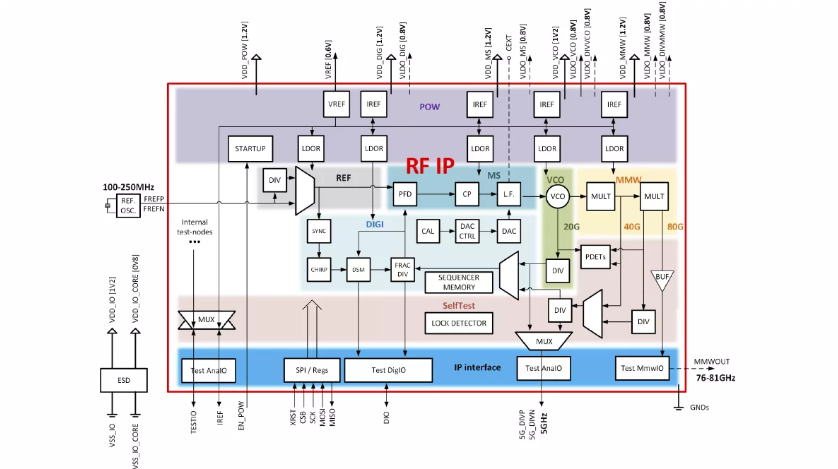

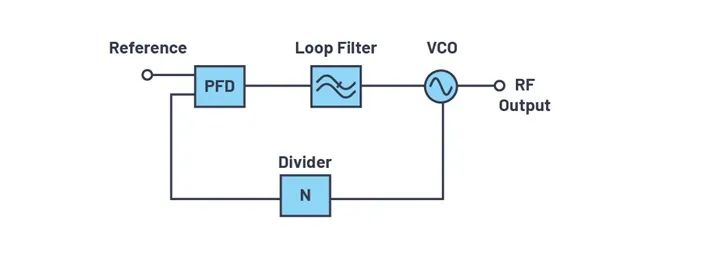

高级驾驶辅助系统(ADAS)应用依赖于多项技术,而在77GHz至81GHz范围内工作的汽车雷达便是其中关键。锁相环(PLL)是该雷达的核心部件,可以为雷达发射器和接收器(收发器)提供本地振荡器(LO)频率。为了在雷达检测和通信中发挥效用,PLL必须兼具高频率精度和低相位噪声。

CoreHW是一家成立于2013年的芬兰芯片设计企业,不久前利用新思科技RFIC设计流程以及格芯(GF)22FDX工艺技术,成功研发了具有出色相位噪声性能的80GHz毫米波PLL(MMW PLL),非常适合自动驾驶、5G/6G通信、物联网和其他超高速连接系统,以及航空航天等应用。

本文将详细介绍先进RFIC设计所面临的挑战,并探讨现代开放式RFIC设计和验证流程如何加速流片成功。

RFIC设计流程助力加速实现出色芯片设计

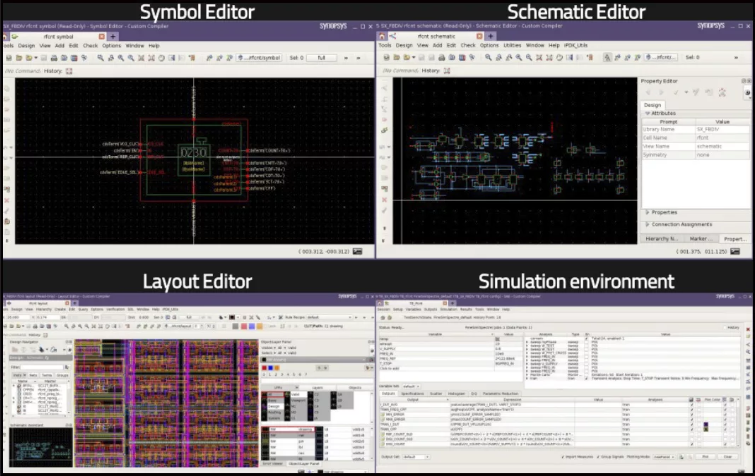

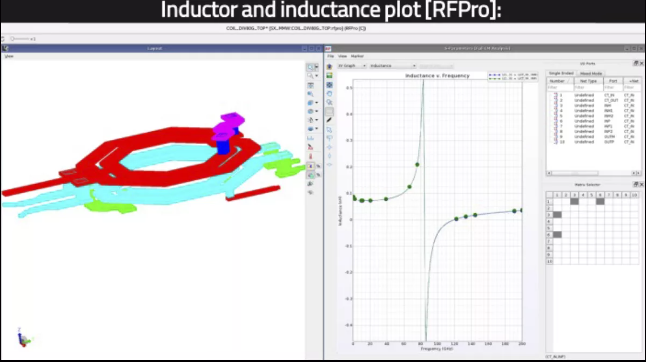

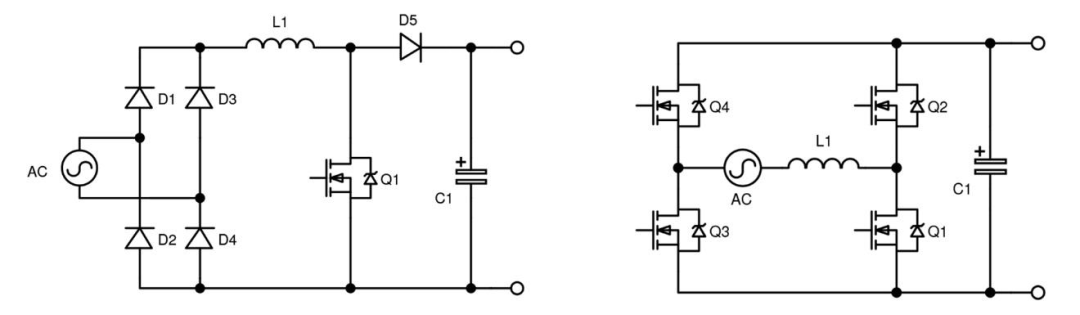

在设计先进的射频和毫米波IC时,开发者依然面临着复杂的设计要求。除了芯片本身的复杂性外,RFIC流程还需要反复迭代和大量手动操作。另外,模拟和射频团队往往还要面对紧迫的上市时间压力。为了满足这些要求,同时得到准确、可重复的结果,并提高设计效率、缩短验证周期,CoreHW在格芯22FDX工艺技术基础上采用了新思科技RFIC设计流程。该流程通过了GF 22FDX认证,以新思科技Custom Compiler设计环境为基础,并结合了新思科技PrimeSim下一代电路仿真技术的统一工作流程,可用于全定制模拟、定制数字和混合信号IC设计。格芯针对这些工具提供了工艺设计套件(PDK)。此外,该流程还与是德科技PathWave RFPro电磁(EM)分析工具相集成,使开发者能够轻松进行交互式EM电路协同仿真,以进一步微调和优化设计。

我们正基于新思科技Custom Compiler和PrimeSim电路仿真器,并借助是德科技RFPro电磁仿真器,积极部署射频和毫米波设计流程,致力于为开发者加速预测性流程,助其开发高品质、全定制的射频和毫米波混合信号IC。

Tomi Pekka Takalo

首席执行官

CoreHW

简而言之,新思科技RFIC设计流程提供了一整套从前端到后端的工具集,将帮助开发者高效取得优异成果,推动行业进入设计与验证射频和毫米波IC的新时代。

-

锁相环

+关注

关注

35文章

584浏览量

87763 -

芯片设计

+关注

关注

15文章

1019浏览量

54893 -

pll

+关注

关注

6文章

776浏览量

135155 -

毫米波

+关注

关注

21文章

1923浏览量

64803

原文标题:80GHz毫米波PLL是如何研发成功的?

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

RFIC设计经理、RFIC设计

RFIC设计经理/RFIC设计(上海。广东)

ADS可以进行RFIC设计吗?

央企研发中心--RFIC工程师+ASIC工程师=薪酬面议

RFIC设计和应用介绍【回映分享】

新思科技联合Ansys、是德科技共同开发RFIC设计产品

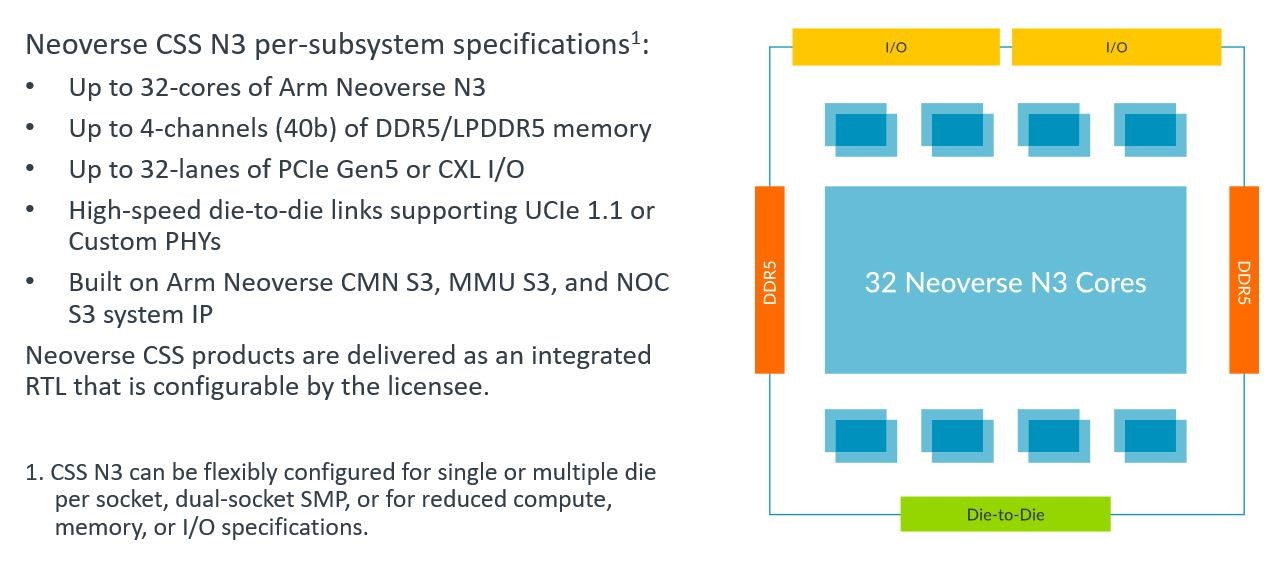

Arm Neoverse CSS N3 助力快速实现出色能效

RFIC设计流程助力加速实现出色芯片设计

RFIC设计流程助力加速实现出色芯片设计

评论