2024年07月09日,一站式定制芯片及IP供应商——灿芯半导体(上海)股份有限公司(灿芯股份,688691)宣布成功研发出一款通用高性能小数分频锁相环(fractional-N PLL)IP,支持24bits高精度小数分频,最高输出频率4.5Ghz,另外还支持扩频时钟(SSC)功能,可以为客户提供多功能的小数分频 PLL解决方案。

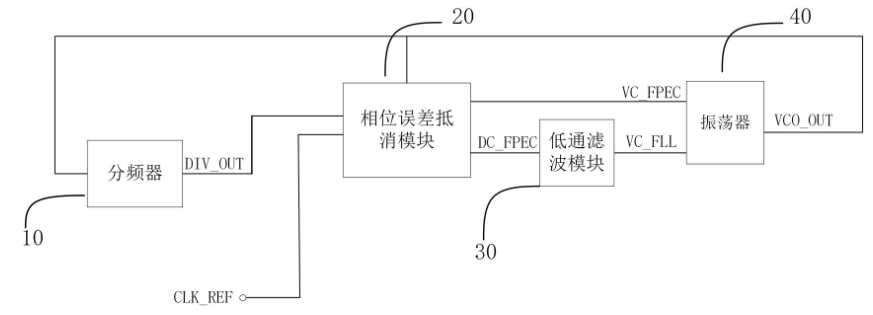

PLL电路一般用于产生输出频率,输出频率值与PLL的参考输入频率呈倍数关系。小数分频PLL通过频率乘法比例的小数值,实现更精确的输出频率控制,从而提供更高精度和准确度的输出频率。

SSC发生器是在一定频率范围内调制时钟信号频率的电路,将时钟信号的能量扩展到更大的频率范围上。这种调制技术可以减少电磁干扰(EMI),提高信号的完整性。随着集成电路工艺节点的不断减小,市场对这类支持SSC功能的小数分频PLL IP需求也在不断增加,这种设计具有减少电磁干扰、提高时钟稳定性和降低功耗的优点。

“基于十多年IP设计开发的成功经验,灿芯半导体成功研发出通用高性能小数分频PLL IP。该PLL IP支持较宽的输入输出频率范围,具有优异的抖动性能,可以应用于任何时钟应用场景,特别是混合噪声信号的SoC环境。这款高性能小数分频 PLL IP已经成功在28nm工艺上流片,并且成功完成测试芯片验证,目前这款高性能小数分频PLL IP已经被多家客户使用。

关于灿芯半导体

灿芯半导体(上海)股份有限公司(灿芯股份,688691)是一家提供一站式定制芯片及IP的高新技术企业,为客户提供从芯片架构设计到芯片成品的一站式服务,致力于为客户提供高价值、差异化的解决方案。

灿芯半导体的“YOU”系列IP和YouSiP(Silicon-Platform)解决方案,经过了完整的流片测试验证。其中YouSiP方案可以为系统公司、无厂半导体公司提供原型设计参考,从而快速赢得市场。

灿芯半导体成立于2008年,总部位于中国上海,为客户提供全方位的优质服务。

-

锁相环

+关注

关注

35文章

590浏览量

88033 -

pll

+关注

关注

6文章

785浏览量

135457 -

灿芯半导体

+关注

关注

0文章

54浏览量

12712

原文标题:灿芯半导体发布通用高性能小数分频锁相环IP及相关解决方案

文章出处:【微信号:BriteSemi,微信公众号:灿芯半导体BriteSemi】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

锁相环是什么意思

可编程晶振的锁相环原理

灿芯半导体ICCAD 2024精彩回顾

锁相环PLL在无线电中的应用 锁相环PLL与模拟电路的结合

锁相环PLL的工作原理 锁相环PLL应用领域

CDC509高性能、低偏斜、低抖动、锁相环(PLL)时钟驱动器数据表

简述锁相环的基本结构

锁相环和锁相放大器的区别

锁相环相位噪声的影响因素

锁相环的工作原理和应用场景

AD9694输入时钟低于337.5MHz时,serdes锁相环无法锁定怎么解决?

倍频器与锁相环的区别

锁相环的基本原理和主要作用

深圳市九天睿芯科技有限公司获得一项锁相环专利

灿芯半导体推出通用高性能小数分频锁相环IP

灿芯半导体推出通用高性能小数分频锁相环IP

评论