- 串联电路

- 晶体负载电容

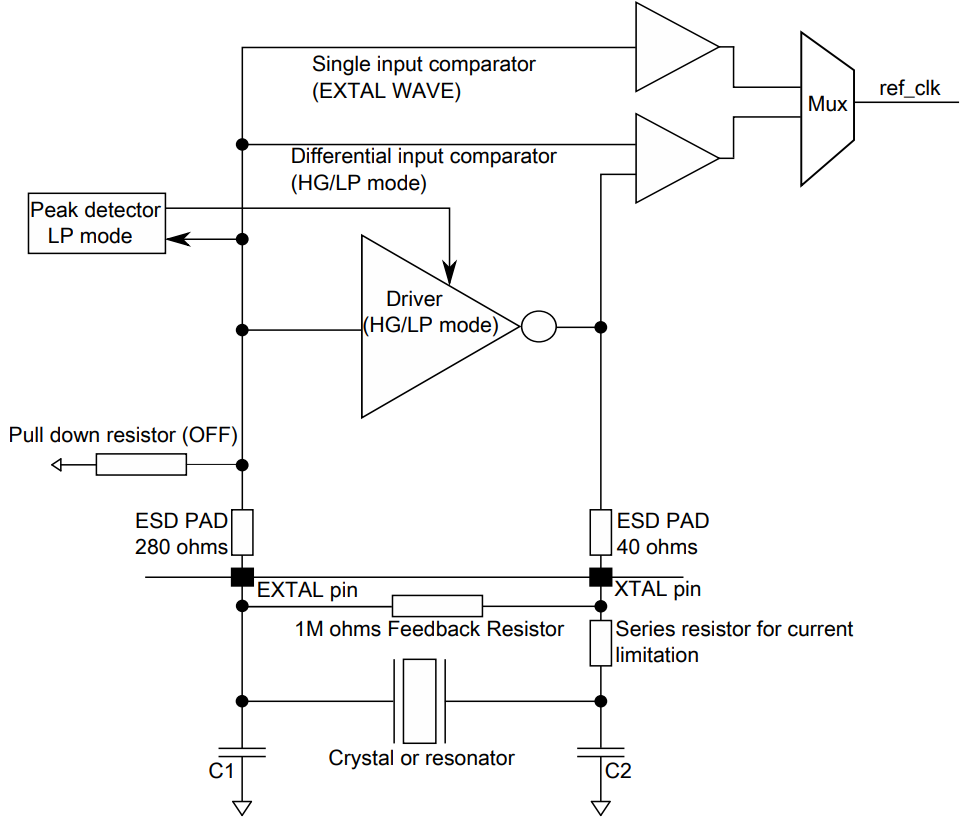

- 并联电路

- 驱动电平

- 频率与振荡模式

- 设计注意事项

- 负阻抗

在这篇文章中,我们将介绍振荡器设计的基础知识以及晶体振荡器电路设计的 7个关键组件中的每一个。

什么是晶体振荡器电路?(振荡器电路基础知识)

晶体振荡器电路由放大器和反馈网络组成。反馈网络从放大器获取特定输出,并将其发送回放大器输入。拉出来的时候看起来很简单......

...但是,我们越深入,就越复杂。抓紧!

晶体振荡器电路要有效运行,必须满足两个关键条件:

- 环路功率增益必须等于一致。

- 环路相移必须等于0、2Pi、4Pi等弧度。

直接回到放大器输入端的功率必须足以为放大器输入和振荡器良率提供电源,并克服电路损耗。

振荡器的精确频率由振荡器电路内的环路相移决定。相移的任何变化都会导致频率的变化。减少净相移的最佳方法之一是在反馈回路中使用石英晶体。我们在TROQ生产的所有晶体都包括石英晶体(石英晶体振荡器)。

当振荡器的反馈回路中使用石英晶体时,振荡器的频率输出实际上是自我调节的。石英晶体产生满足相环要求的电抗。

现在您已经对晶体振荡器设计的基础知识有了扎实的了解,让我们来看看晶体振荡器电路设计的关键考虑因素。

晶体振荡器电路设计的 7个关键考虑因素

- 串联电路

串联电路晶体振荡器使用设计用于在其固有谐振频率下工作的晶体。对于此类电路,反馈回路中不需要电容器。串联谐振器电路是相当基本的,通常使用,因为它们的元件数量很少。

串联电路可以提供通过晶体以外的反馈路径。这意味着即使在晶体故障期间,电路也可能继续以主观频率振荡。

串联电路的一个重大缺点是,如果系统需要修改,则无法调整输出频率。串联谐振晶体设计为首选的频率、容差和稳定性,并且无需调整选项即可保持。

2.负载电容

负载电容在振荡器电路设计中起着至关重要的作用。在下一个设计考虑因素中,您将看到负载电容重要性的示例,但现在,让我们仔细看看负载电容本身。

负载电容被描述为在电路中的晶体端子上测量或计算的电容量。

当涉及到串联电路时,晶体电路的连接点之间没有电容。因此,电路中没有负载电容。对于并联电路来说,情况就不同了。

要确定并联电路中的负载电容(在设计考虑因素 #3中描述)

在这个等式中,LC1和LC2表示负载电容。Cs是电路杂散电容(通常在 3到 5 pF之间)。

3.并联电路

并联谐振振荡器电路由晶体制成,该晶体设计用于在特定负载电容下工作。这导致晶体振荡器的工作频率高于串联谐振频率,但低于真正的并联谐振频率。

要完成此类电路中的反馈回路,必须设计穿过晶体的路由。如果晶体发生故障,电路将不再振荡。

那么决定振荡器频率的负载电容从何而来呢?该电路实际上使用一个单独的逆变器,在反馈回路中有两个电容器,包括负载电容。如果负载电容发生变化,振荡器产生的频率也会发生变化。

话虽如此,重要的是要注意,如果需要,这种电路类型并不适合轻松调整频率。此外,还需要精确的频率控制和负载电容的精确规格。

例如,如果将容量为20 pF的20 MHz晶体放置在评估值为30 pF的电路中,则晶体将低于指定值。但是,如果电路的评估值仅为10 pF,则频率将高于指定值。

4.驱动电平

驱动电平是晶体在运行时消耗的功率。功率通常以毫瓦或微瓦来描述。

石英晶体被指定为可以影响振荡器频率和工作模式的最大驱动电平值。与晶体振荡器供应商合作,确定石英振荡器可以维持的最大驱动电平非常重要。

那么,如果晶体振荡器超过最大驱动电平会发生什么?它可能导致振荡器:

- 变得不稳定

- 加快老龄化速度

- 在关键应用中导致通信丢失或时序丢失

要计算晶体的驱动电平,请使用以下公式(基本上只是欧姆定律,但用于功率):

驱动电平 =(Irms2x R)

在这个方程中,Irms是通过石英晶体的测量 RMS电流,R是石英晶体的最大电阻。

要测量晶体振荡器电路的实际驱动电平,可以在其中插入一个电阻器。然后可以读取电阻两端的压降,以计算电流和功率耗散。当然,请确保在此测量后移除电阻器。

5.频率与模式

晶体振荡器的频率可能受到物理尺寸的限制。有时,这可能是某些应用程序的长度和宽度。其他时候,它可能是石英晶体本身的厚度。石英晶圆越薄,频率就越高。石英晶圆的厚度通常变得太薄,无法在30 MHz左右进行加工。

如果您需要频率高于极限频率的振荡器,则可以利用基频。基频被定义为“由整个物体的振荡产生的最低频率,与更高频率的谐波不同。如果晶体的基频为10 MHz,它也可以在基频的3倍、5倍、7倍等处振荡。因此,振荡器可以在 30 MHz、50 MHz、70 MHz等频率下振荡。这些是频率的泛音。

当需要使用泛音频率时,晶体制造商必须将晶体设计为在所需的泛音频率下工作。切勿尝试订购基波模式晶体,然后在另一个所需的泛音下操作它,因为基波晶体和泛音晶体的晶体制造工艺不同。

6.设计注意事项

为了获得最佳振荡器电路操作,应遵循一些设计注意事项。始终建议的一件事是避免在电路中并联走线。这样做可以减少杂散电容。所有迹线应尽可能短,以防止耦合。使用接地平面保持组件隔离也有助于解决这个问题。

7.负阻抗

振荡器的设计必须能够增强负阻抗以获得最佳性能。负阻抗通常也称为振荡余量。

以下是帮助您计算振荡器电路中负阻抗的六个简单步骤:

- 临时安装一个与晶体串联的可变电阻器。

- 将电阻器设置为最低设置(接近零欧姆)。

- 启动振荡器上电并监控示波器上的输出。

- 在持续监控示波器信号时,使用可变电阻器开始增加电路中的电阻。

- 一旦振荡停止,请注意可变电阻器以确定欧姆值。

- 将晶体的最大电阻值(由供应商指定)与步骤 5中测量的欧姆值相加。

计算出的总值是负阻抗或振荡余量。对于一般经验法则,负阻抗应至少为晶体指定最大电阻值的 5倍,才可靠。

石英晶体振荡器,让您的下一个项目更进一步

近20年来以来,TROQ创捷电子一直在设计和制造晶体振荡器。浏览我们的全系列频率产品,找到适合您项目需求的产品,或立即联系我们的工程师以了解更多信息。

-

振荡器

+关注

关注

28文章

3832浏览量

139033 -

晶振

+关注

关注

34文章

2859浏览量

68004 -

振荡器电路

+关注

关注

1文章

43浏览量

16594 -

晶体振荡器

+关注

关注

9文章

617浏览量

29105

发布评论请先 登录

相关推荐

这7个关键因素,您在设计LDO必须重点考虑资料下载

无源晶振的选型理念 无源晶振的EMC电路设计

超详细!晶振电路设计的7个关键因素,小白也能变高手!

超详细!晶振电路设计的7个关键因素,小白也能变高手!

评论