一、RS锁存器的定义

RS锁存器,全称Reset-Set Latch,是一种具有两个稳定状态(双稳态)的电路,能够存储一位二进制数据。这两个稳定状态分别对应着二进制数0和1,用于表示电路的两种不同逻辑状态。RS锁存器通过接收外部输入信号(Reset和Set)来控制其状态的转换,并在输入信号消失后,保持已转换的稳定状态(在通电状态下)。

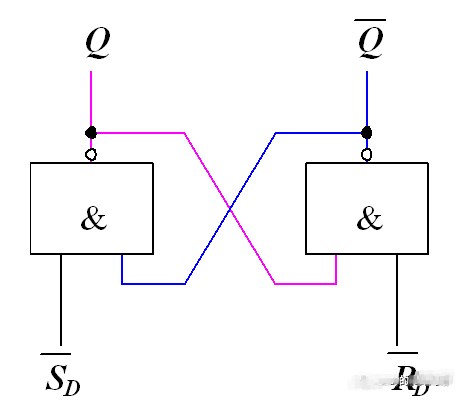

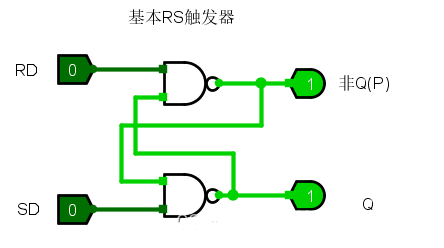

1、基本RS锁存器

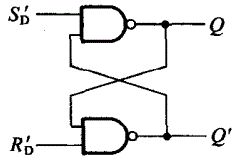

最简单的触发器是基本RS触发器,基本RS锁存器可以由两个与非门构成,电路如下:

基本RS锁存器由电平触发,并且有一个重要的约束条件:/SD和/RD不能同时为零。即:/SD+/RD=1。

2、门控SR锁存器

门控SR 锁存器(或时钟控制 SR 锁存器)只能在存在使能信号以及所需输入时更改其输出状态。因此,它也称为 同步 SR 锁存器 。相反,可以在应用其所需输入条件时立即改变其状态的锁存器称为异步锁存器。

这意味着输入仅在锁存器启用时才影响锁存器;否则,即使应用输入,输出状态也保持不变。换句话说,当 ENABLE 信号为高电平时,锁存器处于活动状态;当 ENABLE 信号为低电平时,锁存器处于非活动状态。该启用信号用作时钟脉冲。

因此,门控SR锁存器也称为时钟SR触发器或同步SR锁存器。由于它仅在时钟脉冲为高电平时响应输入,因此也称为电平触发触发器。门控 SR 锁存器或时钟控制 SR 触发器的逻辑电路如下所示。

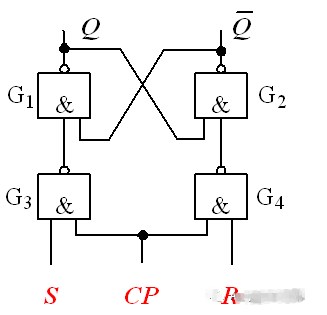

3、同步RS锁存器

许多时候,我们希望触发器只有在时钟来临时,输出状态改变,其它时候,触发器维持,因为这样做可以让多个电路单元的状态同时得以改变,这个时钟,我们称为同步时钟。

如下图所示,将基本RS锁存器的输入端分别经过一个与非门作为钟控信号。就变成了同步RS锁存器。

同步RS锁存器与基本RS锁存器的不同之处在于,只有时钟CP=1的时候,输出状态才能被改变。但是,同步锁存器也具有一个约束条件,就是当CP=1时,S和R不能同时为1。

此外,同步RS锁存器还有一个不足之处在于:当CP=1时,S和R若多次改变,每次改变都会影响输出。这种现象,称为空翻现象。

二、RS锁存器的作用

RS锁存器在数字系统中具有多种重要作用,主要包括以下几个方面:

数据存储:RS锁存器最基本的作用就是存储一位二进制数据。在数字电路中,经常需要临时存储某些数据以便后续处理,RS锁存器正是实现这一功能的关键元件。

状态保持:RS锁存器能够在输入信号消失后,保持已转换的稳定状态,这一特性使得它在需要保持电路状态不变的场合中尤为重要。

信号同步:在复杂的数字系统中,各个部分可能需要同步工作。RS锁存器可以作为同步信号的一部分,通过控制其状态的转换来实现不同部分之间的同步。

逻辑控制:RS锁存器还可以作为逻辑控制元件,通过与其他电路元件的组合,实现复杂的逻辑控制功能。

三、RS锁存器的功能

RS锁存器的功能主要体现在以下几个方面:

置位与复位功能:

置位(Set):当Set(S)输入为高电平时,无论Reset(R)输入为何种电平,RS锁存器都将输出Q置为1(同时Q'输出为0),表示电路处于“置位”状态。

复位(Reset):当Reset(R)输入为高电平时,无论Set(S)输入为何种电平,RS锁存器都将输出Q置为0(同时Q'输出为1),表示电路处于“复位”状态。

保持功能:当Set(S)和Reset(R)输入均为低电平时,RS锁存器将保持当前的状态不变。这一特性使得RS锁存器能够在没有外部输入信号的情况下,长期保持其存储的数据。

竞争与冒险避免:在数字电路中,由于信号传输的延迟和干扰等因素,可能会出现竞争与冒险现象。RS锁存器通过其双稳态特性,能够在一定程度上避免竞争与冒险的发生,提高电路的稳定性和可靠性。

四、SR锁存器的工作原理

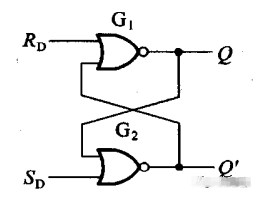

图为与非门构成的SR锁存器

图为或非门构成SR锁存器

上面两图分别是使用两个与非门和两个或非门组成的SR锁存器,本文以图两个或非门组成的SR锁存器进行功能分析。

当SD=1,RD=0时,或非门G2一端以SD作为输入,故G2输出低电平,G2和RD作为G1的输入,所以G1输出为高电平,此时SR锁存器输出Q端为高电平,Q'为低电平。Q的次态与Q的现态无关,输出端Q均为高电平,故SD被称为置数端。

当SD=0,RD=1时,因为或非门G1的RD端输入高电平,所以G1输出端输出低电平,或非门G2输入均为低电平,则Q非为高电平,故SR锁存器Q输出为低电平,Q'输出高电平。Q的次态与Q现态无关,输出端均为低电平,RD被称为SR锁存器清零端。

当SD=0,RD=0,Q的现态为0时,则Q'的次态为高电平,进而推出或非门G1的输出为低电平,所以Q的次态为0;当Q的现态为1时,则或非门G2的输出为0,或非门G1将RD和或非门G2输出作为输入,所以或非门G1输出高电平,即Q的次态为高电平,由此可知,Q端的次态和现态保持相同,所以当SD与RD端输入数据均无效时,SR锁存器具有保持功能。

五、RS锁存器的实现方式

RS锁存器可以通过多种逻辑门电路实现,其中最常见的是使用与非门(NAND Gate)或或非门(NOR Gate)构建。以下分别介绍这两种实现方式:

1. 使用与非门实现RS锁存器

使用两个与非门可以实现一个基本的RS锁存器。两个与非门的输入和输出相互交叉耦合,形成正反馈回路。当Set(S)输入为高电平时,通过与非门的逻辑运算,可以使得输出Q置为1;同样地,当Reset(R)输入为高电平时,可以使得输出Q置为0。当Set(S)和Reset(R)输入均为低电平时,由于正反馈回路的存在,RS锁存器将保持当前的状态不变。

2. 使用或非门实现RS锁存器

与与非门类似,两个或非门也可以构建成RS锁存器。但是需要注意的是,由于或非门的逻辑特性与与非门相反(全0输出1,有1输出0),因此在使用或非门实现RS锁存器时,需要调整输入信号的逻辑电平。具体来说,当Set(S)输入为低电平时(相当于与非门中的高电平),通过或非门的逻辑运算,可以使得输出Q置为1;同样地,当Reset(R)输入为低电平时(相当于与非门中的高电平),可以使得输出Q置为0。当Set(S)和Reset(R)输入均为高电平时(相当于与非门中的低电平),RS锁存器将保持当前的状态不变。

六、RS锁存器的应用实例

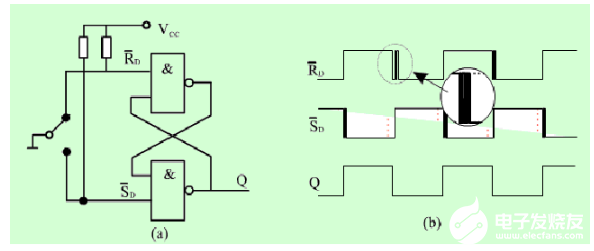

基本RS锁存器虽然电路相当简单,但有很广泛的使用,下图是在时序电路是广泛使用的消除抖动开关电路的使用的例子。

我们通常使用的开关一般是机械触点实现开关的合上和断开的,由于机械触点存在弹性,这就决定了当它们合上的时候,产生反弹的问题,反映在电信号上将出现不规则的脉冲信号,若要求合上输出就为低电平时,就须通过电路加以改进,此图就实现变个功能。

RS锁存器由于其简单性和实用性,在数字系统中有着广泛的应用。以下列举几个典型的应用实例:

寄存器:在CPU中,寄存器是存储临时数据的重要部件。RS锁存器可以作为寄存器的一部分,用于存储和保持CPU执行指令时所需的临时数据。

触发器:触发器是数字电路中用于存储和传输信息的基本单元。RS锁存器可以作为触发器的一种基础形式,虽然在实际应用中更常见到的是D触发器、JK触发器或T触发器等,但RS锁存器为这些更复杂的触发器提供了基础概念。通过添加时钟信号或其他控制逻辑,RS锁存器可以被扩展为这些更高级的触发器。

开关电路:在数字电子学中,RS锁存器经常被用作简单的开关电路。例如,在控制系统中,它可以根据外部信号(如按钮或传感器)的输入来开启或关闭某个电路。当Set信号被激活时,电路打开;当Reset信号被激活时,电路关闭。

同步控制:在需要精确同步的电路中,RS锁存器可以用来确保不同部分的操作按照预定的顺序进行。通过精心设计的时钟信号和触发逻辑,可以确保RS锁存器在适当的时候接收Set或Reset信号,从而控制电路的同步操作。

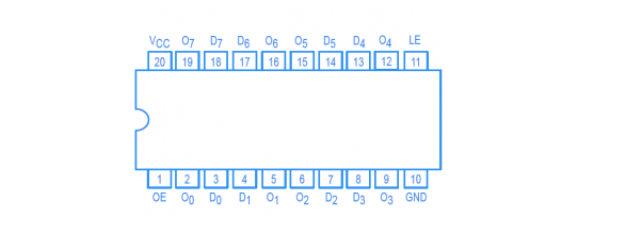

数据锁存:在数据传输过程中,为了防止数据丢失或错误,经常需要使用锁存器来暂存数据。RS锁存器可以在接收到有效数据后,将其锁存起来,直到下一个时钟周期或触发信号到来时才释放数据。这种特性使得RS锁存器在数据通信和存储系统中非常有用。

状态机:在状态机设计中,RS锁存器可以用来表示系统的不同状态。通过控制Set和Reset信号的输入,可以切换系统的状态,并根据当前状态执行相应的操作。虽然在实际应用中,更复杂的触发器(如JK触发器)可能更适合用于状态机设计,但RS锁存器作为基础概念仍然具有重要的指导意义。

故障检测和恢复:在数字系统中,故障检测和恢复是非常重要的功能。RS锁存器可以通过其双稳态特性来检测电路中的故障,并在检测到故障时通过Reset信号将系统恢复到初始状态。这种机制有助于提高系统的可靠性和稳定性。

时序电路中的时序元素:在时序电路中,RS锁存器可以作为时序元素之一,与其他时序元素(如时钟、计数器等)协同工作,实现复杂的时序控制功能。例如,在计数器设计中,RS锁存器可以用来存储计数器的当前值,并在需要时将其输出到外部电路。

-

时钟

+关注

关注

11文章

1758浏览量

132180 -

锁存器

+关注

关注

8文章

918浏览量

41772 -

RS触发器

+关注

关注

3文章

101浏览量

18122

发布评论请先 登录

相关推荐

RS锁存器的工作原理和应用实例

RS锁存器的工作原理和应用实例

评论