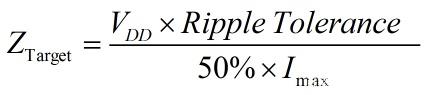

在数字系统中,PCB 的电源分配网络 (power delivery network,即 PDN) 需要在较宽的频率范围内具有较低的阻抗值,以确保在数字器件运行时,电压波动能保持在较低水平。决定 PDN 阻抗的因素有很多,不单单是数字处理器中用于稳定功率输出的电容器。在工作频率达到 GHz 级别的先进系统中,PDN 阻抗不仅受到电容器的影响,还有很多因素会决定 PDN 阻抗,即便在非常高的频率下也是如此。

1

SMD 电容器(频率范围最高 10-100 MHz)

电容器是决定 PDN 阻抗并确保稳定功率传输的主要元件。大多数市售电容器都能保持较低的 PDN 阻抗,但它们所能达到的频率范围取决于以下多种因素:

电容值

ESR 和 ESL 值(决定自谐振频率)

SMD 电容器外壳尺寸

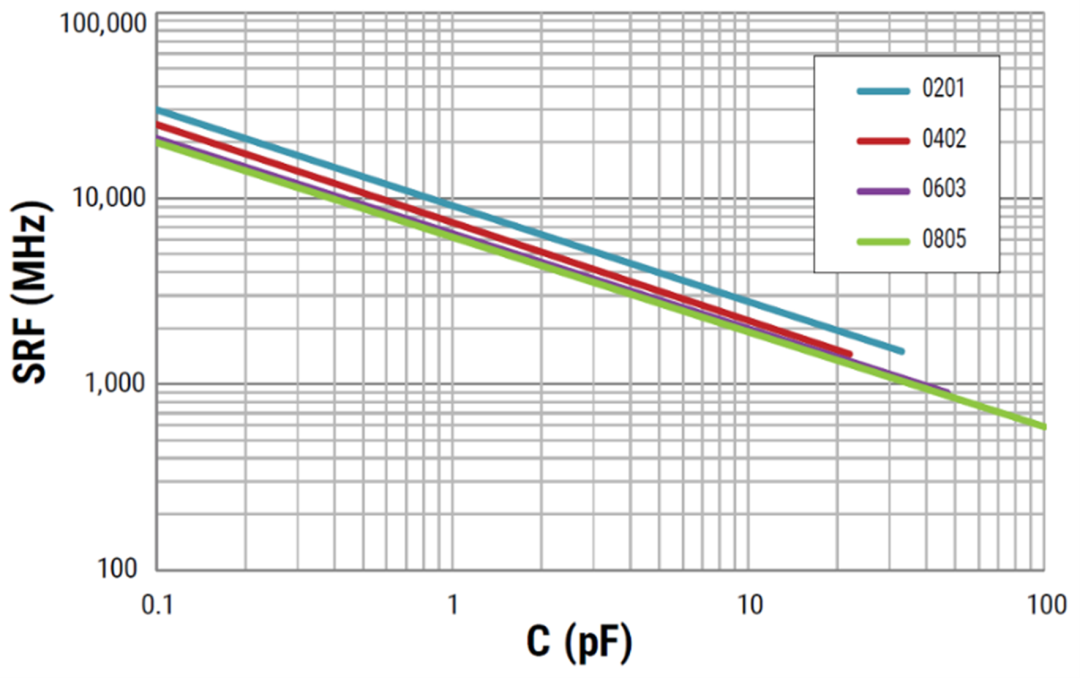

要判断电容器能否确保 PDN 阻抗维持在较低水平,最终考虑的频率范围是电容器的自谐振频率范围。总体来说,较小的外壳尺寸和较低的电容值可提供较高的自谐振频率。

有些电容器是专门针对非常高的频率设计的,如 RF 电路中使用的电容器。让我们通过一个例子来了解一下这些电容器开始产生电感的频率范围。我们可以看到,这些电容器的自谐振频率因外壳尺寸而异,可以达到非常高的数值(理论上而言)。实际上,并非所有电容器都能达到如下所示的极高谐振频率。我们将在下文中详细说明。

不同外壳尺寸下高频电容器的自谐振频率变化趋势。

2

平面对(频率范围接近 100 MHz-1 GHz)

当 PDN 阻抗曲线接近 100 MHz 的范围时,电容器将停止供电,而 PDN 阻抗曲线将由平面电容决定。当数字系统需要较大的电流时,会使用电源-接地平面对,这样也是为了提供较高的电容,以便在极高的谐振频率下仍能保持电容阻抗。平面的功率输出能力取决于电源-接地平面对中的扩散电感 (spreading inductance)。

最终,在非常高的频率(数十 Ghz)下,平面将开始共振并从边缘散发辐射。这时,平面对中的材料选择和电介质厚度成为影响 PDN 阻抗和噪声发射的主要因素。

3

封装(频率范围从 100 MHz 到 1 GHz)

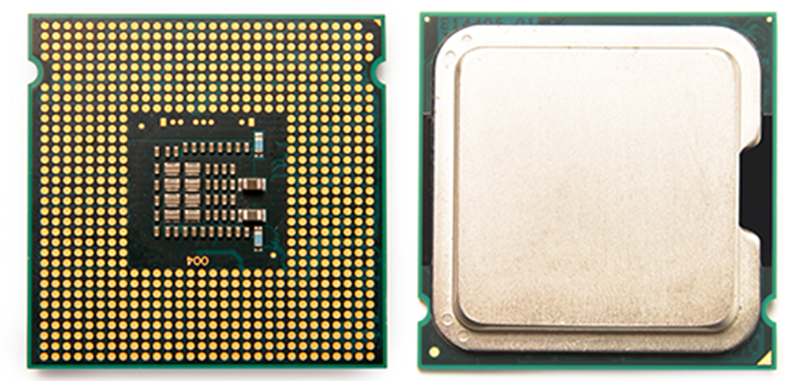

先进数字器件的封装可包含自身的电容,以便在 GHz 范围内以较低的阻抗传输功率。这些器件可对 PCB 上的平面对进行补偿,因为平面对在 GHz 频率下可能会产生电感。

此类封装包括片式电容器,可能还包括嵌入式电容器,以确保稳定的功率传输和较低的 PDN 阻抗,直接作用于器件封装中的半导体裸片。将这些电容直接置于封装上,可避免 PCB 上的焊盘和过孔产生电感,还可避免 BGA/LGA 封装中的引脚电感。

CPU 封装可包含自身的 PDN 元件,以便在低阻抗下实现功率传输。

4

裸片电容(频率范围大约在 1 GHz 以上)

半导体裸片可提供自身的电容,通常在裸片上直接提供总计 pF 级别的电容。该电容的好处是直接位于裸片上,电感极小,可为数字接口供电。这是在 1 GHz 或以上的频率下提供电容的最佳用例,以便支持速度最快的数字接口。

5

PCB 材料(所有频率)

任何 PCB 材料都会影响电磁波的传播,从而影响 PDN 阻抗曲线。我们在上文介绍电源-接地平面对时说过,在数十 GHz 频率下,平面区域会像平行板谐振器一样开始共振。

为确保电源-接地平面对发挥最大作用,分隔二者的材料应具备一些重要特性:

首选高 Dk 值的材料,因为它们能提供更高的电容

损耗正切值适中或较高,以抑制噪音

首选薄层材料,以获得更高的电容和更高的谐振截止频率

使用非常薄的高 Dk 值电介质(如嵌入式电容材料),可以减少振荡 PDN 的辐射发射,并提高总平面电容。这些材料的成本较高,但在高带宽、高功率的数字系统中却经常需要。

6

总结

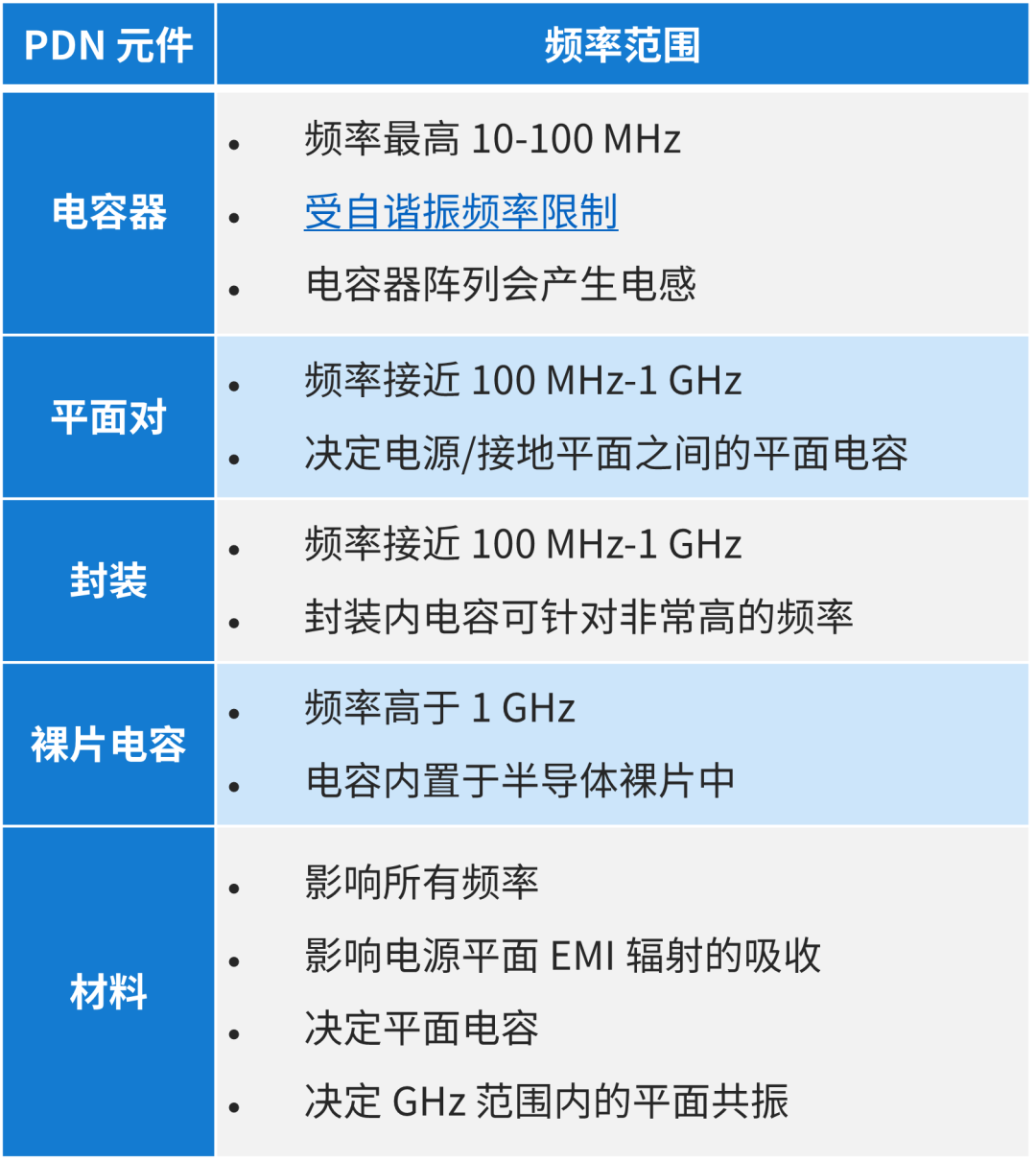

我们通过下表总结了 PDN 的各个部分及其对频率的影响。

电源完整性的最后一个关键因素与 PCB 完全无关,这个因素是电源稳压器或 VRM 的频率响应能力。VRM 电路通过控制环路确保稳定的输出电压,而 VRM 的频率响应需要足够快,以便抑制功率输出可能存在的噪声。如果电源轨上出现快速瞬变,VRM 就不能进入持续振荡状态。在为大型数字处理器设计高电流/低电压电源稳压器时,瞬变下的测量值应满足要求。

-

pcb

+关注

关注

4421文章

24024浏览量

427013 -

阻抗

+关注

关注

17文章

995浏览量

49559 -

数字系统

+关注

关注

0文章

165浏览量

21658 -

PDN

+关注

关注

0文章

86浏览量

23516

发布评论请先 登录

搞定电源完整性,不如先研究PDN!

电源传输网络(PDN)的具体作用

基于可分解的多目标进化算法的PDN阻抗的优化

电源完整性和配电网络阻抗对同步开关噪声的影响

具有寄生提取功能的PDN阻抗分析(Q&A)

PDN设计

NVSwitch芯片周围MLCC阵列的PDN阻抗优化方案

PDN 元件对阻抗的影响

PDN 元件对阻抗的影响

评论