全球算力产业已然迈入新一轮的快速发展阶段,RISC-V具备开源开放、模块化等独特优势,使我国能够独立开发、部署满足特定安全需求的算力芯片产品。当前,RISC-V已成为高算力时代的主要攻关方向。

近日,芯师爷携手慕尼黑上海电子展,在上海举办“2024算力技术创新发展生态大会”。在本次盛会中,RISC-V备受瞩目,与会嘉宾普遍认为,RISC-V已成为算力创新不可或缺的驱动力之一。赛昉科技作为中国RISC-V软硬件生态领导者,受邀出席此次盛会,并发表主题演讲。

赛昉科技资深销售总监周杰

赛昉科技资深销售总监周杰表示:“RISC-V架构的算力芯片,已呈现出从多核(4-16核)到众核(16/32/64核等)的发展态势。为提高大规模数据的并行处理能力,让各计算任务以最小的延迟和功耗分配至最适合的处理单元上完成,就要求算力芯片有一套高效的片上网络(NoC)系统,这是RISC-V技术落地高性能算力场景的核心要素。但目前这种NoC技术和产品主要掌握在海外供应商的手上。”

据周杰介绍,赛昉科技以全自研的国产RISC-V IP和NoC IP为基础,搭建多核/众核片上网络算力子系统平台,填补国产方案的空白。赛昉科技在五年时间里陆续交付了四款自研IP产品,包括两款高性能RISC-V CPU IP——昉∙天枢-90和昉∙天枢-80,以及两款一致性互联总线IP——昉∙星链-500和昉∙星链-700。赛昉科技还将不断扩充自研IP矩阵,为各类应用场景的芯片设计需求奠定坚实基础。

赛昉科技IP产品矩阵

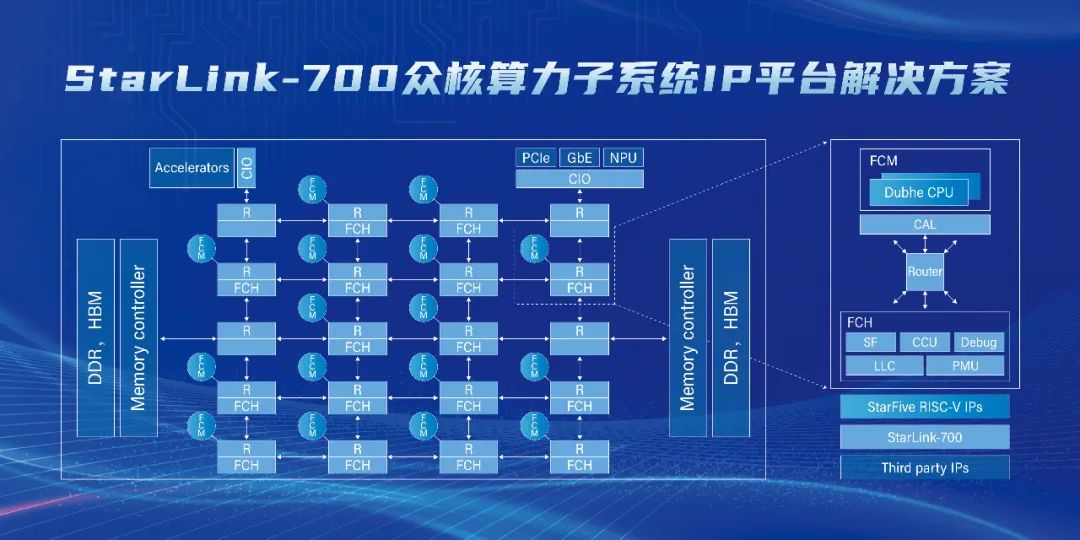

RISC-V众核算力子系统IP平台基于赛昉科技自研的NoC IP——昉·星链-700(StarLink-700)和RISC-V CPU IP——昉·天枢-90(Dubhe-90),赛昉科技推出高性能、高带宽、低延迟的RISC-V众核算力子系统平台。该平台是首个国产Mesh拓扑架构的算力子系统,可以支持最大144节点。平台包括:CPU簇、全一致性节点、全一致性IO节点、调度单元、调试单元、中断控制器、功耗管理、安全性、虚拟化、和内存子系统。该平台可广泛应用于服务器、DPU、计算存储、网络通信、AI等领域。在本次演讲中,周杰还分享了该平台的实际案例以及网络延迟等阶段性实测数据。

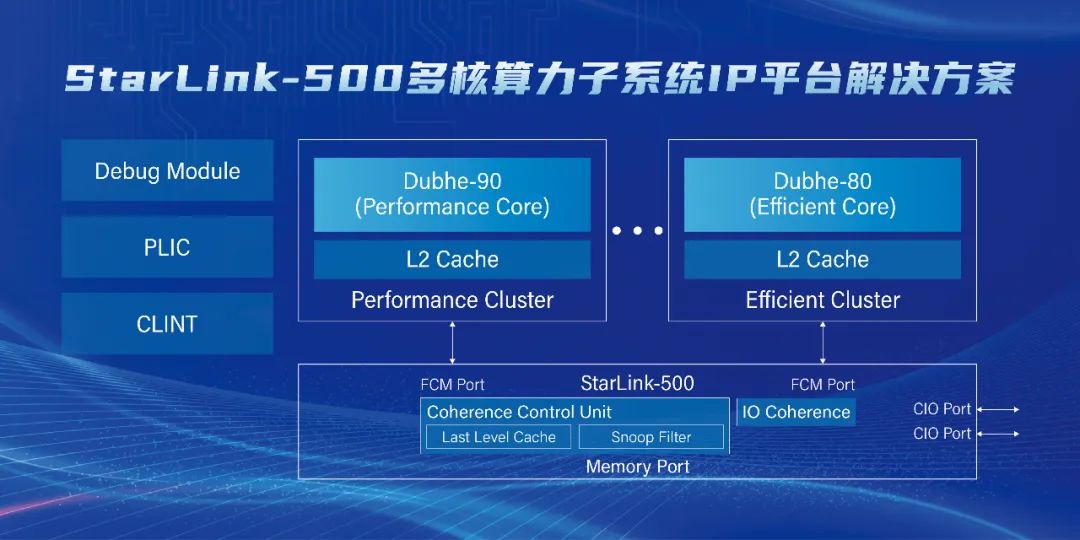

RISC-V大小核算力子系统IP平台基于两款高性能RISC-V CPU IP——昉·天枢-80(Dubhe-80)和昉·天枢-90(Dubhe-90),以及支持缓存一致性的互联总线IP——昉·星链-500(StarLink-500),赛昉科技推出全球首款RISC-V大小核算力子系统IP平台(多核方案)。周杰表示:“昉·星链-500多核(4-16核)算力子系统平台可根据系统需求灵活配置大小核数量,发挥出极致性能、能效平衡、能效优先三大优势,可被广泛应用于PC、笔记本电脑、移动设备、瘦客户机、NAS、工控机及各类行业终端的主控芯片设计。”

除了提供IP产品和子系统平台之外,赛昉科技还将向用户提供系统架构设计支持、DFT设计以及CPU后端实现等参考设计和技术支持。周杰分享称:“多核和众核算力芯片非常复杂,系统架构设计和CPU后端实现是重要环节。赛昉将协助用户一起攻克频率、带宽、延迟等设计难关。”

当下,RISC-V产业生态正蓬勃发展。周杰表示:“随着RISC-V IP核的性能突破,软件生态的完善,当下RISC-V生态系统已然初具规模。依托自研RISC-V CPU IP、互联总线IP等核心产品和技术,赛昉科技将持续推出满足不同应用场景的高性能RISC-V算力方案,2024年RISC-V在高性能计算场景中的表现值得大家为之期待。”

-

芯片

+关注

关注

453文章

50384浏览量

421719 -

RISC-V

+关注

关注

44文章

2228浏览量

46007 -

赛昉科技

+关注

关注

3文章

145浏览量

14257

发布评论请先 登录

相关推荐

预售启动!昉·星光 2 AI套件正式发布,基于RISC-V构建AI算力

赛昉科技产品亮相RISC-V开源创新中心,双方达成战略合作

赛昉科技与您相约IP-SoC China 2024 Day

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,赋能RISC-V高效落地

risc-v多核芯片在AI方面的应用

引领RISC-V核心技术,赛昉科技荣膺AspenCore“年度技术突破IP公司”奖项

芯原股份DC8200显示处理器IP助力赛昉科技RISC-V架构SoC

赛昉基于RISC-V的JH-7110智能视觉处理平台采用了芯原的显示处理器IP

攻克众核RISC-V芯片关键难点,赛昉科技斩获年度IP先锋奖

从多核到众核, 赛昉科技RISC-V+NoC IP子系统为算力芯片赋能

从多核到众核, 赛昉科技RISC-V+NoC IP子系统为算力芯片赋能

评论