SDRAM的发展经历

SDRAM(Synchronous Dynamic Random Access Memory),即同步动态随机存取存储器,是计算机系统中使用最广泛的内存类型之一。它的发展历程可以追溯到多个技术迭代,每个阶段都带来了性能上的显著提升。

第一阶段:SDR SDRAM

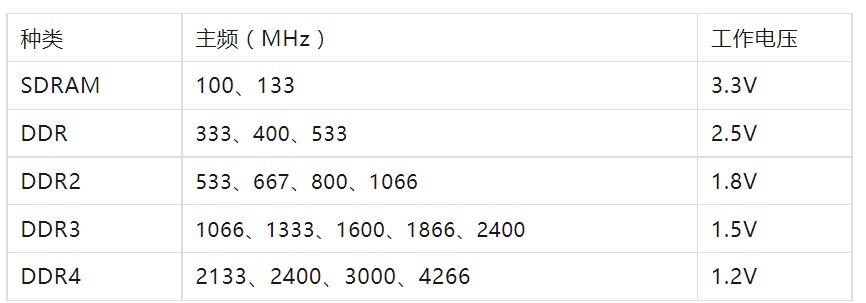

SDR SDRAM(Single Data Rate Synchronous Dynamic Random Access Memory)是SDRAM的最初形态,采用单端(Single-Ended)时钟信号进行数据传输。SDR SDRAM的时钟频率直接决定了数据的读写速率,如PC100和PC133分别表示时钟信号为100MHz和133MHz,数据读写速率也相应为100MB/s和133MB/s。SDR SDRAM的出现标志着内存技术向同步化方向发展的重要一步,但与后续的技术相比,其数据传输速率仍显不足。

第二阶段:DDR SDRAM

DDR(Double Data Rate)SDRAM的推出是内存技术的一次重大飞跃。DDR SDRAM采用了双倍数据速率技术,即在时钟信号的上升沿和下降沿都能传输数据,从而实现了数据传输速率的翻倍。DDR SDRAM的命名规则也发生了变化,如DDR200、DDR266等,表示的是等效数据传输速率(即实际工作频率的两倍)。DDR SDRAM的引入极大地提升了系统的整体性能,成为了当时的主流内存技术。

第三阶段:DDR2 SDRAM

DDR2 SDRAM在DDR SDRAM的基础上进行了进一步的优化和升级。它采用了更低的工作电压(1.8V),减少了功耗和发热量;同时,DDR2还引入了更先进的预取技术(Prefetch),提高了数据传输效率。DDR2 SDRAM的命名规则也延续了DDR的传统,如DDR2-400、DDR2-667等,表示的是等效数据传输速率。DDR2 SDRAM的普及进一步推动了计算机系统的性能提升,成为了市场上的主流内存产品。

第四阶段:DDR3 SDRAM

DDR3 SDRAM在DDR2的基础上再次进行了技术革新。它采用了更先进的8-bit Prefetch技术,进一步提高了数据传输效率;同时,DDR3还降低了工作电压(通常为1.5V),进一步减少了功耗和发热量。DDR3 SDRAM的命名规则也发生了变化,如DDR3-1066、DDR3-1600等,直接以等效数据传输速率命名。DDR3 SDRAM的推出不仅提升了系统的整体性能,还推动了计算机技术的进一步发展。

第五阶段:DDR4 SDRAM及以后

DDR4 SDRAM在2015年左右开始进入消费市场,相较于DDR3而言,DDR4在速度、功耗和容量等方面都有了显著提升。DDR4采用了更低的工作电压(通常为1.2V),进一步降低了功耗;同时,DDR4还引入了更高效的时序参数和预取技术,使得数据传输效率更高。DDR4的命名规则继续沿用DDR3的传统,如DDR4-2133、DDR4-3200等。随着技术的不断进步,DDR5、DDR6等更高性能的内存技术也已经在研发中,并有望在未来几年内推出。

SDRAM的工作原理

SDRAM的工作原理主要包括地址传输、行激活、列读取/写入、数据传输、预充电和刷新操作等步骤。以下是对这些步骤的详细解析:

1. 地址传输

CPU通过地址总线向SDRAM发送行地址和列地址。这些地址信息用于指定要访问的存储单元的具体位置。

2. 行激活

根据接收到的行地址,SDRAM将对应的存储体中的一行数据激活并读取到内部的行缓冲区中。这个过程被称为行激活或行选通(Row Activation)。在行激活后,该行数据就被缓存在行缓冲区中,等待进一步的列操作。

3. 列读取/写入

在确定行之后,通过列地址选择要操作的具体数据位进行数据的读取或写入操作。这个过程被称为列读取(Column Read)或列写入(Column Write)。在列读取操作中,指定的数据位被从行缓冲区中读取出来并通过数据总线传输到CPU或其他设备;在列写入操作中,数据通过数据总线传输到行缓冲区中并写入到指定的数据位。

4. 数据传输

在时钟信号的同步下,数据沿着数据总线进行传输。SDRAM采用与外部时钟信号同步的方式来传输数据,这保证了数据传输的稳定性和可靠性。

5. 预充电

完成一次操作后(无论是读取还是写入),对已激活的行进行预充电操作。预充电的目的是为了关闭当前行的激活状态并为下一次行激活做准备。通过预充电操作可以减少行之间的干扰并提高内存的访问效率。

6. 刷新操作

定期对存储单元进行刷新操作以保持数据的有效性。由于SDRAM采用电容来存储二进制位信息而电容存在漏电现象因此需要定期对存储单元进行刷新以保持数据的正确性。刷新操作通常由内存控制器自动完成无需用户干预。

工作原理的深入解析

1. 内部结构与组织

SDRAM内部由多个存储体(Bank)组成,每个存储体包含多个行(Row)和列(Column)。每个行对应一个行缓冲区,用于缓存该行中的数据。当CPU发起内存访问请求时,首先通过地址总线发送行地址和列地址到SDRAM控制器。控制器根据地址信息激活相应的行,并将数据读取到行缓冲区中。然后,通过列地址选择要读取或写入的数据位,并进行数据传输。

2. 时钟同步与数据管道

SDRAM的数据传输是与时钟信号同步的。时钟信号由外部时钟源提供,并作为SDRAM内部操作的基准。在时钟信号的驱动下,数据沿着数据总线以一定的速率进行传输。为了提高数据传输效率,SDRAM通常采用数据管道技术,即在时钟信号的每个周期内传输多个数据位(如8位或16位)。

3. 刷新机制

由于SDRAM使用电容来存储数据,而电容存在漏电现象,因此需要定期对存储单元进行刷新以保持数据的正确性。刷新操作通常由内存控制器自动完成,并在不影响正常读写操作的情况下进行。刷新周期根据电容的漏电速度和存储单元的稳定性来确定,以确保在数据丢失之前完成刷新。

4. 命令解码与执行

SDRAM控制器负责接收来自CPU的命令(如行激活、列读取/写入、预充电和刷新等),并对这些命令进行解码和执行。控制器内部包含复杂的逻辑电路和时序控制单元,以确保命令的正确执行和数据传输的稳定性。

DDR5及未来展望

DDR5 SDRAM作为最新的内存标准,已经在高端服务器和消费者市场上开始普及。DDR5带来了多项关键改进,包括更高的数据传输速率、更低的电压和功耗、更大的容量以及增强的错误校正和数据保护机制。

- 更高的数据传输速率 :DDR5引入了更先进的信号完整性和时序优化技术,使得数据传输速率得到了显著提升。目前市场上的DDR5内存模块已经能够达到4800MT/s以上的速度,未来还将进一步提升。

- 更低的电压和功耗 :DDR5采用了更低的操作电压(通常为1.1V),进一步降低了功耗和发热量。这有助于提升系统的整体能效比,并延长电池续航时间(在移动设备上)。

- 更大的容量 :DDR5支持更大的内存容量,以满足日益增长的数据处理需求。随着技术的进步,未来我们可能会看到更大容量的DDR5内存模块,以满足高性能计算和大数据应用的需求。

- 增强的错误校正和数据保护 :DDR5引入了更强大的错误校正码(ECC)和其他数据保护机制,以提高系统的可靠性和稳定性。这对于需要高可靠性的应用场景(如数据中心和服务器)尤为重要。

总结与展望

SDRAM作为计算机系统中不可或缺的组成部分,其发展历程见证了计算机技术的飞速进步。从SDR SDRAM到DDR5,每一次技术迭代都带来了显著的性能提升和更好的用户体验。未来,随着计算机技术的不断发展,我们可以期待更高性能、更低功耗、更大容量的内存技术的出现。这些新技术将进一步推动计算机系统的性能提升和应用的拓展,为我们带来更加丰富多彩的数字化生活。

-

SDRAM

+关注

关注

7文章

460浏览量

57892 -

存储器

+关注

关注

39文章

7768浏览量

172386 -

计算机

+关注

关注

19文章

7848浏览量

93556

发布评论请先 登录

一文搞懂DDR SDRAM工作原理

SDRAM的工作原理

SDRAM设计详细说明

使用Verilog实现基于FPGA的SDRAM控制器

SDRAM工作原理 DRAM控制器系统设计架构

简谈 SDRAM的工作原理

简谈 SDRAM的工作原理

DDR SDRAM工作原理简介

SDRAM工作原理 SDRAM布局布线说明

SDRAM的发展经历和工作原理

SDRAM的发展经历和工作原理

评论