数字逻辑门是一种电子电路,它根据输入端的数字信号组合做出逻辑决策。

数字逻辑门可以有多个输入,例如输入A、B、C、D等,但通常仅具有一个数字输出(Q)。单个逻辑门可以连接或级联在一起,以形成具有任何所需数量的输入的逻辑门功能,或者形成组合和顺序型电路,或者从标准门产生不同的逻辑门函数。

标准商用数字逻辑门有两种基本系列或形式,TTL代表晶体管-晶体管逻辑,如7400系列,CMOS代表互补金属氧化物硅,即4000系列芯片。TTL或CMOS的这种表示法是指用于制造集成电路(IC)或更常见的“芯片”的逻辑技术。

一般来说,TTL逻辑IC使用NPN和PNP型双极结晶体管,而CMOS逻辑IC使用互补MOSFET或JFET型场效应晶体管作为其输入和输出电路。

除了TTL和CMOS技术外,还可以通过将二极管、晶体管和电阻器连接在一起来制造简单的数字逻辑门,以产生RTL、电阻晶体管逻辑门、DTL、二极管晶体管逻辑门或ECL、发射极耦合逻辑门,但与流行的CMOS系列相比,这些现在不太常见。

集成电路(通常称为IC)可以根据其设计中可能包含的单个晶体管或“门”的数量分组为逻辑族。例如,一个简单的与门可能只包含几个单独的晶体管来操作。而更复杂的微处理器芯片可以在一块晶圆上包含数十亿个单独的晶体管栅极。集成电路根据逻辑门的数量或单个芯片内电路的复杂性进行分类,单个门的数量的一般分类如下:

集成电路的分类

小型集成电路(SSI)-在单个封装中包含多达10个晶体管或几个栅极,如AND、or、NOT栅极。

中型集成电路(MSI)-在单个封装中包含10到100个晶体管或数十个门,并执行数字操作,如加法器、解码器、计数器、触发器和多路复用器。

大规模集成电路(LSI)——100到1000个晶体管或数百个门,执行特定的数字操作,如I/O芯片、存储器、算术和逻辑单元。

超大规模集成电路(VLSI)——1000到10000个晶体管或数千个门,执行处理器、大型存储器阵列和可编程逻辑器件等计算操作。

超大规模集成电路(SLSI)-在单个封装中包含10000到100000个晶体管,并执行计算操作,如微处理器芯片、微控制器、基本PICs和计算器。

超大规模集成电路(ULSI)——超过100万个晶体管——是计算机CPU、GPU、视频处理器、微控制器、FPGA和复杂PIC中使用的大男孩。

虽然“超大规模”ULSI分类使用得不太好,但代表集成电路复杂性的另一个集成级别被称为片上系统(简称SOC)。这里的单个组件,如微处理器、存储器、外围设备、I/O逻辑等,都是在一块硅上生产的,它代表了一个芯片内的整个电子系统,从字面上讲,“集成”一词就是集成电路。

这些完整的集成芯片可以在一个封装内包含多达1亿个单独的硅CMOS晶体管门,通常用于移动电话、数码相机、微控制器、PIC和机器人型应用。

摩尔定律

1965年,英特尔公司的联合创始人Gordon Moore预测,关于半导体栅极技术的发展,“单个芯片上的晶体管和电阻器的数量将每18个月翻一番”。早在1965年,戈登·摩尔就发表了著名的评论,当时一个硅片或芯片上大约只有60个单独的晶体管栅极。

1971年,世界上第一个微处理器是Intel 4004,它有一个4位数据总线,在一个芯片上包含约2300个晶体管,工作频率约为600kHz。如今,英特尔公司在其运行频率接近4GHz的新型四核i7-2700K Sandy Bridge 64位微处理器芯片上安装了惊人的12亿个单独的晶体管门,随着新型更快的微处理器和微控制器的开发,片上晶体管的数量仍在上升。

数字逻辑状态

数字逻辑门是构建所有数字电子电路和基于微处理器的系统的基本构建块。基本数字逻辑门对二进制数执行AND、OR和NOT的逻辑运算。

在数字逻辑设计中,只允许两个电压电平或状态,这些状态通常被称为逻辑“1”和逻辑“0”,或高和低,或真和假。这两种状态在布尔代数和标准真值表中分别用“1”和“0”的二进制数字表示。

数字状态的一个很好的例子是一个简单的电灯开关。开关可以是“ON”或“OFF”,一种状态或另一种状态,但不能同时处于这两种状态。然后,我们可以将这些不同数字状态之间的关系总结为:

Boolean Algebra | Boolean Logic | Voltage State |

Logic"1" | TURE(T) | HIGH(H) |

Logic"0" | FALSE(F) | LOW(L) |

大多数数字逻辑门和数字逻辑系统都使用“正逻辑”,其中逻辑电平“0”或“LOW”由零电压、0v或接地表示,逻辑电平“1”或“HIGH”由更高的电压(如+5伏)表示,并尽可能快地从一个电压电平切换到另一个电压电平,从逻辑电平“O”切换到“1”,或从“1”转换到“0”,以防止逻辑电路的任何故障操作。

还有一个互补的“负逻辑”系统,其中逻辑“0”和逻辑“1”的值和规则是相反的,但在本教程中关于数字逻辑门的部分,我们将只参考最常用的正逻辑约定。

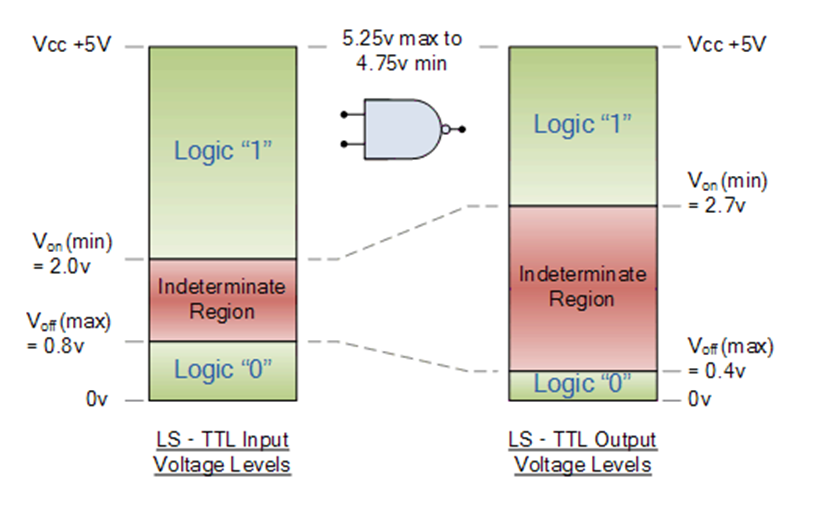

在标准TTL(晶体管-晶体管逻辑)IC中,输入和输出电压电平有一个预定义的电压范围,它准确地定义了什么是逻辑“1”电平,什么是逻辑”0“电平,如下所示。

TTL输入和输出电压电平

在双极7400和CMOS 4000系列的数字逻辑门中都有各种各样的逻辑门类型,例如74Lxx、74LSxx、74ALSxx、74HCxx、74HCCxx、74ACTxx等,每种逻辑门与另一种相比都有其独特的优点和缺点。产生逻辑“0”或逻辑“1”所需的确切开关电压取决于特定的逻辑组或系列。

然而,当使用标准+5伏电源时,2.0伏至5伏之间的任何TTL电压输入都被视为逻辑“1”或“高”,而低于0.8伏的任何电压输入都会被视为“0”或“低”。在这两个电压电平之间的电压区域作为输入或作为输出被称为不确定区域,并且在该区域内操作可能导致逻辑门产生错误输出。

与TTL类型相比,CMOS 4000逻辑系列使用不同级别的电压,因为它们是使用场效应晶体管或FET设计的。在CMOS技术中,逻辑“1”电平在3.0到18伏之间工作,逻辑“0”电平低于1.5伏。下表显示了传统TTL和CMOS逻辑门的逻辑电平之间的差异。

TTL和CMOS逻辑电平

Device Type | Logic 0 | Logic1 |

TTL | 0 to 0.8v | 2.0 to 5v(Vcc) |

CMOS | 0 to 1.5v | 3.0to18v(VDD) |

然后,根据上述观察结果,我们可以将理想的TTL数字逻辑门定义为具有0伏(接地)的“低”电平逻辑“0”和+5伏的“高”电平逻辑”1“的数字逻辑门,这可以证明为:

理想的TTL数字逻辑门电压电平

开关的打开或闭合产生逻辑电平“1”或逻辑电平“0”,电阻R被称为“上拉”电阻。

数字逻辑噪声

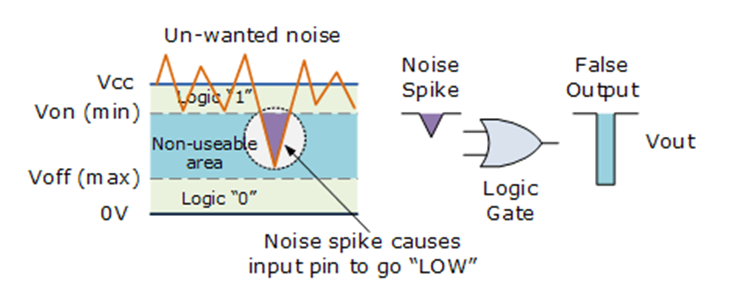

然而,在这些定义的HIGH和LOW值之间是通常所说的“无人区”(上面的蓝色区域),如果我们在无人区内施加一个值的信号电压,我们不知道逻辑门是将其响应为电平“0”还是电平“1”,输出将变得不可预测。

噪声是指由外部干扰(如附近的开关、电源波动或拾取杂散电磁辐射的电线和其他导体)感应到电子电路中的随机和不需要的电压。然后,为了使逻辑门不受噪声的影响,必须具有一定的噪声裕度或抗扰度。

数字逻辑门抗扰度

在上面的例子中,噪声信号被叠加到Vcc电源电压上,并且只要它保持在最小电平(VON(min))之上,逻辑门的输入和相应输出就不受影响。但是,当噪声电平变得足够大并且噪声尖峰导致高电压电平下降到该最小电平以下时,逻辑门可以将该尖峰解释为低电平输入并且相应地切换输出,从而产生错误的输出切换。然后,为了使逻辑门不受噪声的影响,它必须能够在其输入上容忍一定量的不需要的噪声,而不改变其输出的状态。

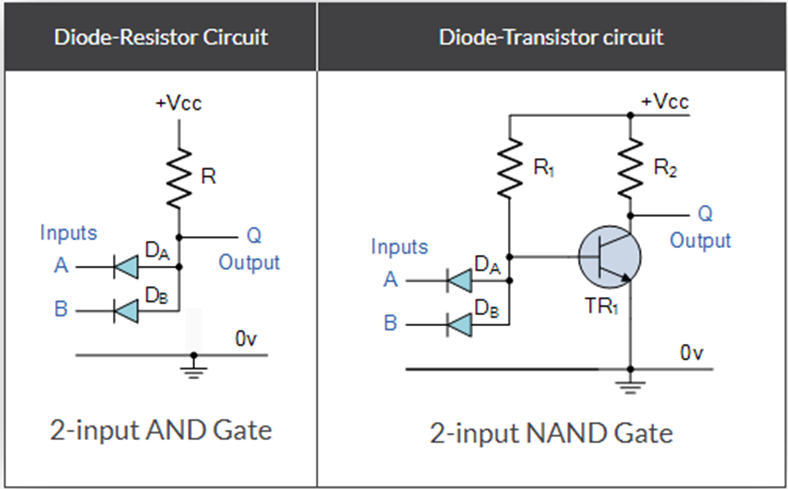

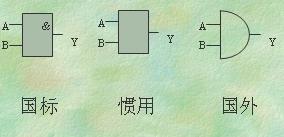

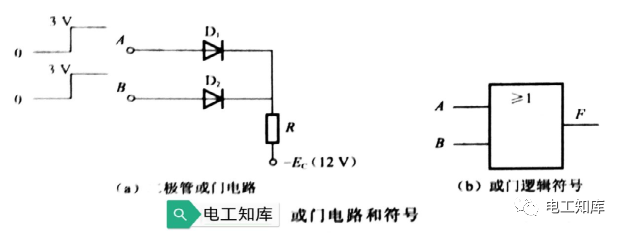

简单的基本数字逻辑门

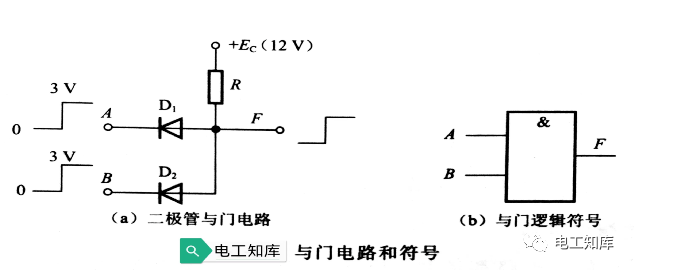

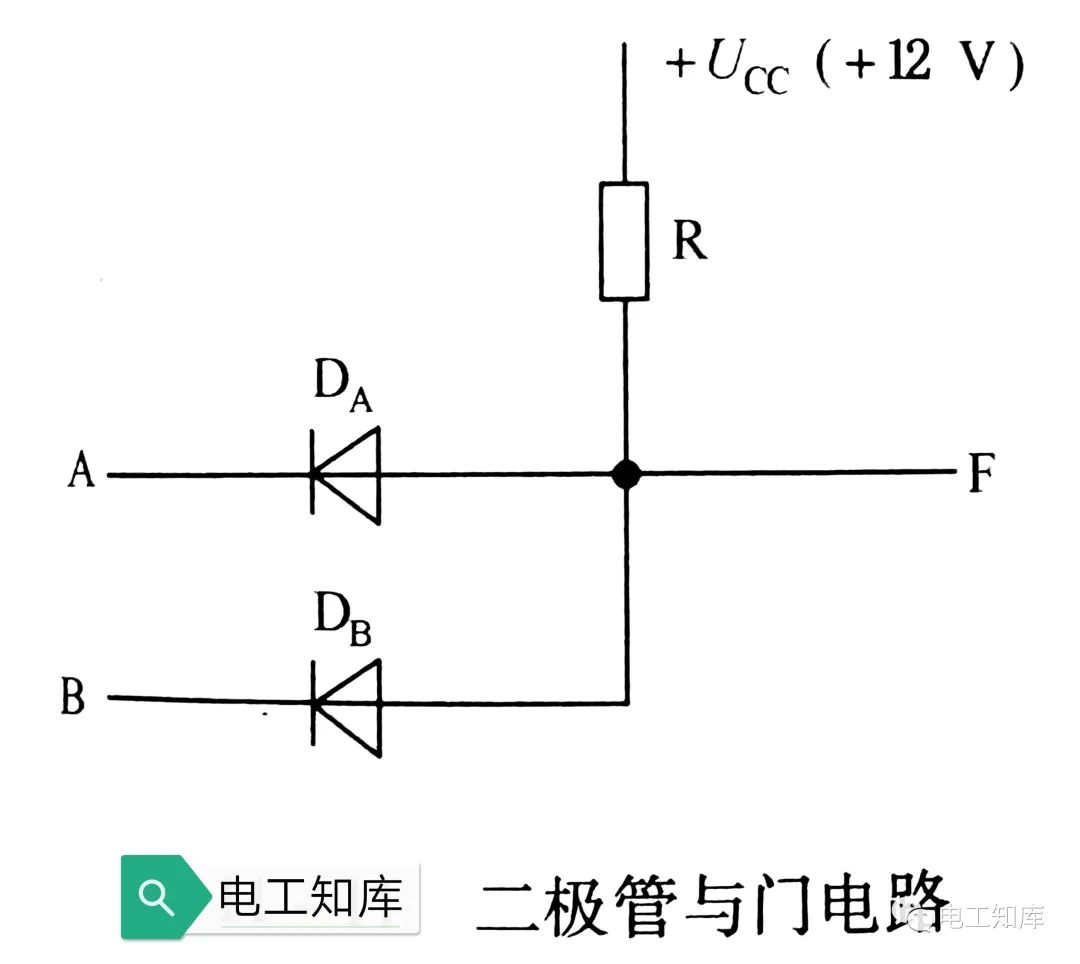

简单的数字逻辑门可以通过将晶体管、二极管和电阻器与下面给出的二极管-电阻器逻辑(DRL)and门和二极管-晶体管逻辑(DTL)NAND门的简单示例相结合来制造。

简单的2输入二极管电阻器与门可以通过添加单个晶体管反相(NOT)级转换为NAND门。在实际的商用逻辑IC中不使用诸如二极管、电阻器和晶体管之类的分立部件来制造数字逻辑门电路,因为这些电路遭受传播延迟或门延迟以及由于上拉电阻器而引起的功率损耗。

二极管电阻器逻辑的另一个缺点是没有“扇出”功能,即单个输出驱动下一级的许多输入的能力。此外,这种类型的设计不会完全“关闭”,因为逻辑“0”产生0.6v的输出电压(二极管压降),因此使用以下TTL和CMOS电路设计。

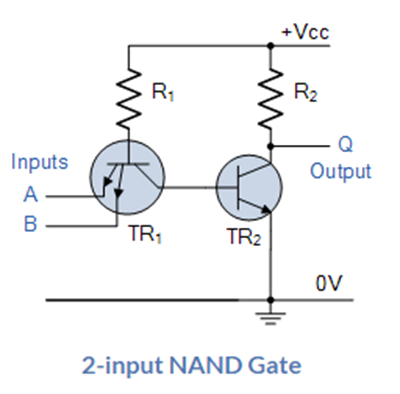

基本TTL逻辑门

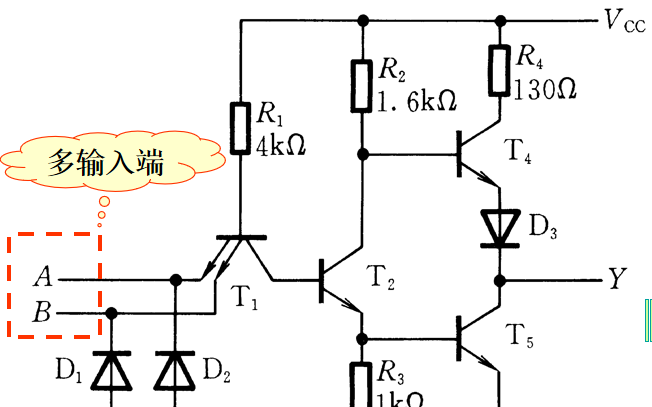

上面的简单二极管电阻器与门使用单独的二极管作为输入,每个输入一个。由于双极晶体管实际上是两个连接在一起的二极管结,代表NPN(负-正-负)器件或PNP(正-负-正)器件,因此二极管-晶体管逻辑(DTL)电路的输入二极管可以被一个具有多个发射极输入的单个NPN晶体管取代,以形成另一种类型的逻辑电路,称为晶体管-晶体管逻辑或TTL,如图所示。

这种简化的NAND门电路由具有两个(或多个)发射极端子的输入晶体管TR1和TR2的单级反相NPN开关晶体管电路组成。

当代表输入“A”和“B”的TR1的一个或两个发射极连接到逻辑电平“0”(LOW)时,TR1的基极电流通过其基极/发射极结接地(0V),TR1饱和,其集电极端子跟随。此动作导致TR2的基极连接到地(0V),因此TR2为“OFF”,Q处的输出为HIGH。

当输入“A”和“B”均为逻辑电平“1”的高电平时,输入晶体管TR1变为“OFF”,开关晶体管TR2的基极变为“HIGH”并变为“ON”,因此由于晶体管的开关动作,Q处的输出为LOW。TR1的多个发射极被连接作为输入,从而产生NAND门功能。

发射极耦合数字逻辑门

发射极耦合逻辑或简称ECL,是另一种类型的数字逻辑门,它使用双极晶体管逻辑,其中晶体管不在饱和区工作,就像它们与标准TTL数字逻辑门一样。相反,输入和输出电路是推挽连接的晶体管,其电源电压相对于地为负。

与标准TTL类型相比,这具有将发射极耦合逻辑门的操作速度提高到千兆赫范围的效果,但噪声在ECL逻辑中具有更大的影响,因为不饱和晶体管在其有源区内操作,并放大和切换信号。

集成电路的“74”子族

随着电路设计的改进,考虑到传播延迟、电流消耗、扇入和扇出要求等,这种类型的TTL双极晶体管技术形成了前缀为“74”的数字逻辑IC系列的基础,如“7400”Quad 2输入NAND门或“7402”Quad 2-输入NOR门等。

74xxx系列IC的子系列与用于制造栅极的不同技术有关,它们由74名称和器件编号之间的字母表示。有许多TTL子系列可提供广泛的开关速度和功耗,如74L00或74ALS00 NAND门,其中“L”代表“低功率TTL”,“ALS”代表“高级低功率肖特基TTL”,如下所示。

•74xx或74Nxx:标准TTL–这些器件是70年代早期引入的逻辑门的原始TTL系列。它们具有大约10ns的传播延迟和大约10mW的功耗。电源电压范围:4.75至5.25伏

•74Lxx:低功率TTL–通过增加内阻的数量,功耗比标准类型有所提高,但代价是降低了开关速度。电源电压范围:4.75至5.25伏

•74Hxx:高速TTL–通过减少内阻的数量提高了开关速度。这也增加了功耗。电源电压范围:4.75至5.25伏

•74Sxx:与74Lxx和74Hxx类型相比,肖特基TTL–肖特基技术用于提高输入阻抗、开关速度和功耗(2mW)。电源电压范围:4.75至5.25伏

•74LSxx:低功率肖特基TTL–与74Sxx类型相同,但增加了内阻以提高功耗。电源电压范围:4.75至5.25伏

•74ASxx:先进的肖特基TTL–在74Sxx肖特基类型的基础上改进设计,优化以提高开关速度为代价,功耗约为22mW。电源电压范围:4.5至5.5伏

•74ALSxx:高级低功率肖特基TTL–与74LSxx类型相比,功耗降低约1mW,开关速度提高4nS。电源电压范围:4.5至5.5伏

•74HCxx:高速CMOS–CMOS技术和晶体管,使用CMOS兼容输入将功耗降低到1uA以下。电源电压范围:4.5至5.5伏

•74HCTxx:高速CMOS–CMOS技术和晶体管,可将功耗降低到1uA以下,但由于TTL兼容输入,传播延迟增加了约16nS。电源电压范围:4.5至5.5伏

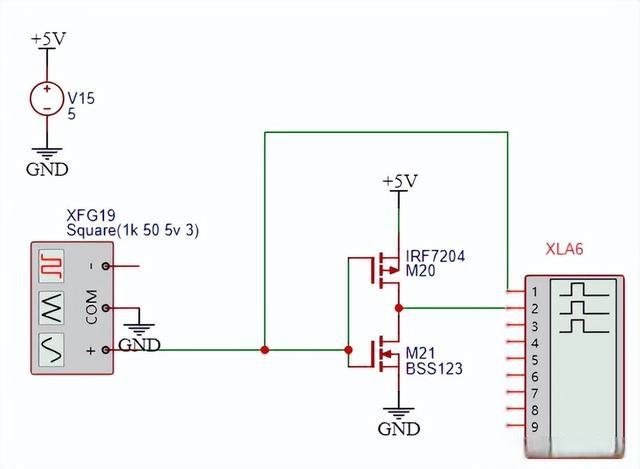

基本CMOS数字逻辑门

TTL数字逻辑门系列的主要缺点之一是,逻辑门基于双极晶体管逻辑技术,并且由于晶体管是电流操作器件,它们消耗来自固定+5伏电源的大量功率。

此外,TTL双极晶体管栅极在从“OFF”状态切换到“ON”状态时,工作速度有限,反之亦然,称为“栅极”或“传播延迟”。为了克服这些限制,开发了使用“场效应晶体管”或FET的被称为“CMOS”(互补金属氧化物半导体)的互补MOS逻辑门。

由于这些栅极同时使用P沟道和N沟道MOSFET作为其输入设备,在无开关的静态条件下,CMOS栅极的功耗几乎为零(1至2μA),因此非常适合用于低功率电池电路,开关速度高达100MHz,用于高频定时和计算机电路。

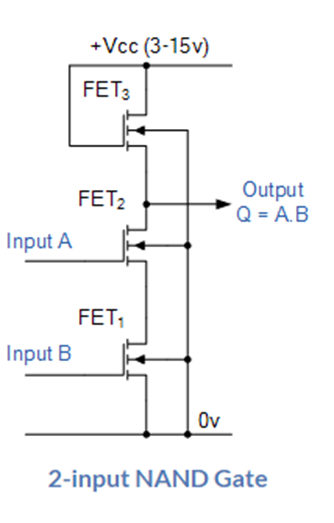

这个基本的CMOS栅极示例包含三个N沟道常关增强MOSFET,每个输入一个,由FET1和FET2组成,以及一个额外的开关MOSFET,FET3通过其栅极永久“导通”偏置。

当一个或两个输入“A”和“B”接地至逻辑电平“0”时,相应的输入MOSFET、FET1或FET2被切换为“OFF”,从而从FET3的源极端产生逻辑“1”(高)输出条件。

只有当输入“A”和“B”都保持在逻辑电平“1”的高电平时,电流才会流过相应的MOSFET,将其切换为“ON”,从而在Q处产生相当于逻辑电平“0”的输出状态,因为MOSFET、FET1和FET2都导通。因此产生代表NAND门功能的开关动作。

电路设计在开关速度、低功耗和改进的传播延迟方面的改进导致了标准CMOS 4000“CD”系列逻辑IC的开发,以补充TTL范围。

与标准TTL数字逻辑门一样,CMOS封装中提供了所有主要的数字逻辑门和器件,如CD4011、Quad 2输入NAND门或CD4001、Quad 2-输入NOR门及其所有子系列。

与TTL逻辑一样,互补MOS(CMOS)电路利用了这样一个事实,即N沟道和P沟道器件可以在同一衬底材料上一起制造,以形成各种逻辑功能。

与等效TTL类型相比,CMOS范围的IC的一个主要缺点是它们很容易被静电损坏。与TTL逻辑门的输入和输出电平都工作在单个+5V电压上不同,CMOS数字逻辑门的工作电压在+3到+18伏之间。

常见的CMOS子系列包括:

•4000B系列:标准CMOS–这些器件是70年代早期引入的原始缓冲CMOS逻辑门系列,在3.0至18v直流电源电压下工作。

•74C系列:5v CMOS–这些器件与标准5v TTL器件引脚兼容,因为它们的逻辑开关在CMOS中实现,但具有TTL兼容输入。它们在3.0至18v直流电源电压下工作。

请注意,CMOS逻辑门和器件对静电敏感,因此请始终采取适当的预防措施,如在防静电垫或接地工作台上工作、佩戴防静电腕带以及在需要之前不要从防静电包装中取出零件。

-

电路板

+关注

关注

140文章

4884浏览量

97281 -

逻辑门电路

+关注

关注

2文章

65浏览量

11990 -

数字系统

+关注

关注

0文章

140浏览量

20819

发布评论请先 登录

相关推荐

数字系统的核心:逻辑门电路

数字系统的核心:逻辑门电路

评论