1、DDIO用法

2、时钟输出

3、Efinity处理三态端口问题

4、PLL的添加

5、HSIO的解串器用法

1、DDIO用法

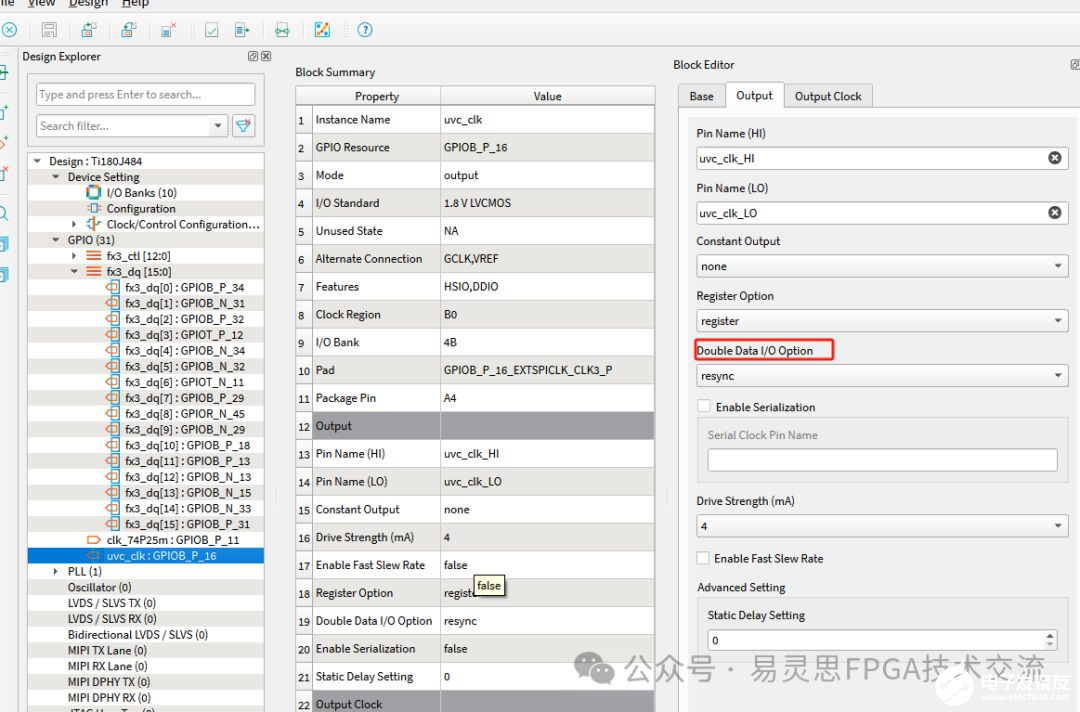

对于输入输出IO很多时候会用到DDIO的用法。对于DDIO,就是时钟的双沿采集或者发送数据,所以必须要用到寄存器。它的设置也比较简单,在intefaceDesigner中添加GPIO,并把register Option设置为register,另外要设置Double Data IO Option模式,分别为normal和resync。

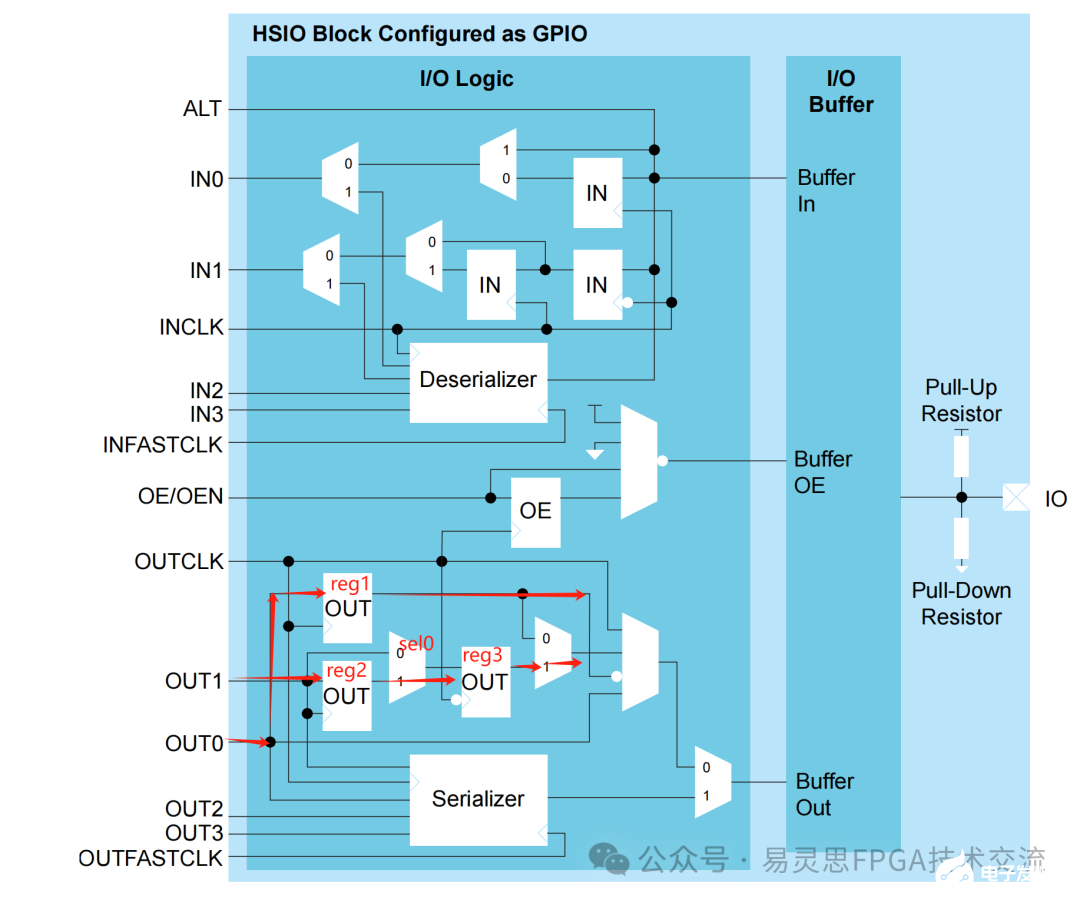

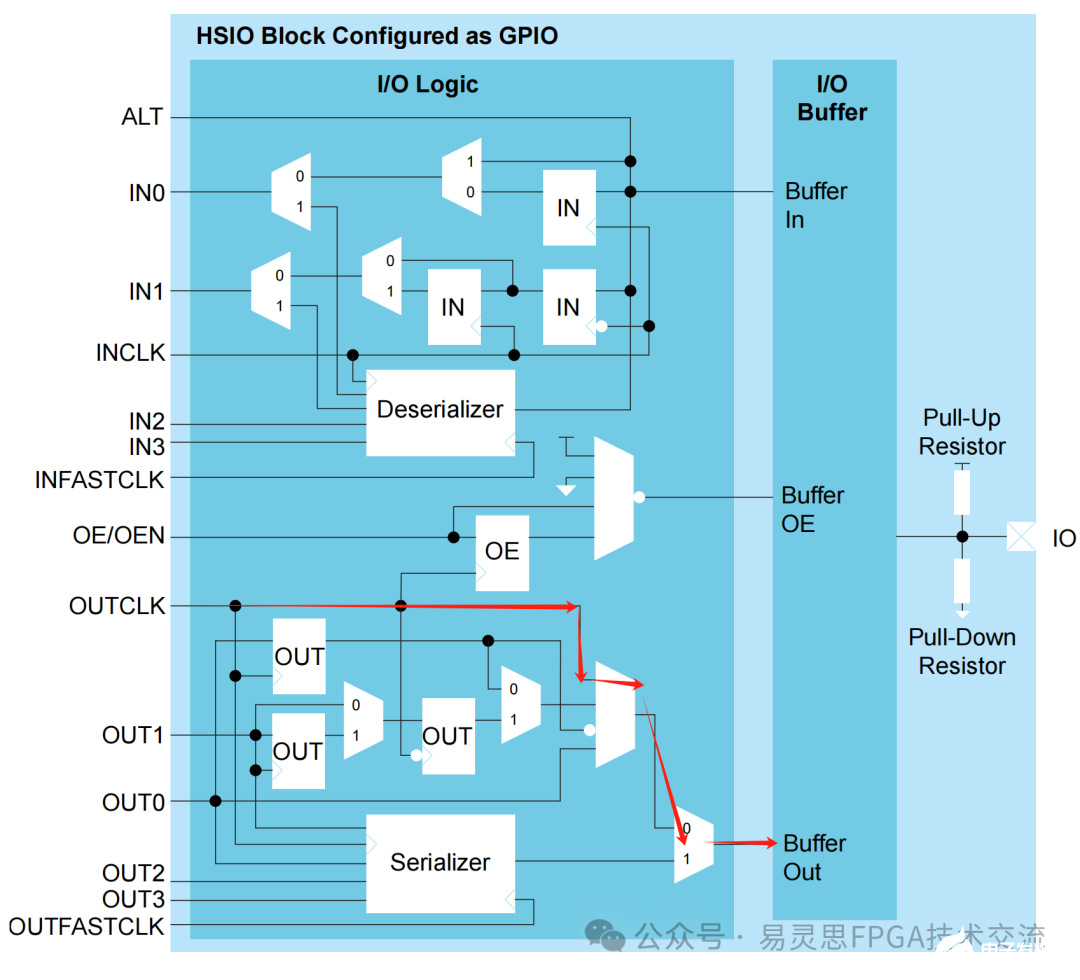

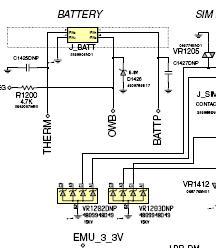

下图是易灵思的GPIO的结构。

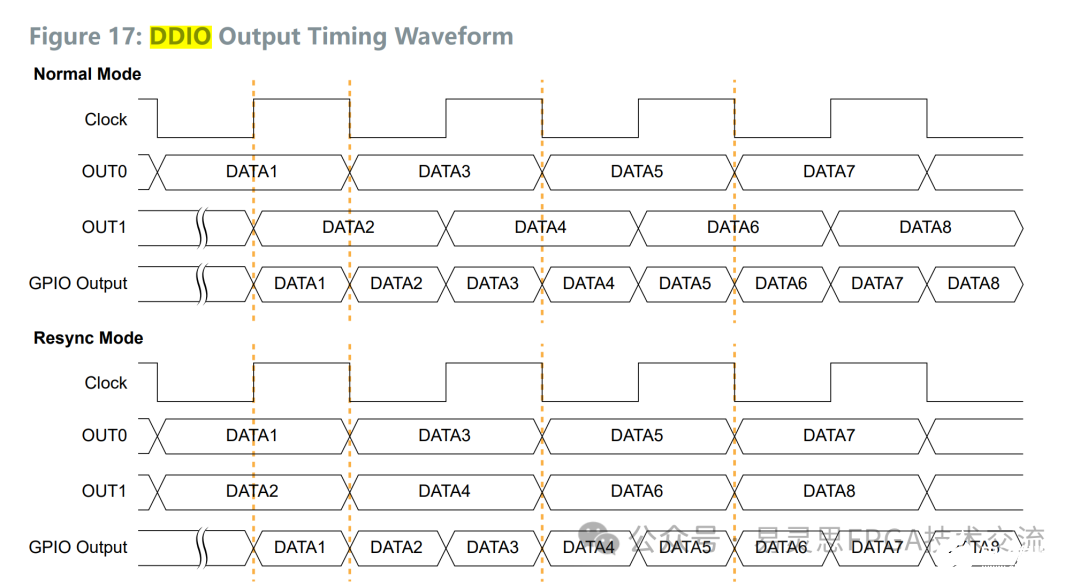

对应上图我们以ODDIO为例,分别标出了reg1,reg2和reg3三个寄存 器。当OUT0为上升沿的触发信号,即HI,OUT1为下降沿的触发信号,即LO。当DDIO模式设置为Normal mode时,OUT1经过reg3输出;当设置为Resync mode时OUT1经过了reg2和reg3,reg2用于对数据打一拍来对齐数据,下面是数据的输出波形。

我们只需要在top模块中添加相应信号即可以用于控制:

module DDIO_Test(...otuputoddio_HI,output oddio_LO,...);

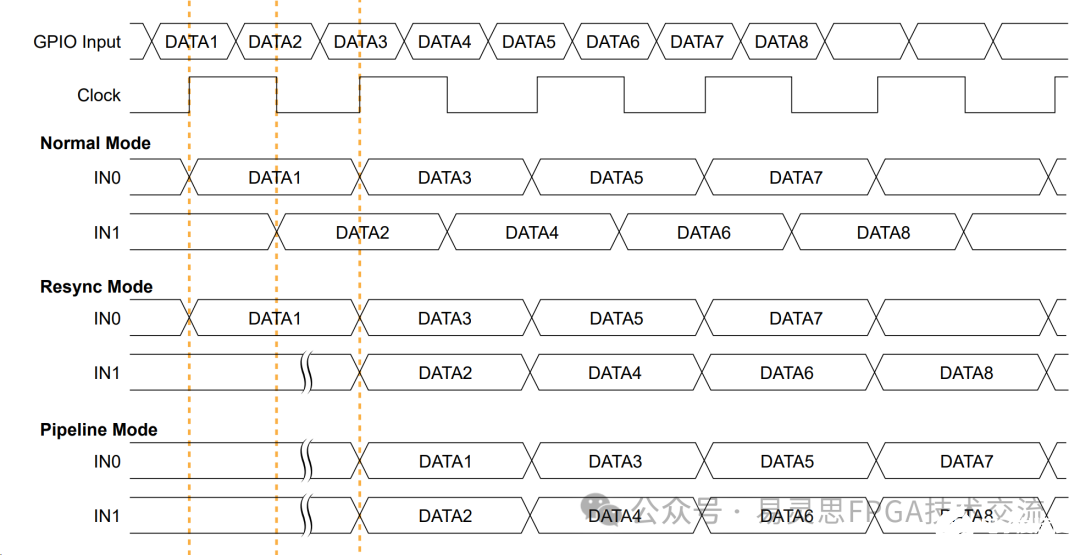

下图为数据输入时的波形,分别对应 Normal和Resync mode。

2、时钟输出

易灵思所有的GPIO都可以用作时钟输出。这里我们提供两种时钟输出方式。

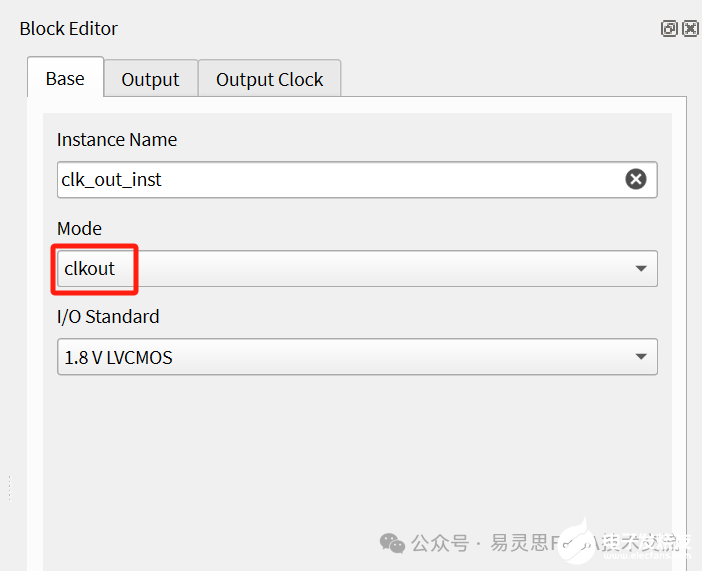

方法一:把时钟设置为clkout模式。下图选自钛金系列ds上的IO框图 。从图片上可以看到OUTCLK的路径。

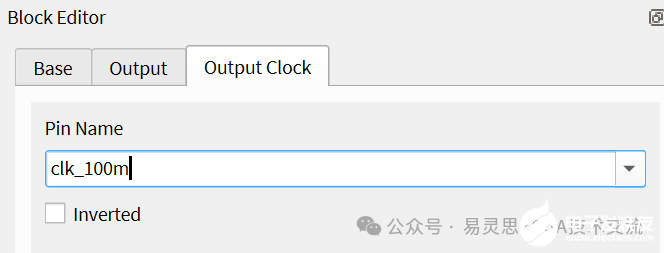

在添加 GPIO时,设置Mode为clkout,并在output Clock中输入时钟名。

这里需要 注意的是,时钟名不能从core直接输出,而只能使用interface中使用的时钟,如PLL输出的时钟或者GCLK输入的时钟。比如我们在代码中定义了一个IO,如下:

module clk_test(...output clk_100m,...);

如果直接把代码中定义的clk_100m直接配置给interface的GPIO,这时软件会报错。

方法二:

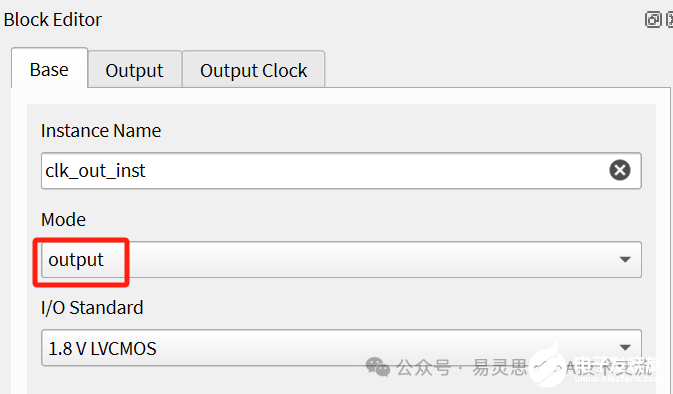

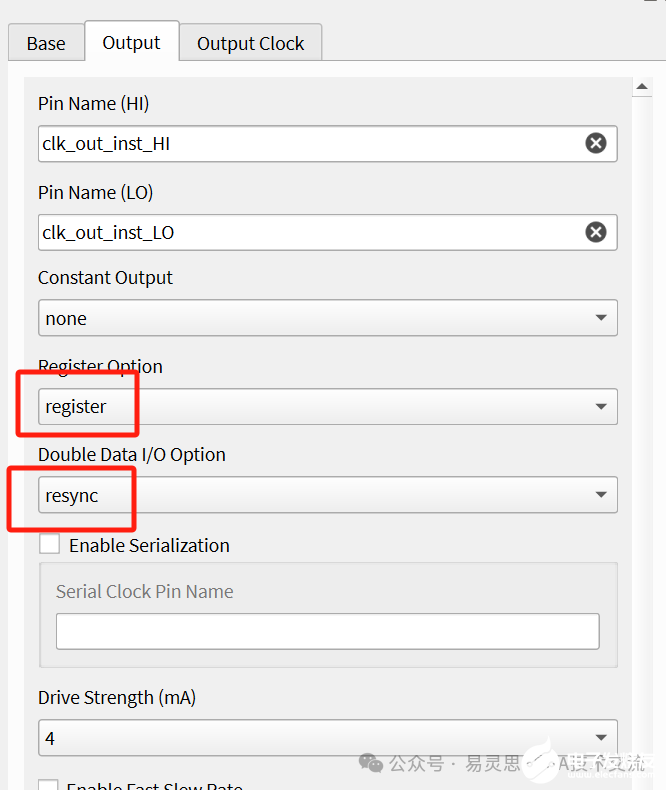

通过DDIO的方式设置时钟输出。IO模式设置为output,并打开Register Option及Double Data I/O Option,并指定时钟。

程序内部分别对DDIO的高低位分部赋值为1或者0.

assign clk_out_inst_HI = 1'b1;assign clk_out_inst_LO=1'b0;

对于两种方式的使用,Trion有很大一部分的GPIO不支持DDIO,只能使用第一种方式,钛金所有的GPIO都支持DDIO;另外在源同步时钟数据输出时,DDIO的方式可以保证数据和时钟的延时一致,所以易灵思推荐使用DDIO的方式。

3、Efinity处理三态端口问题

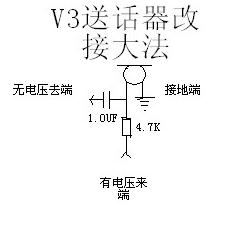

我们在处理三态门时一般都是用下面的语句;

inout bidr_pad;wirein;wire out;wireo_oe;assign bidr_pad= o_en ? out :z;assignin=bidr_pad;

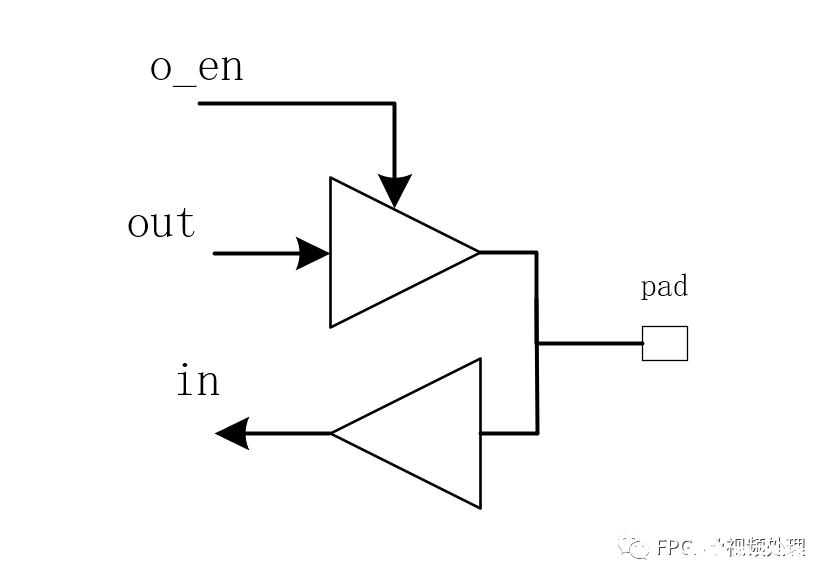

其实它对应的硬件结构就是下面的框图。它涉及到3个信号:in,out,o_en。

当o_en = 1时,out可以通过out buf输出到pad上,同时会反馈到in;

当o_en = 0时,out buf就是高阻态。in的信号就是通过外部pad通过in buf输入进来。

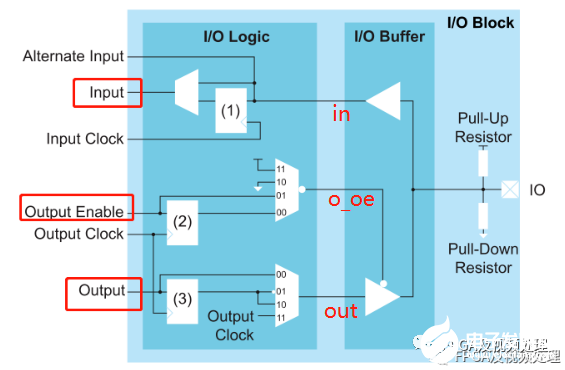

最初使用Efinity,因为架构差异,很多人被inout的使用难住了。这里来说明一下。在易灵思的产品架构中,原有的rtl代码都是针对fabric的,也就逻辑部分。而IO被认为是外设。如下图I/O Buffer部分相对于fabric是外设,它是在Efinity的interface Designer中设置的。这样在rtl只需要定义:

inputin;outputout;output o_oe;

有了上面的认知,我们就容易理解在efinity中怎样添加三态。

添加三态门的过程如下:

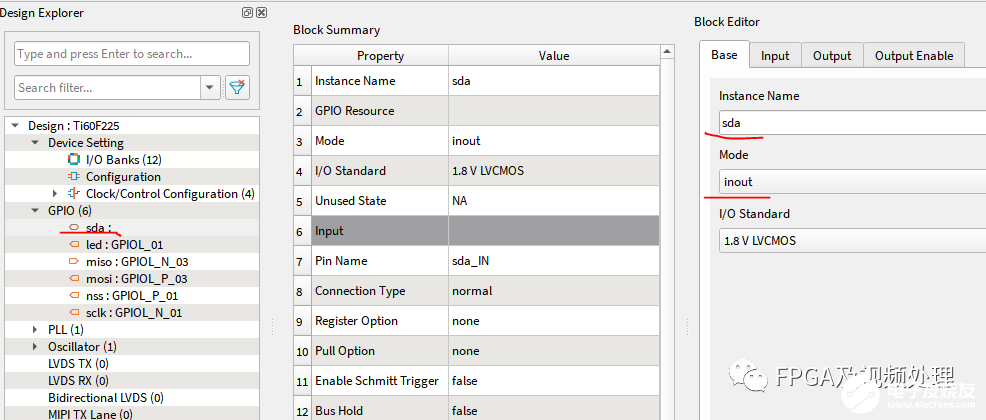

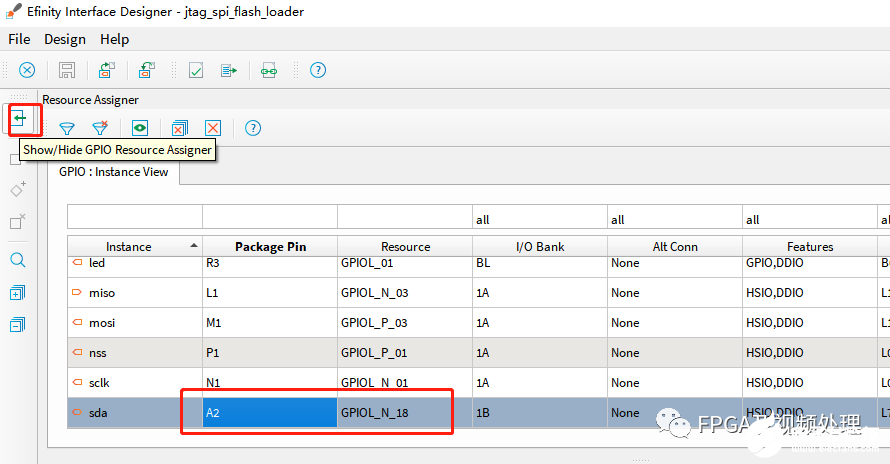

我们在interface中添加一个gpio,命名为sda,把Mode选择为inout,

点击show/Hide GPIO Resource Assigner,打开IO分配界面分配IO.

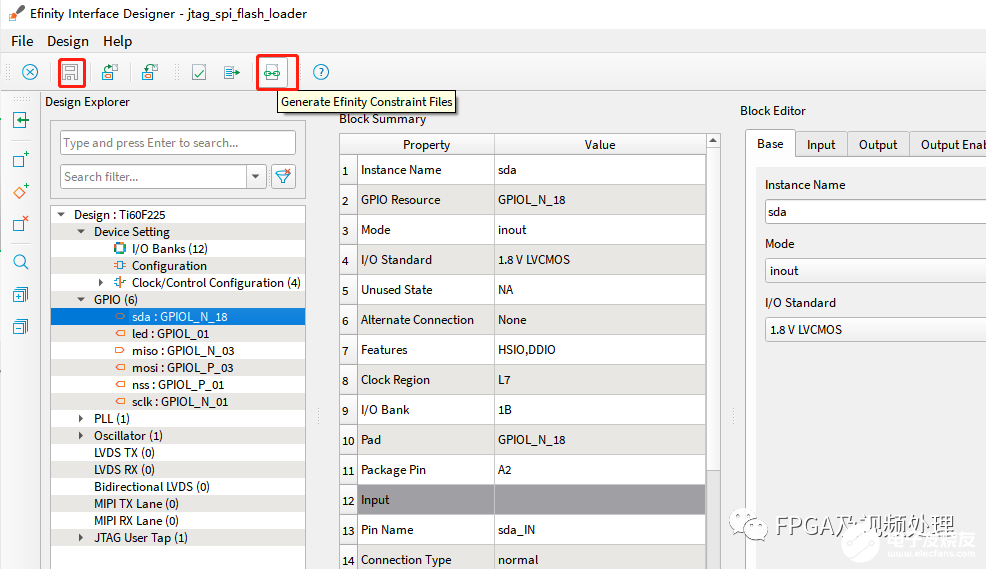

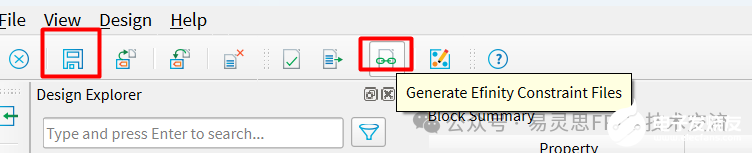

点击保存和Generate Efintiy Constraint Files.

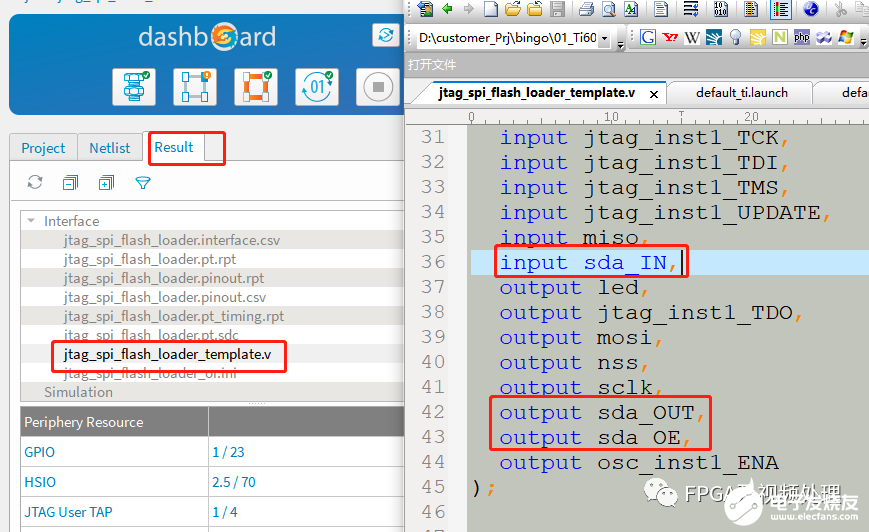

打开工程面板下面的Result下的xxx_template.v,可以看到里面添加了

Inputsda_IN,output sda_OE,output sda_OUT

三个信号,把这三个信号复制到工程文件的顶层中去,这样就定义好了一个inout,可以直接全用了。

另外如果要添加IO寄存可以根据实际需要去选择,同时要注意为寄存器选择准确的时钟。

这样就不用再写assign sda = oe ? sda_out :z; 这样的语句,因为oe就是sda_OE, sda_out对应的就是接口生成的sda_OUT。

在Efinity的.v文件中不支持inout 双向口的定义,另外Efinity也不支持‘z’这种定义。

4、PLL的添加

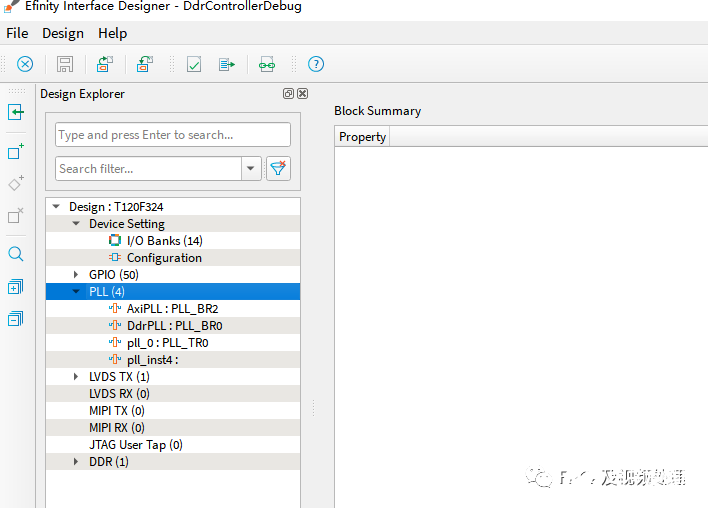

易灵思的FPGA在生成PLL的方式与别的厂家稍有区别,这与其的core和interface架构是相对应的。对于易灵思的FPGA来讲,PLL,GPIO,MIPI,LVDS和DDR相对于core部分都是外设。而这些外设的设置都是在interface designer中的。下面以pll的添加为例,对于trion系列的设置简单说明。钛金系列会稍微的区别,但是只要了解了一个,另一个都是大同小异的。

一、PLL的添加

(1)打开interface desinger。

(2)选择pll右击选择Createblock,就可以添加pll

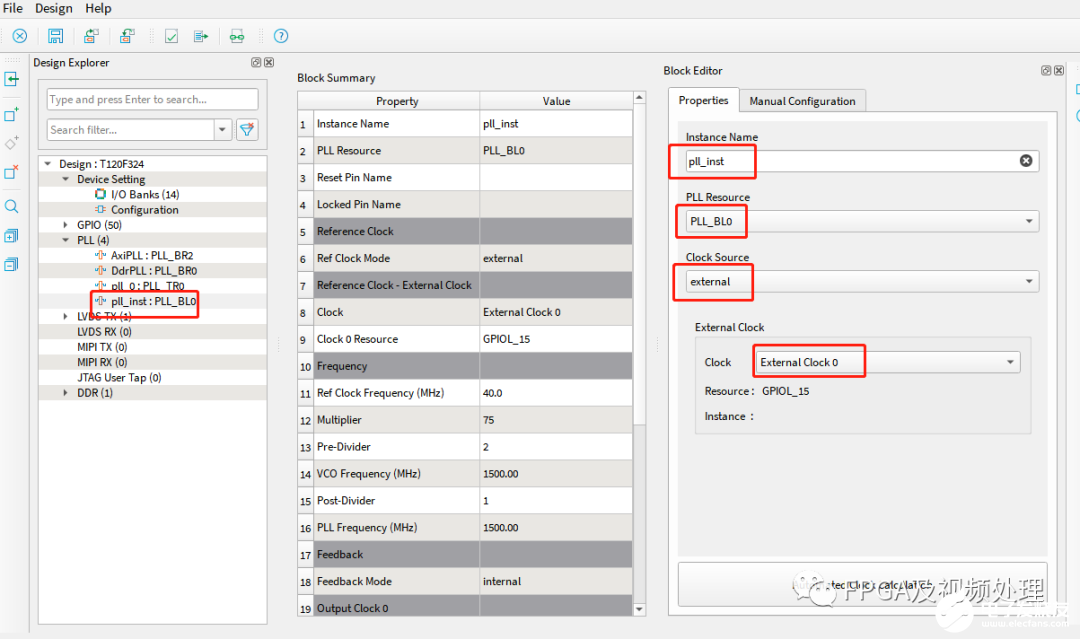

(3)这里我们把pll的例化名修改为pll_inst,并且按回车(必须回车)。

PLL resource对应PLL的位置,这也是易灵思的PLL使用与别家有区别的地方,必须要指定PLL的位置。

clock source是指pll参考时钟的源来自哪里,包括外部和内部。

External clock:指示参考时钟的源,包括参考时钟0,参考时钟1。

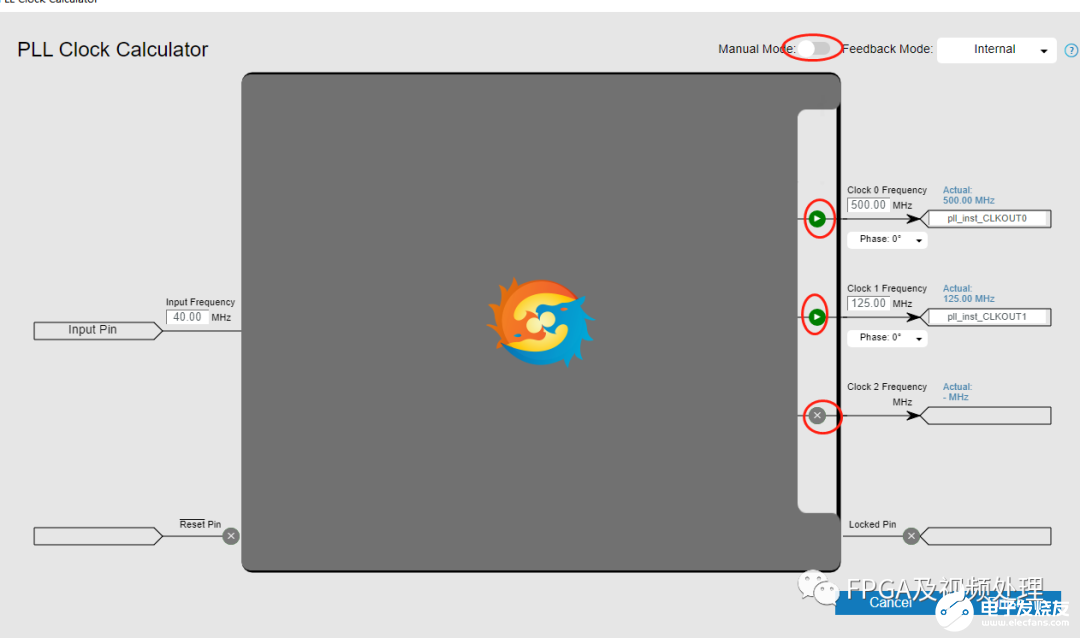

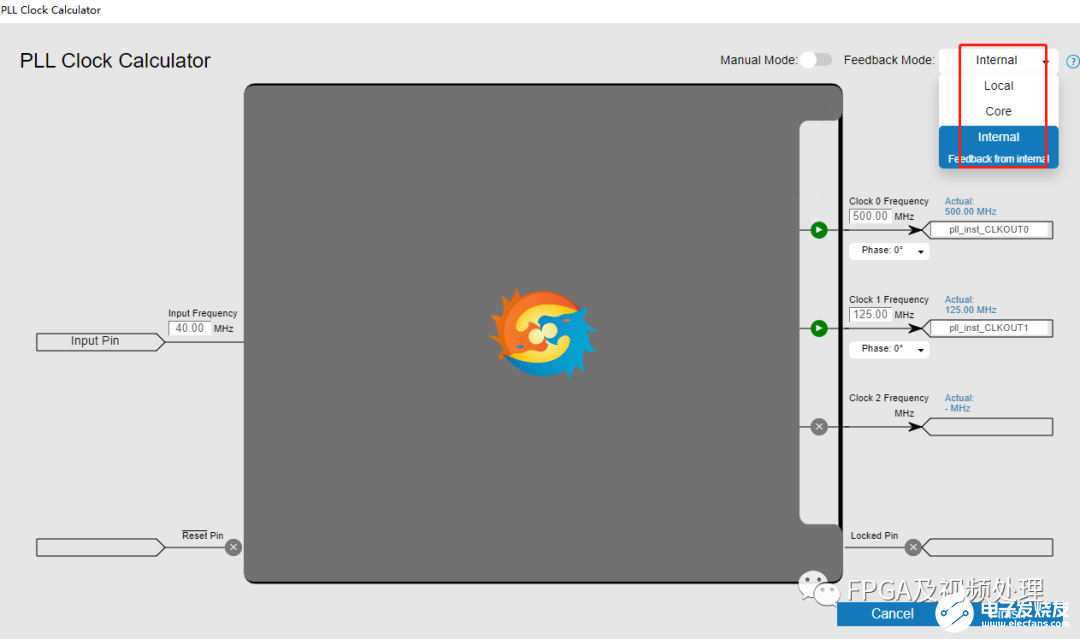

(4)点击Automated Clock Calculation打开时钟设置界面。trion最多可以设置3个时钟,红包框中的箭头和x可以用于打开和关闭相应的时钟。

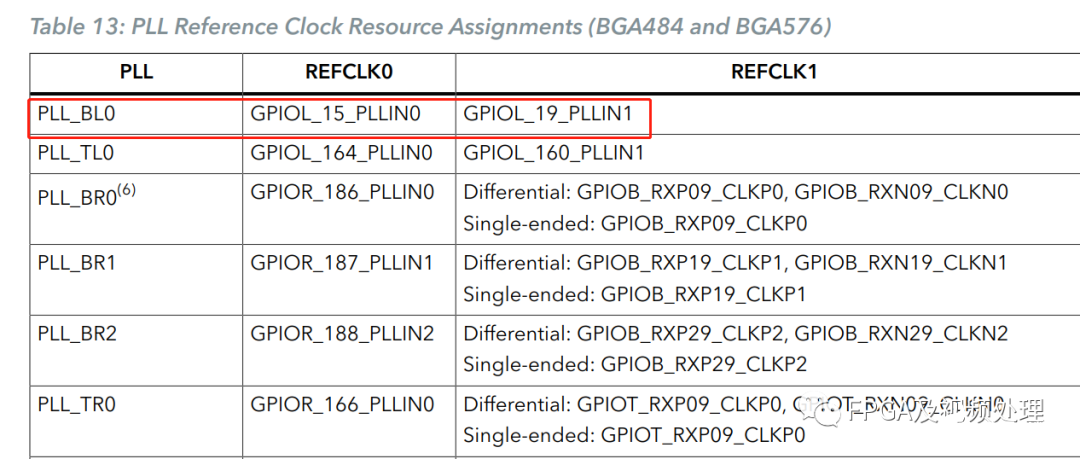

(5)设置完成上面的操作之后,我们需要指定PLL的参考时钟来源。从ds上我们可以看到PLL_BL0有两个时钟源,分别是REFCLK0和REFCLK1,分别对应GPIOL_15_PLLIN0和GPIOL_19_PLLIN1。

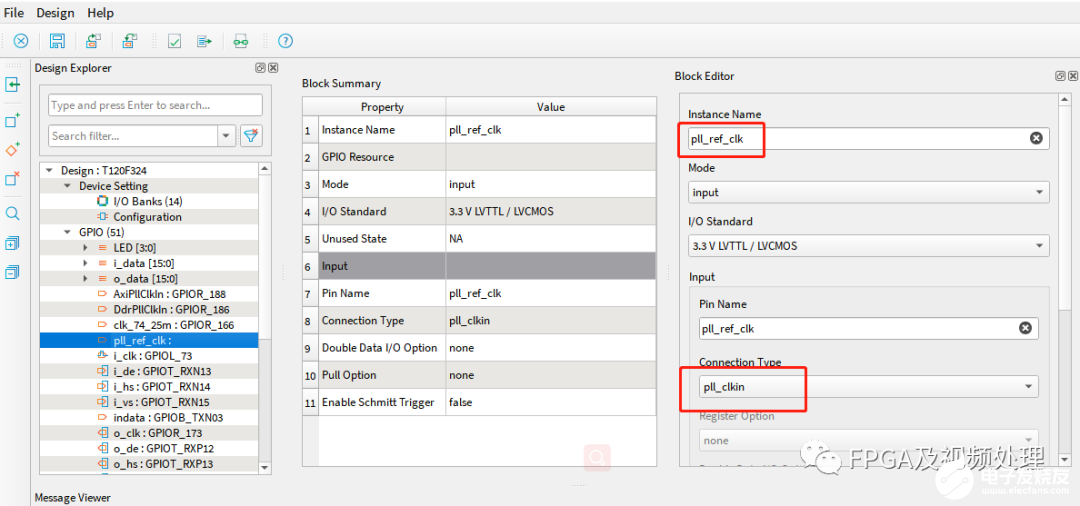

然后再添加PLL的参考时钟脚,这里我们例化为pll_ref_clk,并要把connection Type设置为pll_clkin。并分配到GPIOL_15_PLLIN0上,因为上面选择了External Clock0。这样PLL的设置就差不多了。

二、关于时钟源

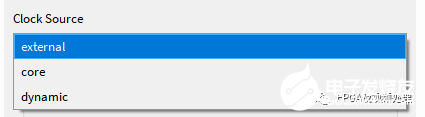

在选择clock source时,有三个选项,分别是external, core和dynamic。

external好理解,就是参考时钟从外部IO进入的,上面的设置就是。

core是指时钟从FPGA内部给PLL的参考,比如一个PLL的输出给另一个PLL做参考时,第二个PLL的参考就是设置成core,或者从GCLK进入FPGA再环到PLL的输入。

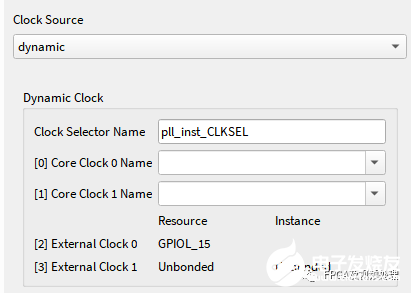

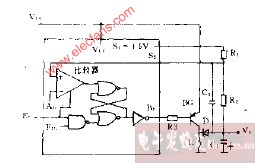

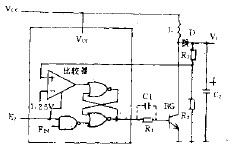

至于Dynamic Clock就是动态输入选择,支持多路选择,如下图,可以支持两个core和两个external时钟。但是因为PLL不支持动态重配置,所以这个功能应用有限。

三、PLL的反馈方式

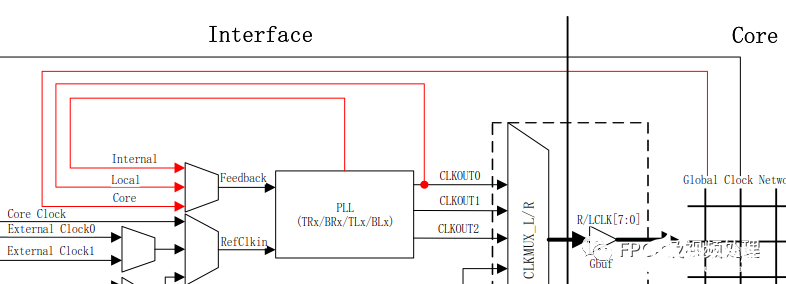

PLL有三种反馈,core,Local和internal。

从下面的图来看,不同的反馈位置是不一样的。core的反馈路径是从FPGA的core内部来反馈,可以保证输入时钟与输出时钟同频同相。这在源同步设计中是很有用的。而local和internal可以支持输出更多的频率,大家可以在操作中发现如果是core反馈的话,有些频率是设置不出来的,而local和interanl却可以。

上面描述其实描述相对粗糙,语句什么的也没有太去考虑措辞,花半个小时BB下,能用起来就行,如果实在有看不懂的,欢迎留言。

5、HSIO的解串器用法

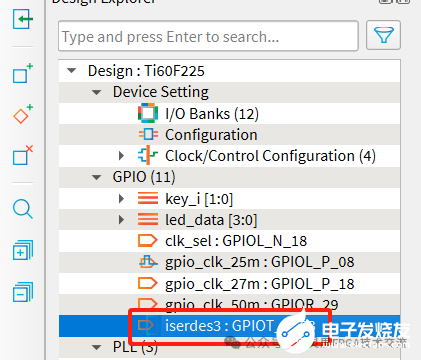

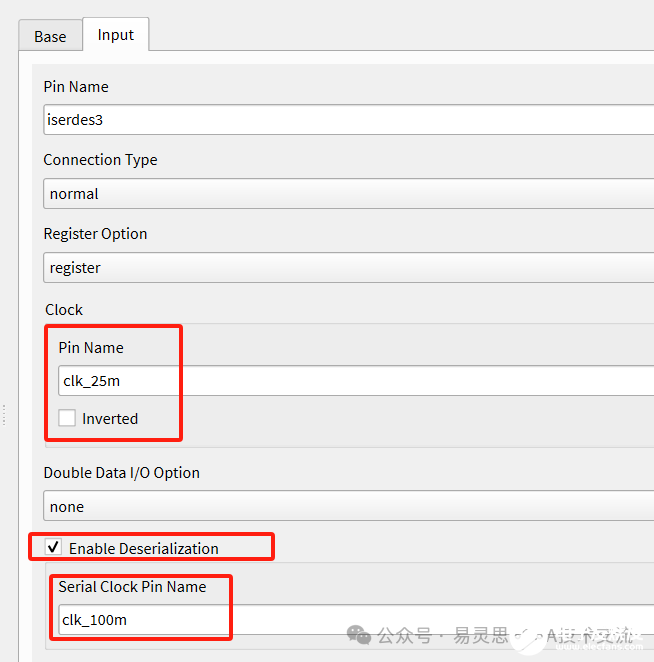

在interface中添加一个IO,注意要分给HSIO,HVIO是不支持4位解器的。这里我们定义一个iserdes3的GPIO,方向为输入。

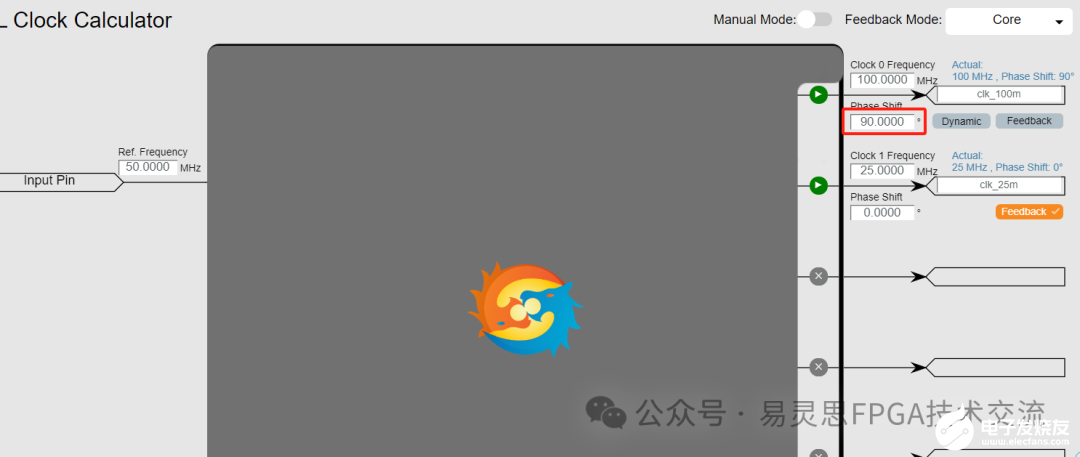

在GPIO的属性中,打开register,再打开Enable Deserialization就打开了解串器。Serial Clock Pin Name和Clock分别对应解串器的串行和并行时钟,需要指出的是在使用解串器时不能打开DDIO功能,所以串行时钟和并行时钟的关系只是能是4倍关系。

假如串行时钟是100MHz,那么转换成的4位并行数据就降速到25MHz。

在设置对应时钟时会有相位的要求。如果同相位会提示错误信息。

保存并点击生成约束之后,在生成的template文件中就可以看到生成的IO端口已经变成4位位宽。

(* syn_peri_port = 0 *) input [3:0] iserdes3,

-

Interface

+关注

关注

0文章

103浏览量

39753 -

desinger

+关注

关注

0文章

1浏览量

3528

发布评论请先 登录

ITIL V3白皮书

NODEMCU V3烧写 AT固件

NodeMCU V2 Amica V3 Lolin的盾牌

InterfaceDesinger 使用案例-v3

InterfaceDesinger 使用案例-v3

评论