引言

随着科学技术的飞速发展,特别是半导体制造工艺的进步,现场可编程门阵列(Field Programmable Gate Array, FPGA)的设计技术取得了显著进展。FPGA凭借其丰富的片内资源和固有的并行处理能力,在数字信号处理、硬件加速、汽车电子等领域得到了广泛应用。在图像采集与显示系统中,FPGA能够实现高速、并行的数据处理,显著提高系统的实时性和性能。本文设计了一个基于FPGA的图像采集与显示系统,详细阐述了系统的整体架构、模块功能及关键代码实现。

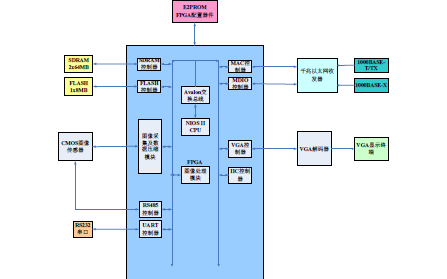

系统架构

本系统主要由图像采集子系统和图像显示子系统两部分组成。图像采集子系统负责从外部摄像头或其他图像传感器获取图像数据,并进行初步处理;图像显示子系统则将处理后的图像数据通过VGA接口显示在监视器上。

图像采集子系统

图像采集子系统包括RS232通信芯片、总线缓冲器、线阵电荷耦合器件(Charge Coupled Device, CCD)传感器、CCD缓冲放大器、CCD模数转换器(ADC)、双口随机存取存储器(Random-Access Memory, RAM)模块和图像采集模块。

- CCD传感器 :本系统采用东芝公司生产的TCD2566BFG彩色线阵图像传感器。该传感器灵敏度高、暗电流小,通过两相5V时钟脉冲驱动,含有3行彩色光电二极管阵列与1行黑白光电二极管阵列,每行阵列中光电二极管数量为5340个。

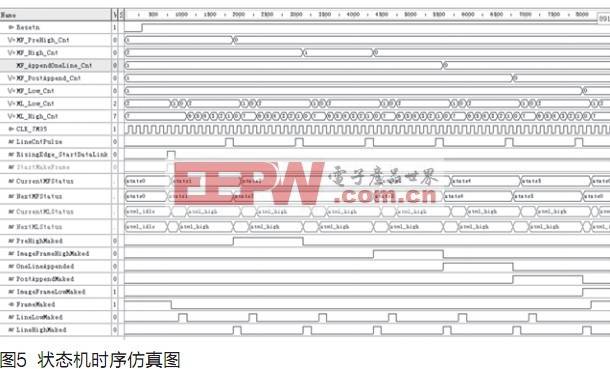

- 驱动模块 :图像采集模块的核心功能是驱动CCD传感器。该模块接收外部指令,配置CCD的行频和每英寸点数(Dots Per Inch, DPI),并产生CCD时钟脉冲与控制信号。在驱动CCD传感器前,需在驱动子模块内设置好CCD的行频与DPI。

- 信号传输与处理 :CCD传感器产生的模拟图像信号经过缓冲放大器传输至CCD专用模数转换器AD9945。AD9945完成图像信号的模数转换,并将采集到的一行数字图像信号写入片内双口RAM中。

图像显示子系统

图像显示子系统包括同步动态随机存储器(Synchronous Dynamic Random Access Memory, SDRAM)、视频解码芯片、VGA监视器、图像缓存模块和图像显示模块。

- SDRAM :本系统采用Hynix公司生产的HY57V64820HG芯片,位宽8bit,内含4个Bank,总存储空间为64MB,用于缓存双口RAM输出的图像信号。

- 视频解码芯片 :视频解码芯片采用Analog Devices公司生产的ADV7123KSTZ140,最高数据吞吐率为330MS/s,可将数字图像信号转换为VGA标准时序的模拟图像信号。

- 显示模块 :图像缓存模块与图像显示模块协同工作,将缓存的图像数据按照VGA时序送至VGA监视器显示。

模块详细设计

视频流采集设计

视频流采集设计主要关注摄像头接口的时序和图像数据的捕获。在FPGA内部,首先使用一个异步FIFO来同步外部输入的数据和FPGA内部逻辑。FIFO的读端口设计了一个简单的读控制状态机,当数据达到一定量时(如16个数据),连续读出这些数据,并送入DDR3写缓存FIFO中。

module fifo_controller(

input clk,

input rst_n,

input [7:0] data_in,

input fifo_full,

output reg fifo_wr_en,

output reg fifo_rd_en,

output reg [7:0] data_out

);

// FIFO读写控制逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

fifo_wr_en <= 1'b0;

fifo_rd_en <= 1'b0;

end else begin

// 写入控制逻辑

if (!fifo_full) begin

fifo_wr_en <= 1'b1; // 当FIFO未满时写入

end else begin

fifo_wr_en <= 1'b0;

end

// 读取控制逻辑(简化版,实际应更复杂)

if (/* 读取条件 */) begin

fifo_rd_en <= 1'b1; // 读取条件满足时读取

end else begin

fifo_rd_en <= 1'b0;

end

// 数据输出(这里仅示意)

if (fifo_rd_en) begin

data_out <= /* 从FIFO读出的数据 */;

end

end

end

DDR3缓存控制

DDR3缓存控制模块是连接图像采集子系统和图像显示子系统的关键部分。它负责将从视频流采集模块接收到的图像数据高效地写入DDR3内存,并在需要时从DDR3内存中读取这些数据以供显示。

DDR3接口设计

DDR3接口设计包括物理接口设计、控制逻辑设计和内存管理策略。

- 物理接口设计 :

DDR3的物理接口通常包括时钟信号(CK和CK#)、控制信号(如RAS#、CAS#、WE#、CS#等)和数据信号(DQ和DQS)。在FPGA设计中,这些信号需要通过专用的DDR3控制器IP核进行连接和配置。 - 控制逻辑设计 :

控制逻辑主要包括命令生成、地址生成和数据传输控制。命令生成负责根据内存管理策略生成必要的读写命令;地址生成则负责生成访问DDR3的起始地址和递增地址;数据传输控制则确保数据在正确的时钟周期内从FPGA的I/O口传输到DDR3接口。 - 内存管理策略 :

内存管理策略包括缓存策略、页管理和数据一致性检查。缓存策略决定了何时将数据从DDR3读取到FPGA的局部存储(如Block RAM)中,以及何时将数据写回DDR3。页管理涉及DDR3的页面开闭操作,以减少访问延迟。数据一致性检查确保在并发读写操作中数据的完整性和一致性。

DDR3写入流程

当视频流采集模块将图像数据写入FIFO后,DDR3写入控制模块会检查FIFO的满/空状态,并在FIFO非满时从FIFO中读取数据并写入DDR3。

DDR3缓存控制

DDR3缓存控制模块是连接图像采集子系统和图像显示子系统的关键部分。它负责将从视频流采集模块接收到的图像数据高效地写入DDR3内存,并在需要时从DDR3内存中读取这些数据以供显示。

DDR3接口设计

DDR3接口设计包括物理接口设计、控制逻辑设计和内存管理策略。

- 物理接口设计 :

DDR3的物理接口通常包括时钟信号(CK和CK#)、控制信号(如RAS#、CAS#、WE#、CS#等)和数据信号(DQ和DQS)。在FPGA设计中,这些信号需要通过专用的DDR3控制器IP核进行连接和配置。 - 控制逻辑设计 :

控制逻辑主要包括命令生成、地址生成和数据传输控制。命令生成负责根据内存管理策略生成必要的读写命令;地址生成则负责生成访问DDR3的起始地址和递增地址;数据传输控制则确保数据在正确的时钟周期内从FPGA的I/O口传输到DDR3接口。 - 内存管理策略 :

内存管理策略包括缓存策略、页管理和数据一致性检查。缓存策略决定了何时将数据从DDR3读取到FPGA的局部存储(如Block RAM)中,以及何时将数据写回DDR3。页管理涉及DDR3的页面开闭操作,以减少访问延迟。数据一致性检查确保在并发读写操作中数据的完整性和一致性。

DDR3写入流程

当视频流采集模块将图像数据写入FIFO后,DDR3写入控制模块会检查FIFO的满/空状态,并在FIFO非满时从FIFO中读取数据并写入DDR3。

module ddr3_write_controller(

input clk,

input rst_n,

input fifo_empty,

input fifo_full,

input [7:0] fifo_data,

output reg fifo_rd_en,

// DDR3接口信号

output reg [15:0] ddr3_addr,

output reg ddr3_wr_en,

output reg [31:0] ddr3_wdata,

// 其他DDR3控制信号...

);

// 状态机定义

typedef enum reg [1:0] {

IDLE,

READ_FIFO,

WRITE_DDR3

} state_t;

reg [1:0] state;

// DDR3写缓存

reg [31:0] ddr3_write_buffer[16]; // 假设缓存16个32位数据

integer write_idx = 0;

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

state <= IDLE;

fifo_rd_en <= 1'b0;

ddr3_wr_en <= 1'b0;

// 初始化DDR3写缓存...

end else begin

case (state)

IDLE: begin

if (!fifo_empty) begin

fifo_rd_en <= 1'b1;

state <= READ_FIFO;

end

end

READ_FIFO: begin

ddr3_write_buffer[write_idx] <= {fifo_data, 24'h00}; // 假设每次读取8位,扩展到32位

write_idx <= (write_idx + 1) % 16; // 循环使用缓存

if (write_idx == 0) begin // 缓存满

fifo_rd_en <= 1'b0;

state <= WRITE_DDR3;

end

end

WRITE_DDR3: begin

// 这里简化处理,实际应检查DDR3的写入状态

ddr3_addr <= /* 计算DDR3地址 */;

ddr3_wdata <= ddr3_write_buffer[0]; // 假设从缓存第一个位置开始写

ddr3_wr_en <= 1'b1;

// 假设每个时钟周期写入一个数据

if (/* DDR3写入完成条件 */) begin

// 移除已写入的数据

for (integer i = 0; i < 15; i = i + 1) begin

ddr3_write_buffer[i] <= ddr3_write_buffer[i+1];

end

ddr3_write_buffer[15] <= 32'h00000000; // 清除最后一个位置

// 检查是否还有数据需要写入

if (!fifo_empty) begin

state <= READ_FIFO; // 回到读取FIFO状态,继续填充缓存

end else begin

state <= IDLE; // FIFO为空,等待新数据

ddr3_wr_en <= 1'b0; // 停止写入DDR3

end

end

end

default: state <= IDLE;

endcase

end

end

// DDR3地址生成逻辑(简化示例)

// 这部分需要根据实际的内存映射和访问模式来设计

always @(posedge clk) begin

if (state == WRITE_DDR3) begin

// 假设使用简单的线性地址递增

ddr3_addr <= ddr3_addr + 16'h1000; // 每次增加4KB(假设每个数据块大小为4KB)

// 注意:这里需要确保地址不越界,并且根据DDR3的bank、row、column结构来正确设置地址

end

end

// DDR3接口的其他控制信号(如RAS#、CAS#等)应由DDR3控制器IP核管理

// 这里只展示了与数据写入直接相关的信号

// 注意事项:

// 1. DDR3的访问通常需要复杂的时序控制,包括预充电、激活、写入等命令的精确时序。

// 这些通常通过DDR3控制器IP核内部的逻辑来管理,但开发者需要正确配置IP核的参数和接口。

// 2. DDR3的页管理也非常重要,因为DDR3是基于页面的内存架构。

// 在写入新数据时,可能需要先关闭当前页面并激活新页面。

// 3. 数据一致性和缓存策略是设计高性能DDR3接口时需要考虑的关键因素。

// 例如,可以使用写回(Write-Back)或写直达(Write-Through)缓存策略,以及使用缓存一致性协议(如MESI)来确保数据的一致性。

DDR3读取流程

DDR3读取流程与写入流程类似,但方向相反。当图像显示子系统需要从DDR3中读取图像数据时,DDR3读取控制模块会生成相应的读取命令和地址,并将读取到的数据通过FIFO或其他缓冲机制传输给显示子系统。

module ddr3_read_controller(

// 输入输出端口与ddr3_write_controller类似,但包括读取相关的信号

// ...

// 读取数据输出到FIFO

output reg fifo_wr_en,

output reg [7:0] fifo_data_out,

// 其他DDR3控制信号...

);

// 状态机定义

typedef enum reg [1:0] {

IDLE,

READ_DDR3,

WRITE_FIFO

} state_t;

reg [1:0] state;

// DDR3读缓存(如果需要的话,可以根据实际情况设计)

// ...

// FIFO写使能逻辑

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

fifo_wr_en < = 1'b0;

end else begin

case (state)

WRITE_FIFO: begin

fifo_wr_en <= 1'b1; // 写入FIFO

fifo_data_out <= ddr3_read_data[7:0]; // 假设ddr3_read_data为DDR3控制器提供的读取数据

// 根据实际情况处理FIFO的满状态

// ...

// 检查是否完成所有数据的写入

// ...

// 如果完成,则回到IDLE状态

// ...

end

default: fifo_wr_en <= 1'b0;

endcase

end

end

// DDR3读取控制逻辑(简化示例)

// 这部分逻辑将依赖于DDR3控制器IP核提供的读取接口

// 通常需要处理读取命令的发送、读取数据的接收以及读取状态的监测

// ...

// 注意事项:

// 1. DDR3读取同样需要精确的时序控制,但通常这些控制由DDR3控制器IP核内部完成。

// 2. 读取过程中可能会遇到等待状态(如DDR3忙、页面未激活等),需要合理处理这些状态以避免死锁或性能下降。

// 3. 数据从DDR3读取到FPGA内部后,可能需要进行格式转换、缩放、裁剪等预处理操作,以满足显示子系统的要求。

性能优化与错误处理

在设计DDR3缓存控制模块时,性能优化和错误处理是非常重要的方面。以下是一些关键的优化和错误处理策略:

- 并行处理 :为了提高性能,可以设计多个并行的读写通道,同时处理多个数据块的读写操作。这需要在FPGA内部合理分配资源,并确保不同通道之间的数据一致性和独立性。

- 流水线设计 :引入流水线技术可以显著提升DDR3访问的效率。通过将DDR3的访问过程(如命令发送、数据等待、数据读取/写入等)划分为多个阶段,并让这些阶段在时间上重叠,可以大幅减少等待时间,提高吞吐量。例如,在写入过程中,可以在等待DDR3响应上一个写入命令的同时,准备下一个写入命令和数据。

- 缓存策略 :合理的缓存策略对于提高DDR3访问效率至关重要。常见的缓存策略包括写回(Write-Back)和写直达(Write-Through)两种。写回策略将修改后的数据先存储在缓存中,待缓存满或达到特定条件时再写回DDR3,这可以减少对DDR3的直接访问次数,但可能增加数据一致性的维护难度。写直达策略则直接将数据写入DDR3,避免了缓存带来的延迟,但可能会增加DDR3的访问频率。

- 突发传输 :DDR3支持突发传输(Burst Transfer),即在一次访问中连续传输多个数据字。利用突发传输可以显著减少命令发送的次数和等待时间,提高数据传输的效率。但是,也需要注意不要造成突发传输的浪费,即尽量确保每次突发传输都传输了足够的数据量。

- 错误检测与纠正 :DDR3接口可能会遇到各种错误,如数据位错误、地址错误、时序错误等。为了保证数据的可靠性,需要实现相应的错误检测与纠正机制。常见的错误检测方法包括奇偶校验(Parity Check)、循环冗余校验(CRC)等。对于可纠正的错误,如单比特错误,可以使用ECC(Error Correction Code)等技术进行纠正。对于不可纠正的错误,则需要通过错误报告和重试机制来处理。

- 电源与时钟管理 :DDR3的访问效率还受到电源和时钟管理的影响。稳定的电源供应和精确的时钟同步是确保DDR3稳定工作和高性能访问的基础。在设计中,需要合理规划电源网络,确保DDR3控制器及其周边电路的电源稳定可靠;同时,还需要精确控制时钟信号的生成和分布,以减小时钟偏差和抖动对DDR3访问性能的影响。

- 性能监测与调优 :在实际应用中,DDR3缓存控制模块的性能可能会受到多种因素的影响,如FPGA内部的资源分配、DDR3控制器的配置、外部电路的干扰等。为了获得最佳的性能表现,需要对DDR3缓存控制模块进行性能监测和调优。可以通过添加性能计数器来监测关键指标(如访问延迟、吞吐量、错误率等),并根据监测结果对设计进行调整和优化。

应用场景与案例分析

DDR3缓存控制模块在多种应用场景中发挥着重要作用,特别是在需要高速数据处理的领域,如图像处理、视频编解码、网络通信等。以下是一个基于FPGA的图像处理系统中DDR3缓存控制模块的应用案例。

案例背景 :

某图像处理系统需要实时处理来自摄像头的视频流数据,并将处理后的结果输出到显示设备。由于视频数据量大、处理复杂度高,因此需要设计一个高效的DDR3缓存控制模块来存储和传输数据。

设计目标 :

- 实现高速的数据读写操作,以满足实时处理的需求。

- 优化缓存策略,减少DDR3的访问次数和等待时间。

- 引入错误检测与纠正机制,确保数据的可靠性和完整性。

设计方案 :

- 并行处理与流水线设计 :设计多个并行的读写通道,每个通道负责处理一部分视频数据。同时,引入流水线技术,将DDR3的访问过程划分为多个阶段,以实现高效的数据传输。

- 缓存策略优化 :根据视频数据的特性和处理需求,选择合适的缓存策略。例如,在处理过程中可以引入局部缓存来暂存即将处理的数据块,以减少对DDR3的直接访问。同时,利用DDR3的突发传输特性,优化数据块的读写操作。

- 错误检测与纠正 :为DDR3缓存控制模块添加ECC等错误检测与纠正机制,确保在数据传输和存储过程中及时发现并纠正错误。

- 性能监测与调优 :在系统中添加性能监测模块,实时监测DDR3缓存控制模块的性能指标。根据监测结果对设计进行调整和优化,以获得最佳的性能表现。

实施效果 :

通过实施上述设计方案,该图像处理系统成功实现了高速的数据读写操作,满足了实时处理的需求。同时,由于采用了合理的缓存策略和错误检测与纠正机制,系统的数据可靠性和稳定性也得到了显著提升。此外,通过性能监测与调优,系统的整体性能得到了进一步优化,达到了预期的设计目标。

结论与展望

DDR3缓存控制模块作为FPGA与DDR3存储器之间的桥梁,在高速数据处理系统中发挥着至关重要的作用。通过合理的设计和优化,可以显著提升系统的数据处理能力和性能表现。未来,随着技术的发展和应用的不断扩展,DDR3缓存控制模块将面临更多的挑战和机遇。例如,随着DDR4、DDR5等新一代存储技术的推出,DDR3缓存控制模块可能需要进行相应的升级和改造,以兼容和支持这些新技术。同时,随着AI、大数据、云计算等领域的快速发展,对高速、大容量数据存储和处理的需求将不断增加,这也将对DDR3缓存控制模块的设计和优化提出更高的要求。

在未来设计中,可以考虑以下几个方面来进一步提升DDR3缓存控制模块的性能和可靠性:

- 高级缓存算法 :引入更先进的缓存替换算法,如LRU(最近最少使用)或LFU(最不经常使用),以提高缓存命中率,减少DDR3的访问次数。同时,可以设计多级缓存结构,利用FPGA内部的SRAM资源构建快速的本地缓存,以减少对DDR3的依赖。

- 动态资源分配 :根据系统的实时负载和性能需求,动态调整DDR3缓存控制模块的资源分配。例如,在处理高峰时段,可以增加并行处理通道的数量或提高缓存的大小,以应对更大的数据量;而在负载较低时,则可以减少资源占用,以节省功耗。

- 智能调度与仲裁 :设计智能的调度与仲裁机制,以优化多个并行读写通道之间的数据访问顺序。通过预测和优先级调度,可以减少冲突和等待时间,提高整体的数据传输效率。

- 低功耗设计 :随着对能效要求的提高,低功耗设计将成为DDR3缓存控制模块的重要考虑因素。可以通过优化时钟管理、降低工作电压、使用低功耗的FPGA器件等方式来降低功耗。此外,还可以设计功耗感知的调度算法,根据系统的功耗预算动态调整工作模式。

- 安全性增强 :在数据处理和存储过程中,安全性也是不可忽视的问题。可以为DDR3缓存控制模块添加加密解密模块,对敏感数据进行加密存储和传输,以防止数据泄露。同时,还可以设计安全认证机制,确保只有授权用户才能访问DDR3中的数据。

- 标准化与模块化 :为了提高设计的可重用性和可维护性,可以将DDR3缓存控制模块设计为标准化的模块。通过定义清晰的接口和协议,可以方便地将该模块集成到不同的系统中。此外,还可以将模块划分为多个子模块,每个子模块负责特定的功能,以降低设计的复杂度和提高开发效率。

- 实时性能监控与自适应调整 :在DDR3缓存控制模块中集成实时性能监控功能,可以实时监测系统的性能指标(如延迟、吞吐量、错误率等)。根据监控结果,可以自动调整缓存策略、并行通道数量等参数,以实现性能的自适应优化。

- 跨平台兼容性 :随着多平台、多架构系统的普及,DDR3缓存控制模块需要具备良好的跨平台兼容性。通过设计通用的接口和协议,可以确保该模块能够灵活地集成到不同的硬件平台上,满足多样化的应用需求。

综上所述,DDR3缓存控制模块的设计和优化是一个涉及多个方面的复杂任务。通过不断探索和创新,可以不断提升该模块的性能和可靠性,为高速数据处理系统提供更加坚实的支撑。同时,随着技术的不断发展和应用需求的不断变化,DDR3缓存控制模块的设计也将不断面临新的挑战和机遇。

-

FPGA

+关注

关注

1628文章

21722浏览量

602870 -

图像采集

+关注

关注

2文章

299浏览量

41269 -

显示系统

+关注

关注

1文章

141浏览量

24259

发布评论请先 登录

相关推荐

【工程源码】基于FPGA的OV5640数据流接收和应用基本逻辑设计

基于Zedboard FPGA的VGA图像信号采集系统的设计

基于Xilinx FPGA的视频图像采集系统

如何利用FPGA来设计一个视频图像采集及显示系统并使用详细资料概述

基于FPGA的图像采集与显示系统设计

基于FPGA的图像采集与显示系统设计

评论