本文主要讲解的是FPGA高速收发器的来源,着重从三个方面解析,可能部分理解会存在有错误,想要不一致的可以来评论区交流哦。

01回顾其余接口

首先应该了解这种接口出现的原因,为什么会有这种接口出现,就拿ADC芯片的接口举例吧。

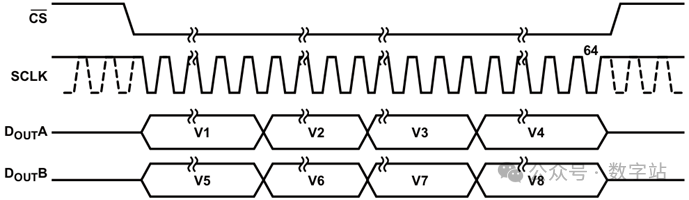

下图是ad7606芯片的串行数据传输模式的时序图,像这种采样率较低,一般小于1MHz。一般使用spi这种低速接口即可,也是出现比较早的接口。

图1 ad7606时序图

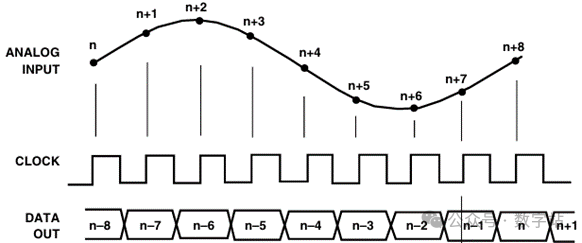

下图ad9226的时序图,接口包含一根时钟线CLOCK和一组数据线DATA OUT,每个时钟传输一个数据,时钟频率最大可以达到65MHz。

图2 ad9226时序图

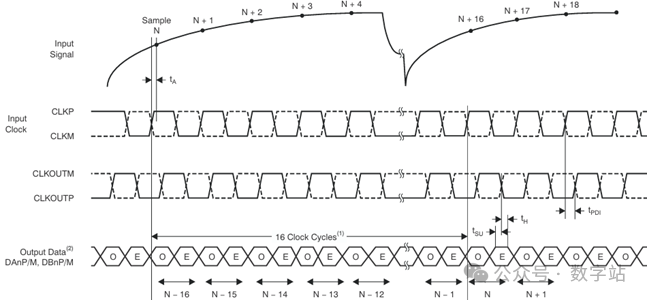

之后ADC芯片的采样率进一步提升,高于100MHz,为了提高数据传输的稳定性,将时钟和数据都变为差分信号,增加抗干扰能力。如下图是ads4225的LVDS接口时序图。

图3 ADS4225的LVDS接口时序图

上述ad9226和ads4225的LVDS并行接口,时钟线和数据线都要保证等长。

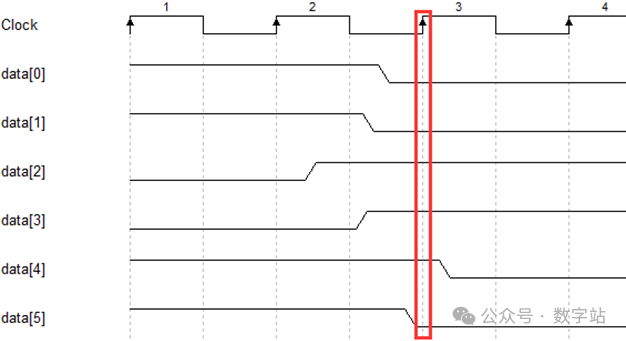

举个例子,如下图所示,在时钟上升沿采集data的数据,由于data数据线并没有严格等长,data[2]的线比较短,第二个时钟上升沿之后一段时间就传输到FPGA的端口寄存器了,data[4]的走线比较长,第三个时钟上升沿之后都没有传输到FPGA的端口寄存器,那么在clk第三个时钟上升沿会采集到错误数据。这就是为什么数据线和时钟线均要做等长的原因。

这种少数走线差别可以通过FPGA的input delay进行约束,需要计算每根线的PCB走线延迟,输出寄存器延时等等,会比较麻烦,并且不能对代码进行移植,所以对于这种并行传输的接口在设计PCB时数据线和时钟线必须做等长处理。

图4 并行数据传输

但LVDS的数据线和时钟线都是差分信号,导致数据线很多,等长处理很麻烦,但是还能有效果。比如时钟频率200MHz,那么数据只要在5ns之内能够稳定传输到输入寄存器也没有问题,即使每根走线之间有点差距,也问题不大。

但如果时钟频率继续增加,就要求增加走线等长的精度。当数据传输速率大于2Gbps时,时钟周期小于0.5ns,此时即使微小的等长差距也会引发错误,甚至无法完成这样的PCB布线。

在这种传输速率下,并行接口将不再合适,进而推出了高速串行接口。

高速串行接口取消了时钟线,只有一对差分数据线,接收端通过CDR技术从串行数据中恢复时钟信号,之后将数据与时钟同步给用户。像PCIE、JE204B接口均是高速串行接口。

使用串行接口就可以避免时钟同步和多位宽数据等长问题,但是对于恢复时钟和数据接收难度就增大了,发展到如今,高速串行接口也已经很成熟了。

02FPGA中其余接口

FPGA内部包含普通bank和gt bank两种,后者就是高速收发器所在bank。xilinx的芯片根据架构不同,包含不同类型的bank,其中A7只有HR bank,而K7除此之外还包含HP bank。下文将展示这些普通bank能够达到的数据传输速率。

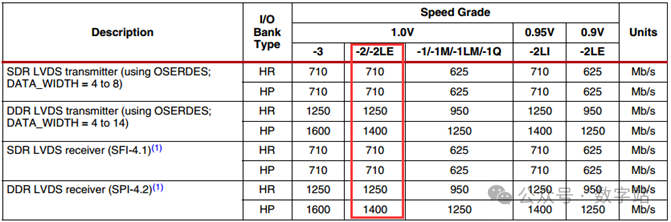

如下图所示,以K7为例,平常使用芯片速度等级大多为-2,因此以-2举例。HP和HR bank的单沿数据传输速率均可以达到710Mb/s。

图5 接口性能

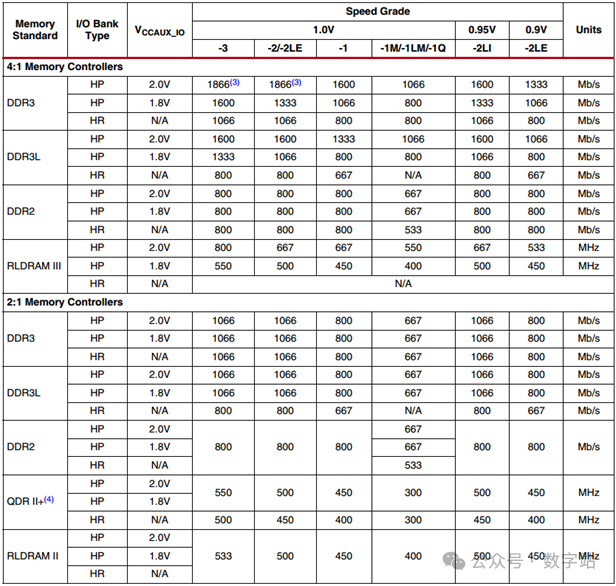

对于K7的DDR3硬核数据收发速率基本可以达到1600Mb/s以上,如下图所示。

图6 K7内存接口IP的最大物理接口速率

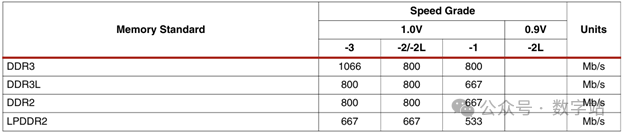

下图是A7的DDR控制器的数据收发速率,一般在800Mb/s左右,是K7速率的一半。

图7 A7内存接口IP的最大物理接口速率

由上述可知,除了DDR硬核控制器之外,HP和HR bank的ISERDES和OSERDES即使能够实现单沿并行数据与双沿串行数据的转换,但是数据传输的速率依旧不是很高。如果要应对高速ADC和PCIE这些接口,显然速率不够。

03Gigabyte Transceiver

基于上述原因,xilinx就推出了Gigabyte Transceiver。Xilinx 7系列的FPGA支持的GT一共有四种,分别为:GTP,GTX,GTH,GTZ,区别在于线速率不同。

其中GTP被用于A7系列,GTX通常被用于K7系列,GTH一般被用于V7系列,GTZ被用于少数V7系列。

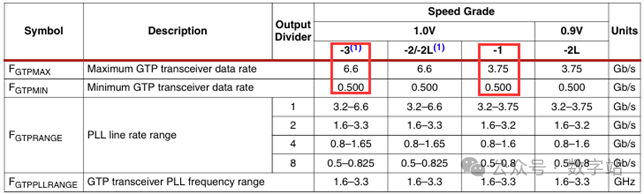

GTP线速率可以达到6.6Gb/s,具体速率与芯片的速度等级有关,如下表所示,速度等级为-2的芯片线速率可以达到6.6Gb/s。

图8 GTP速率

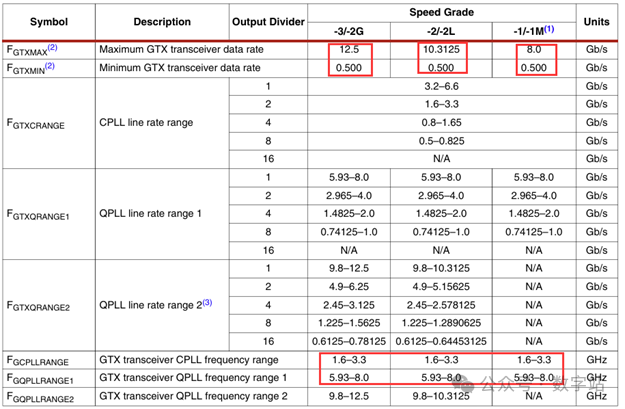

GTX线速率可以达到12.5Gb/s,我用的芯片型号为xc7z030ffg676-2,因此速率可以达到10.3125Gb/s,可以实现万兆网传输。从下图知最大速率与QPLL和CPLL也有关,当线速率大于5.93GHz时使用QPLL。

图9 GTX速率

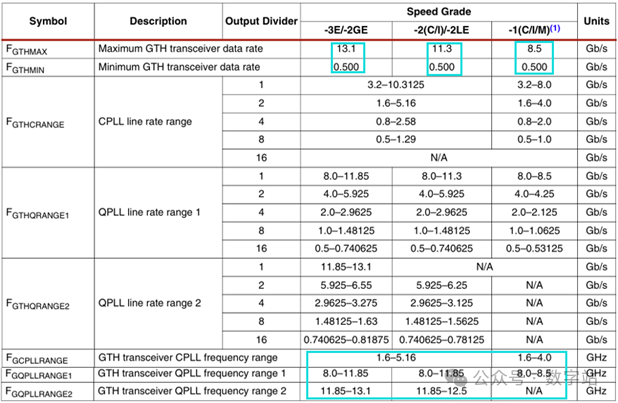

GTH线速率可以达到13.1Gb/s,如下图所示,GTZ线速率可以达到28.05Gb/s,暂时没有找到其数据手册。

图10 GTH速率

关于GT收发器出现背景以及HP、HR bank、高速收发器的速率就讲解到这里吧。

来源:本文转载自数字站公众号

-

FPGA

+关注

关注

1664文章

22508浏览量

639431 -

收发器

+关注

关注

10文章

3840浏览量

111471 -

接口

+关注

关注

33文章

9603浏览量

157654 -

adc

+关注

关注

100文章

7950浏览量

556938

原文标题:FPGA高速收发器的来源

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA设计之GTP、GTX、GTH以及GTZ四种串行高速收发器

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平 ...

关于FPGA如何连接CAN收发器?

FPGA高速收发器设计要遵循哪些原则?

FPGA高速收发器设计原则

Xilinx推出UltraScale FPGA收发器设计

40-nm收发器FPGA和ASIC系列的特点

高速ADC与高速串行收发器

基于XilinxVirtex®-6FPGA 11.18 Gbps收发器的高速互操作性

Logos系列FPGA高速串行收发器(HSST)用户指南

FPGA高速收发器的来源

FPGA高速收发器的来源

评论