PMOS(Positive channel Metal Oxide Semiconductor,P 沟道金属氧化物半导体)工艺制程技术是最早出现的MOS 工艺制程技术,它出现在20世纪60年代。早期的 PMOS 栅极是金属铝栅,MOSFET 的核心是金属-氧化物-半导体,它们组成电容,形成电场,所以称为金属氧化物半导体场效应管。PMOS 是制作在n型衬底上的p沟道器件,采用铝栅控制器件形成反型层沟道,沟道连通源极和漏极,使器件开启导通工作。PMOS 是电压控制器件,依靠空穴导电工作。由于空穴的迁移率较低,所以PMOS 的速度很慢,最小的门延时也要80 ~ 100ns 。

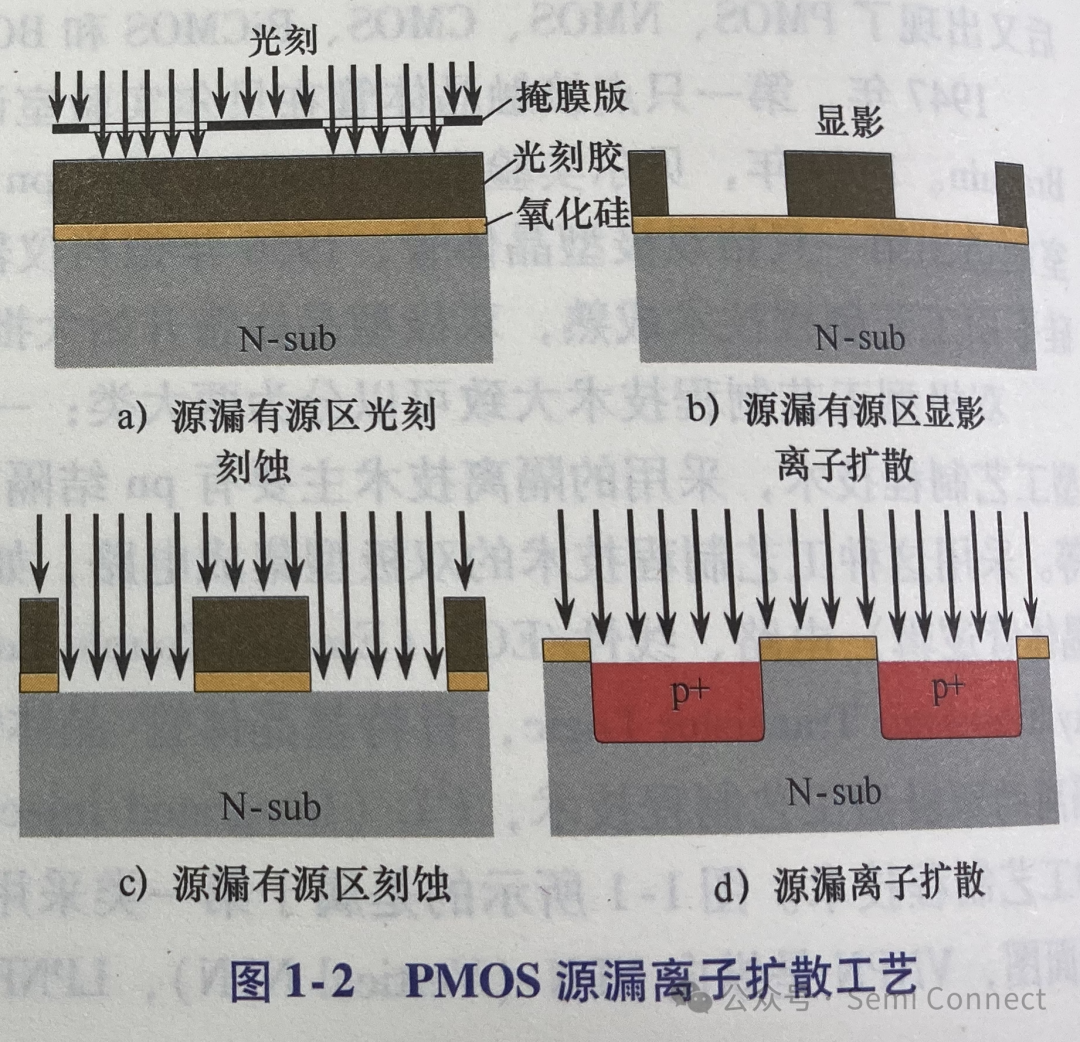

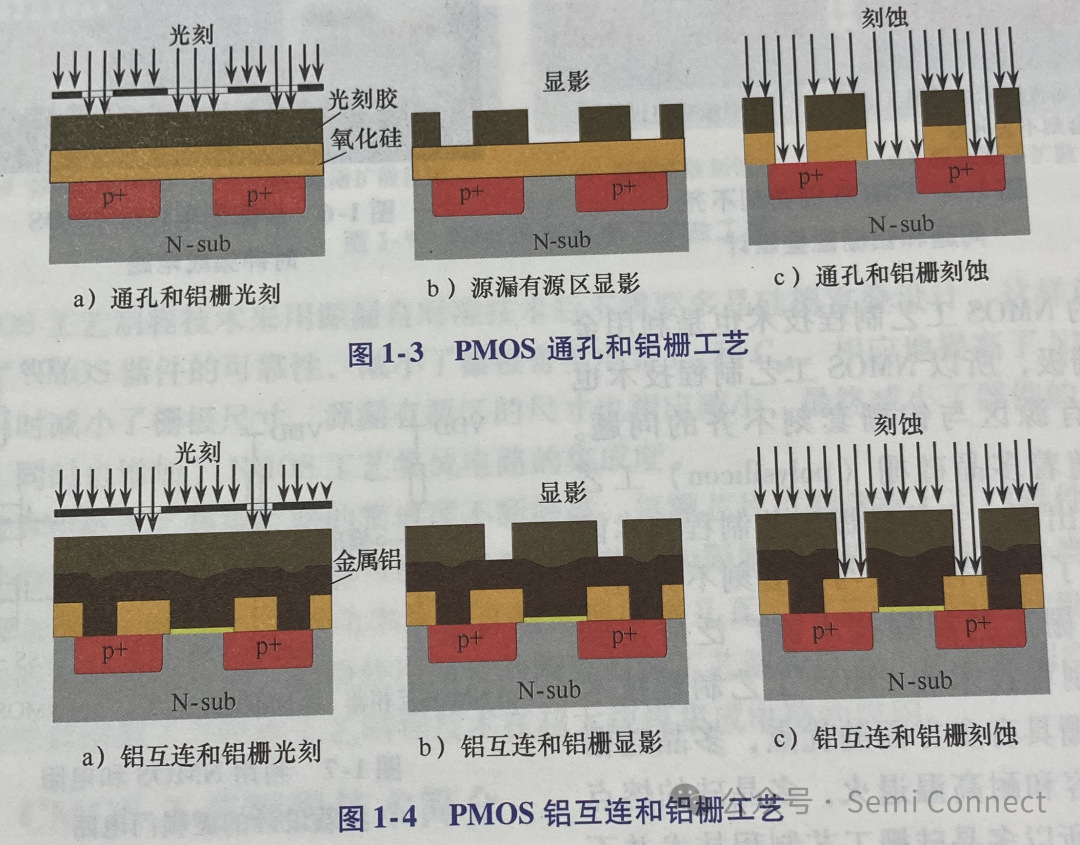

由于 PMOS 源漏离子扩散后需要高达900°C的高温工艺进行退火激活,而铝栅的熔点是660°C,不能承受900°C的高温,所以 PMOS的铝栅必须在源漏有源区形成之后再经过一道光刻和刻蚀形成的,这就造成了形成源漏有源区与制造铝栅需要两次光刻步骤,这两次光刻形成的图形会存在套刻不齐的问题。如图1-2 所示为形成 PMOS 源漏有源区的工艺步骤,包括图1-2a的光刻、图1-2b的显影、图1-2c的刻蚀和图1-2d的离子扩散。N-sub(N-substrate)是n型衬底。图1-3所示为形成PMOS 通孔和铝栅的光刻和刻蚀。图1-4所示为形成PMOS 铝互连和铝栅的光刻和刻蚀。图1-5a 所示为形成 PMOS 铝栅后的剖面图,源漏有源区的边界与铝栅产生交叠或者间距问题。当源漏有源区与铝栅套刻不齐时会造成器件尺寸误差和电性参数误差,也会造成器件无法形成沟道或者沟道中断等问题从而影响器件性能。为了解决这些问题,在PMOS 版图设计上采用铝栅重叠设计,也就是铝栅的版图长度要比PMOS的实际沟道要长一些,这样就造成铝栅与源漏有源区产生重叠,如图1-5b所示,这种铝栅重叠设计会导致栅极寄生电容Cgs(铝栅与源极的寄生电容)和Cgd(铝栅与漏极的寄生电容)增大,另外也增加了栅极长度,所以也会增加器件的尺寸,降低了集成电路的集成度。因为集成电路的集成度较低,所以 PMOS工艺制程技术只能用于制作寄存器等中规模集成电路。

PMOS 是电压控制器件,它的功耗很低,它非常适合应用于逻辑运算集成电路。但是PMOS 的速度很慢,所以PMOS 工艺集成电路主要应用于手表和计算器等对速度要求非常低的领域。

图1-6所示为1974年加德士半导体利用 PMOS设计的时钟集成电路。

-

半导体

+关注

关注

334文章

27285浏览量

218010 -

场效应管

+关注

关注

46文章

1162浏览量

63907 -

PMOS

+关注

关注

4文章

245浏览量

29551 -

工艺制程

+关注

关注

0文章

57浏览量

12998

原文标题:PMOS 工艺制程技术简介

文章出处:【微信号:Semi Connect,微信公众号:Semi Connect】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

半导体工艺几种工艺制程介绍

《炬丰科技-半导体工艺》超大规模集成电路制造技术简介

PMOS和NMOS哪个更适合用于电源开关

制程工艺是什么?

PMOS工艺制程技术简介

PMOS工艺制程技术简介

评论