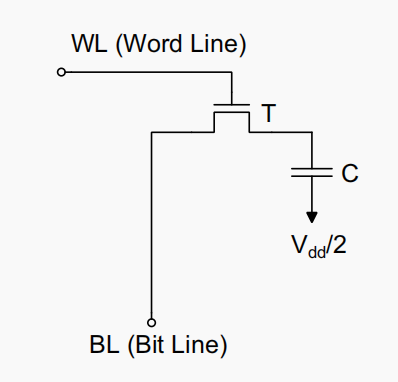

一个电容节点连接到Vdd/2。如果电容器存储“1”,则电容器之间的电压为+Vdd/2,如果电容器保存“0”,则电容之间的电压为-Vdd/2)。存储在电容器中的电荷等于电容乘以电容器两端的电压:

Q = C × Vdd /2

在90nm DRAM工艺中,DRAM存储单元的电容为30 fF。如果我们假设Vdd=3.3V,那么

Q = 30 f F × 3.3V/2 = 34.5 f C.

你可能还记得,在物理课上,一个电子等于1.6·10^-19C的电荷,因此存储电容器只存储了210000个电子!即使晶体管在关断时,电阻非常高,电容器上的电荷也会在几~几百毫秒内通过被关断的晶体管泄漏出去。因此,DRAM存储单元应定期刷新,以避免数据丢失。

通过将“1”或“0”电荷放入存储电容,将数据写入存储单元。要将数据写入单元,我们首先设置位线并拉高字线将电容连接到位线。然后,在字线被拉低和晶体管被关闭之后,存储电容器保留了存储的电荷。存储电容上的电荷会慢慢泄漏,所以如果不进行干预,芯片上的数据很快就会丢失。

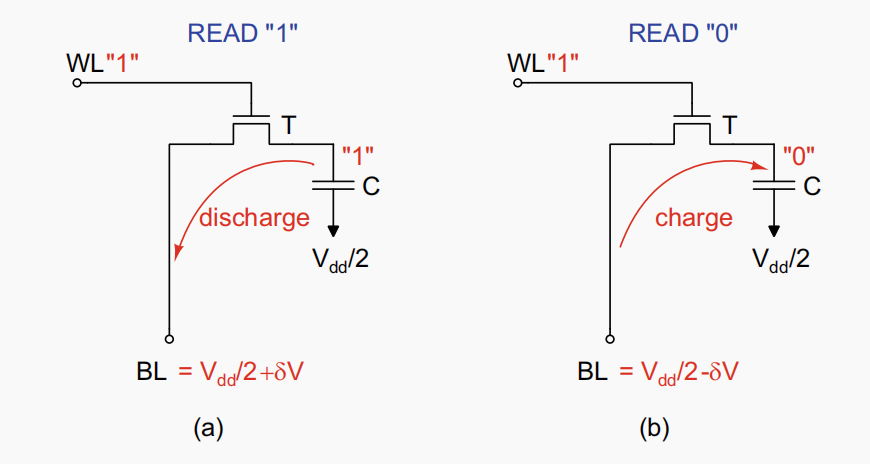

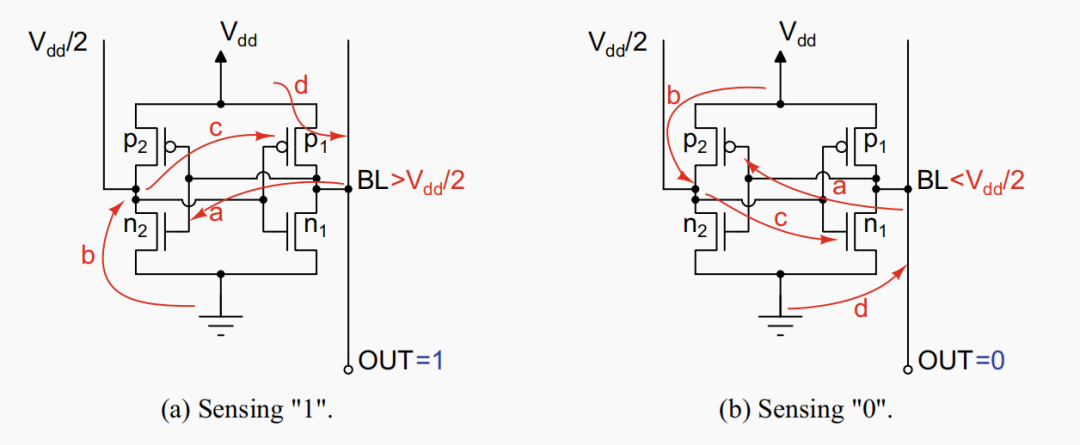

要从DRAM单元读取数据,位线首先预充电到Vdd/2。然后将字线驱动到高电平,以将单元的存储电容器连接到其位线。这导致晶体管导通,将电荷从存储单元转移到连接的位线(如果存储值为“1”),或从连接的位线上转移到存储单元(如果存储数值为“0) 。这一过程如图所示。

在这两种情况下,存储在DRAM单元中的信息都会丢失。因此,从DRAM读取是一种破坏性操作。

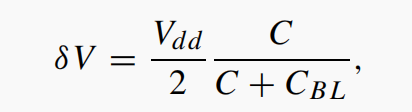

根据电荷共享方程(电容分压器),读出时位线上的电压摆幅(电压差的大小)为

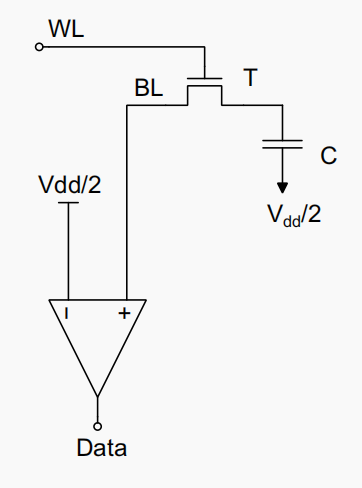

其中C是存储电容器的电容,CBL是位线的电容。如果位线的电容是存储电容的10倍,Vdd=3.3V,则读取操作时位线上的电压差仅为150mv!当处理这样一个微小的电压摆幅时,正确地检测位值是一个相当大的挑战。因此,我们需要一个特殊的电路来感测这个小的电压摆幅。用于检测电压摆幅和读取数据的专用电路是一个读出放大器sense amplifier。

放大器有两个输入。.一个输入端连接到位线,另一个输入端连接到Vdd/2。放大器检测其输入端的电压差,如果位线上的电压小于Vdd/2,则在数据端输出0,否则输出1。

-

电容器

+关注

关注

64文章

6215浏览量

99516 -

DRAM

+关注

关注

40文章

2309浏览量

183422 -

晶体管

+关注

关注

77文章

9679浏览量

138050

原文标题:DRAM的基本操作

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

[分享]直接总线式DRAM的信号连接

DRAM内存原理

【内存知识】DRAM芯片工作原理

请教关于C6748 L1DRAM cache 的问题?

FPGA DRAM数据错位

DRAM存储原理和特点

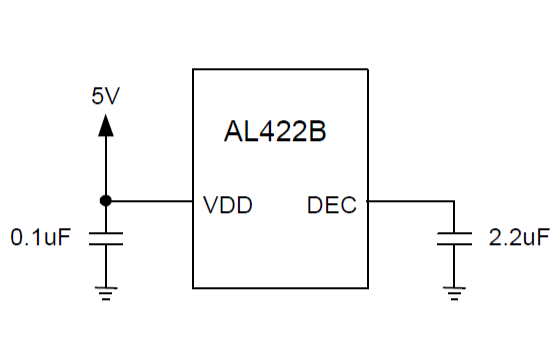

AL422 3M位FIFO现场存储器的数据手册免费下载

现场存储器AL422数据手册

DRAM内存操作与时序解析

DRAM的基本操作

DRAM的基本操作

评论