在数字电路中,锁存器和触发器是两种非常重要的存储元件,它们在逻辑功能上有着明显的区别。锁存器和触发器都是用于存储二进制信息的基本元件,但它们在结构、工作原理、应用场景等方面都存在差异。

一、锁存器(Latch)

1.1 锁存器的定义

锁存器是一种在数字电路中用于存储一位二进制信息的存储元件。它具有两个稳定状态,即0和1,并且能够在没有输入信号的情况下保持其输出状态不变。锁存器的输出状态只有在输入信号改变时才会改变。

1.2 锁存器的类型

锁存器主要分为以下两种类型:

- SR锁存器(Set-Reset Latch) :最基本的锁存器类型,具有两个输入端,分别称为Set(置位)和Reset(复位)。当Set端为高电平,Reset端为低电平时,锁存器的输出为1;当Reset端为高电平,Set端为低电平时,输出为0。

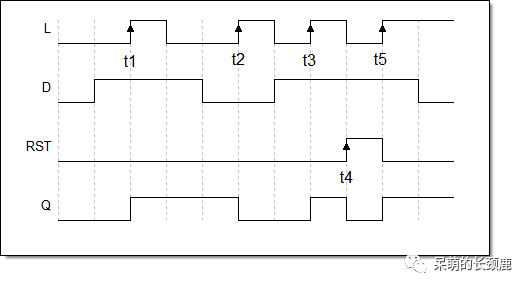

- D锁存器(Data Latch) :也称为数据锁存器,其输出直接由输入端D决定。当控制信号(如时钟信号)有效时,D锁存器的输出将与输入端D同步。

1.3 锁存器的工作原理

锁存器的工作原理主要依赖于其内部的逻辑电路。以SR锁存器为例,其内部通常包含两个交叉耦合的反相器和两个与门。当Set端为高电平时,与门1的输出为高电平,经过反相器1后,输出端Q为低电平,反相器2的输出为高电平,与门2的输出为低电平,这样Q端的输出就被“锁定”在低电平状态。同样,当Reset端为高电平时,Q端的输出会被“锁定”在高电平状态。

1.4 锁存器的应用

锁存器在数字电路中有着广泛的应用,例如:

- 数据存储 :在计算机系统中,锁存器可以用于存储指令和数据。

- 控制信号生成 :在微处理器中,锁存器可以用于生成控制信号,以控制其他电路的运行。

- 状态保持 :在数字系统中,锁存器可以用于保持某些状态信息,直到下一个输入信号到来。

二、触发器(Flip-Flop)

2.1 触发器的定义

触发器是一种具有两个稳定状态的双稳态存储元件,其输出状态的改变依赖于特定的输入信号。与锁存器不同,触发器的输出状态改变是同步的,即在特定的时钟信号下才会发生。

2.2 触发器的类型

触发器主要分为以下两种类型:

- D触发器(Data Flip-Flop) :其输出状态与输入端D同步,当时钟信号上升沿到来时,D触发器的输出将与输入端D同步。

- JK触发器(J-K Flip-Flop) :具有两个输入端J和K,当J和K均为高电平时,输出状态翻转;当J为高电平,K为低电平时,输出状态置1;当J为低电平,K为高电平时,输出状态置0。

2.3 触发器的工作原理

触发器的工作原理主要依赖于其内部的逻辑电路和时钟信号。以D触发器为例,其内部通常包含两个D锁存器和一些额外的逻辑门。当时钟信号的上升沿到来时,D触发器的输出将与输入端D同步。JK触发器的工作原理则更为复杂,其内部通常包含四个反相器和两个与门。

2.4 触发器的应用

触发器在数字电路中也有着广泛的应用,例如:

- 数据存储 :在计算机系统中,触发器可以用于存储指令和数据。

- 时序控制 :在数字系统中,触发器可以用于生成时序控制信号,以控制其他电路的运行。

- 状态机实现 :在数字系统中,触发器可以用于实现状态机,以控制系统的状态转换。

-

存储

+关注

关注

13文章

4883浏览量

90251 -

锁存器

+关注

关注

8文章

957浏览量

45455 -

触发器

+关注

关注

14文章

2065浏览量

63536 -

低电平

+关注

关注

1文章

238浏览量

14031

发布评论请先 登录

sr锁存器和触发器的逻辑功能区别

sr锁存器和触发器的逻辑功能区别

评论