锁存器和触发器是数字电路中的基本组件,它们在实现数字逻辑功能中起着至关重要的作用。虽然它们在功能上有很多相似之处,但它们之间还是存在一些主要区别的。本文将探讨锁存器和触发器的主要区别。

1. 定义

锁存器(Latch) 是一种具有双稳态的存储单元,它可以保持一个比特的数据,直到被新的数据替换。锁存器可以视为一个简单的存储设备,它能够存储一个二进制位(0或1),并且能够在没有时钟信号的情况下保持数据稳定。

触发器(Flip-flop) 也是一种存储单元,但它通常包含两个稳定状态,可以存储一个比特的数据。与锁存器不同,触发器通常需要一个时钟信号来同步数据的存储和更新。

2. 工作原理

锁存器的工作原理:

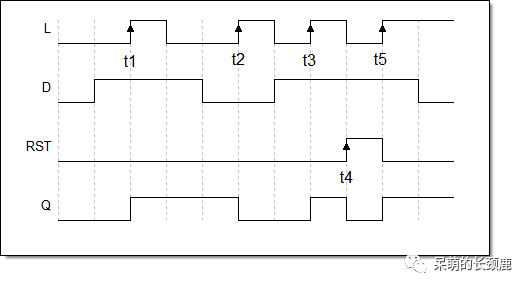

锁存器通常由两个交叉耦合的反相器或NAND门组成。当输入信号改变时,锁存器的输出会跟随输入变化,直到输入再次改变。锁存器的输出在输入信号稳定时保持不变,这使得它能够“锁定”输入信号的状态。

触发器的工作原理:

触发器的工作原理依赖于时钟信号。在时钟信号的上升沿或下降沿,触发器会捕获输入信号并将其存储在内部。触发器的输出在时钟信号的下一个边沿之前保持不变。触发器通常有多种类型,如D触发器、JK触发器、T触发器等,每种触发器的输入逻辑和输出逻辑都有所不同。

3. 触发方式

锁存器的触发方式:

锁存器的触发方式通常是边沿触发或电平触发。边沿触发锁存器在输入信号的边沿(上升沿或下降沿)时触发,而电平触发锁存器在输入信号达到特定电平时触发。

触发器的触发方式:

触发器的触发方式通常是时钟触发。触发器在时钟信号的上升沿或下降沿捕获输入信号,并在下一个时钟边沿之前保持输出稳定。

4. 应用场景

锁存器的应用场景:

锁存器通常用于数据存储和数据传输。它们可以用于实现数据寄存器、移位寄存器、计数器等。锁存器还可以用于实现简单的存储器,如只读存储器(ROM)。

触发器的应用场景:

触发器在数字电路中应用广泛,包括寄存器、计数器、移位寄存器、存储器(如随机存取存储器RAM)、状态机等。触发器的同步特性使其在时钟驱动的数字系统中尤为重要。

5. 优缺点

锁存器的优缺点:

- 优点:

- 简单易实现。

- 可以在没有时钟信号的情况下工作。

- 适合用于数据存储和传输。

- 缺点:

- 容易产生亚稳态,特别是在输入信号变化时。

- 需要额外的逻辑来控制数据的存储和更新。

触发器的优缺点:

- 优点:

- 同步特性使其在时钟驱动的数字系统中更为可靠。

- 可以减少亚稳态的发生。

- 适合用于实现复杂的数字逻辑。

- 缺点:

- 需要时钟信号,增加了系统复杂性。

- 在某些情况下,可能会引入时钟偏斜和时钟抖动。

6. 类型

锁存器的类型:

锁存器主要有SR锁存器(Set-Reset Latch)、D锁存器(Data Latch)和T锁存器(Toggle Latch)等类型。每种锁存器的输入逻辑和输出逻辑都有所不同。

触发器的类型:

触发器主要有D触发器、JK触发器、T触发器、SR触发器等类型。每种触发器的输入逻辑和输出逻辑都有所不同,适用于不同的应用场景。

7. 亚稳态

锁存器的亚稳态:

锁存器在输入信号变化时容易产生亚稳态。亚稳态是指锁存器的输出在一段时间内不确定,可能会在0和1之间振荡。这通常发生在输入信号变化时,锁存器的输出尚未稳定。

触发器的亚稳态:

触发器通过时钟信号同步输入,可以减少亚稳态的发生。然而,在某些情况下,如时钟偏斜或时钟抖动,触发器仍然可能产生亚稳态。

-

锁存器

+关注

关注

8文章

904浏览量

41441 -

数字电路

+关注

关注

193文章

1600浏览量

80490 -

触发器

+关注

关注

14文章

1995浏览量

61043 -

时钟信号

+关注

关注

4文章

445浏览量

28506

发布评论请先 登录

相关推荐

锁存器和触发器的主要区别是什么

锁存器和触发器的主要区别是什么

评论