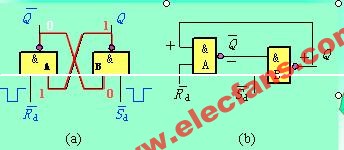

钟控RS触发器(Clock-Controlled RS Flip-Flop)是一种数字电路的基本组件,广泛应用于各种数字逻辑电路中。它是一种具有两个输入端(R和S)和两个输出端(Q和Q')的双稳态电路,可以实现对输入信号的存储和转换。

- 钟控RS触发器的工作原理

钟控RS触发器是一种双稳态电路,其工作原理基于两个输入端R和S的状态。当R=0,S=1时,触发器的输出Q为1,Q'为0,称为置位状态;当R=1,S=0时,触发器的输出Q为0,Q'为1,称为复位状态。当R和S同时为1或同时为0时,触发器的状态保持不变,称为保持状态。

钟控RS触发器的工作原理可以分为以下几个步骤:

1.1 输入信号的接收

触发器的两个输入端R和S接收外部输入信号。R端接收置位信号,S端接收复位信号。

1.2 时钟信号的控制

触发器的输出状态在时钟信号的上升沿或下降沿发生改变。时钟信号可以是外部提供的,也可以是内部生成的。

1.3 状态的转换

在时钟信号的控制下,触发器根据输入端R和S的状态进行状态转换。具体转换规则如下:

- 当R=0,S=1时,触发器置位,输出Q变为1,Q'变为0。

- 当R=1,S=0时,触发器复位,输出Q变为0,Q'变为1。

- 当R和S同时为1或同时为0时,触发器保持当前状态不变。

1.4 输出信号的生成

触发器根据内部状态生成输出信号Q和Q'。Q和Q'互为反相,即当Q为1时,Q'为0;当Q为0时,Q'为1。

- 钟控RS触发器的特性

2.1 双稳态特性

钟控RS触发器具有双稳态特性,即在没有外部输入信号的情况下,触发器可以保持当前状态不变。

2.2 同步特性

触发器的输出状态在时钟信号的控制下同步发生改变,这使得触发器在数字电路中具有很好的同步性能。

2.3 抗干扰特性

由于触发器的输出状态在时钟信号的控制下发生改变,因此具有一定的抗干扰能力。

2.4 存储特性

触发器可以存储输入信号的状态,实现对信号的存储和转换。

- 钟控RS触发器的应用

3.1 寄存器设计

钟控RS触发器可以用于设计各种寄存器,如移位寄存器、计数器等。

3.2 时序逻辑电路设计

触发器在时序逻辑电路中扮演着重要的角色,可以实现各种时序控制功能。

3.3 存储器设计

触发器可以用于设计各种存储器,如随机存取存储器(RAM)和只读存储器(ROM)。

3.4 状态机设计

触发器可以用于设计各种状态机,实现复杂的状态控制功能。

- 钟控RS触发器的设计方法

4.1 基本设计

钟控RS触发器的基本设计包括两个输入端R和S,两个输出端Q和Q',以及时钟信号输入端。设计时需要考虑触发器的逻辑功能和电路结构。

4.2 触发器类型的选择

根据应用需求,可以选择不同类型的触发器,如上升沿触发、下降沿触发、边沿触发等。

4.3 时钟信号的设计

时钟信号的设计需要考虑时钟频率、时钟相位等因素,以满足触发器的工作要求。

4.4 抗干扰设计

为了提高触发器的抗干扰能力,可以采取一些措施,如增加滤波电路、采用差分信号等。

4.5 存储特性的设计

为了实现触发器的存储特性,可以采用一些技术,如使用触发器的反馈回路、增加锁存器等。

- 结论

钟控RS触发器是一种重要的数字电路组件,具有双稳态、同步、抗干扰和存储等特性。在数字电路设计中,触发器被广泛应用于寄存器、时序逻辑电路、存储器和状态机等设计中。通过合理的设计方法,可以提高触发器的性能和可靠性,满足各种应用需求。

-

RS触发器

+关注

关注

3文章

101浏览量

18968 -

双稳态电路

+关注

关注

1文章

29浏览量

15405 -

触发器

+关注

关注

14文章

2065浏览量

63582

发布评论请先 登录

RS触发器是什么?解读rs触发器的作用和数字电路中的rs触发器的作用

钟控RS触发器状态d是什么

钟控RS触发器状态d是什么

评论