一、原理图绘制及检查流程

| 阶段 | 流程 |

| 原理图绘制 | 根据已有原理图或资料(数据手册、方案书)绘制原理图 |

| DRC检查 | EDA的DRC自检,初步找出绘制不合理部分 |

| 根据Check List自检 | 根据Check List进行原理图及PCB详检 |

二、原理图检查清单细则

| 原理图Check List | |||

| 电源电路 | 自检确认项目 | 确认结果 | 备注 |

| 应用设计 | 模拟部分数字部分是否隔离 | ||

| 每个IC的电源引脚是否都有一个去耦电容 | |||

| 去耦/储能电容是否足够大 | |||

| 电感、电阻、磁珠的额定功率、电流是否达到要求 | |||

| 电源大小的配置电阻是否设置正确(反馈引脚电阻) | |||

| 电源网络上的电容额定电压是否合适 | |||

| 需要测试的电源处是否添加测试点 | |||

| 电源输出精度是否满足要求 | |||

| 输出电流能力是否超过负载峰值20% | |||

| DC-DC设计 | 是否有防反接电路 | ||

| 输入电容耐压是否满足要求 | |||

| 电源电路是否有指示灯 | |||

| 开关电感下不允许有信号线通过 | |||

| 开关电感的饱和电流是否满足70%裕量 | |||

| 有两路及两路以上使用同一个DCDC电路,输出端和地平面是否分割 | |||

| DCDC散热是否有考虑 | |||

| 参考设计来源及与参考设计的不同之处说明 | |||

| LDO设计 | 最低压差是否满足要求 | ||

| 散热引脚是否有足够的散热铜皮 | |||

| 输入使能默认使能还是失能 | |||

| 时钟部分 | 自检确认项目 | 确认结果 | 备注 |

| 时钟电路 | 时钟及高速信号是否有正确的连接方式 | ||

| 时钟信号是否采用点到点连接 | |||

| 无源晶振设计 | 无源晶振是否有起振电阻设计(1MΩ)(也可0Ω代替,需要时更换) | ||

| 无源晶振起振电容是否满足要求 | |||

| 无源晶振的精度是否满足要求 | |||

| 复位电路 | 自检确认项目 | 确认结果 | 备注 |

| 确认主芯片复位是高电平复位还是低电平复位 | |||

| 确认主芯片复位的电平时间 | |||

| 主芯片是否为上电复位,是否有上/下拉电阻 | |||

| 原理图 | 自检确认项目 | 确认结果 | 备注 |

| 原理图是否采用0.05inch栅格 | |||

| 原理图图页规格采用A4规格,元器件过大时可使用A3规格 | |||

| 必要的部分是否有注释标注 | |||

| 每张原理图是否有文件名 | |||

| 所有元器件是否有符号和容量等标识 | |||

| 电阻、电容、电感等器件的管脚标注等不必要标识不要显示 | |||

| LED颜色标识是否显示 | |||

| 器件管脚上的引线,应引出后再分叉,不得直接在器件管脚上分叉。 | |||

| 电路是否需要上/下拉电阻 | |||

| 各个管脚的上/下拉电阻是否正确 | |||

| 提供各单点网络列表和 连接管脚列表,并一一确认 | |||

| 确认原理图中的器件与数据手册一致 | |||

| 确认器件名称及位号是否正确 | |||

| 多图页原理图是否有重新分配位号 | |||

| 总线的名称和作用是否有标识 | |||

| 网络标识的标注是否正确 | |||

| 是否已经标识出需要阻抗匹配的电路 | |||

| GND及电源测试点是否标识 | |||

| 确认DRC检查的每个错误及警告是否已经修改正确 | |||

| 最新的原理图生成的网表必须保证已经导入PCB | |||

| 可以邀请其他成员一起检查原理图设计 | |||

| PCB Check List | |||

| 规则设置 | 自检确认项目 | 确认结果 | 备注 |

| 安全距离设置是否正确 | |||

| 是否正确设置物理和电气规则(注意电源网络和地网络的约束设置) | |||

| Test Via、Test Pin的间距设置是否足够 | |||

| 叠层的厚度和方案是否满足设计和加工要求 | |||

| 所有有特性阻抗要求的差分线阻抗是否已经经过计算,并用规则控制 | |||

| 确认DRC已经调整到最少,对于不能消除DRC要一一确认 | |||

| 器件检查 | 自检确认项目 | 确认结果 | 备注 |

| 确认所有器件封装是否与公司统一库一致,是否已更新封装库 | |||

| 元器件是否100% 放置 | |||

| 较重的元器件,应该布放在靠近PCB支撑点或支撑边的地方,以减少PCB的翘曲 | |||

| 接口相关的器件尽量靠近接口放置 | |||

| 发热量大的器件是否需要加装散热片,距离是否足够 | |||

| 金属壳体的元器件,特别注意不要与其它元器件相碰,要留有足够的空间位置 | |||

| 与结构相关的器件布好局后是否锁住以防止误操作移动位置 | |||

| 在PCB上轴向插装较高的元件,应该考虑卧式安装 | |||

| 功能检查 | 自检确认项目 | 确认结果 | 备注 |

| 数模混合板的数字电路和模拟电路器件布局时是否已经分开,信号流是否合理 | |||

| A/D转换器跨模数分区放置 | |||

| 时钟器件布局是否合理 | |||

| 高速信号器件布局是否合理 | |||

| IC器件的去耦电容数量及位置是否合理 | |||

| 信号线以不同电平的平面作为参考平面,当跨越平面分割区域时,参考平面间的连接电容是否靠近信号的走线区域 | |||

| 保护电路的布局是否合理,是否利于分割 | |||

| 电源电路 | 自检确认项目 | 确认结果 | 备注 |

| 是否IC电源距离IC过远 | |||

| LDO及周围电路布局是否合理 | |||

| 模块电源等周围电路布局是否合理 | |||

| 电源的整体布局是否合理 | |||

| 丝印检查 | 自检确认项目 | 确认结果 | 备注 |

| 器件位号是否遗漏,位置是否能正确标识器件 | |||

| 器件位号是否符合公司标准要求 | |||

| 确认器件的管脚排列顺序、第1脚标志、器件的极性标志、连接器的方向标识的正确性 | |||

| 确认设计要求的丝印添加是否正确 | |||

| 确认PCB编码正确且符合公司规范 | |||

| 确认单板的PCB编码位置和层面正确 | |||

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

原理图

+关注

关注

1303文章

6363浏览量

235436 -

pcb

+关注

关注

4328文章

23182浏览量

400389 -

Checklist

+关注

关注

0文章

7浏览量

3265

发布评论请先 登录

相关推荐

HK32F030MF4P6最小系统板原理图及PCB文件

方便验证 HK32F030MF4P6 性能的最小系统板原理图和PCB文件,所有IO都有引出,适合需要验证单片机性能但不想要画板的小伙伴。原理图:PCB 预览:注意:因为IO口都是直接引

发表于 12-23 18:00

•0次下载

如何导入Altium Designer的原理图和PCB?

“ KiCad可以支持直接导入Altium Designer的原理图及PCB文件。与其它导入器不同,KiCad导入器可以直接导入源生的二进制文件(*.schdoc及*.pcbdoc),而不需要像

TPS65950/30/20 32KHz振荡器原理图和PCB布局指南

电子发烧友网站提供《TPS65950/30/20 32KHz振荡器原理图和PCB布局指南.pdf》资料免费下载

发表于 10-29 09:58

•1次下载

AD(Altium Desinger) PCB排版时,选中原理图元件直接对应跳转到PCB对应元件

方法如下:①首先分屏显示原理图和PCB②然后原理图选中多个元件,或者自己选择想要集体排布的电子元件。在原理图里按快捷键T+S后,它会自己跳转至PCB

发表于 09-19 16:39

ad怎么实现原理图与pcb元件对应

在Altium Designer(AD)中,实现原理图(Schematic)与PCB(Printed Circuit Board)元件对应的过程是一个关键的设计步骤,它确保了电路设计的准确性和一致性

AD20原理图跟PCB怎么交互

在Altium Designer 20(简称AD20)中,原理图和PCB之间的交互是设计流程中的一个重要环节,它允许设计师在逻辑设计和物理实现之间自由切换,确保设计的准确性和一致性。以下是AD20

ad怎么把原理图和pcb相关联

在Altium Designer(简称AD)中,将原理图和PCB相关联是一个重要的设计步骤,它确保了从逻辑设计到物理实现的顺利过渡。以下是实现原理图和PCB相关联的步骤: 一、分配元件

AD画完原理图后如何导入PCB

在Altium Designer(简称AD)中,将画完的原理图导入到PCB(Printed Circuit Board,印制电路板)是一个关键的设计步骤。以下是导入过程: 一、准备阶段 确保原理图

altium怎么把原理图导入pcb

在Altium Designer中,将原理图导入到PCB设计是一个关键的步骤,它确保了电路设计的准确性和可制造性。这个过程涉及到多个阶段,包括原理图的创建、编译、检查以及最终的导入到PCB

Altium怎么把原理图换成pcb

在Altium Designer中,将原理图转换为PCB(Printed Circuit Board,印制电路板)图是一个关键的设计步骤。以下是将原理图换成

FS201资料(pcb & DEMO & 原理图)

电子发烧友网站提供《FS201资料(pcb & DEMO & 原理图).zip》资料免费下载

发表于 07-16 11:24

•2次下载

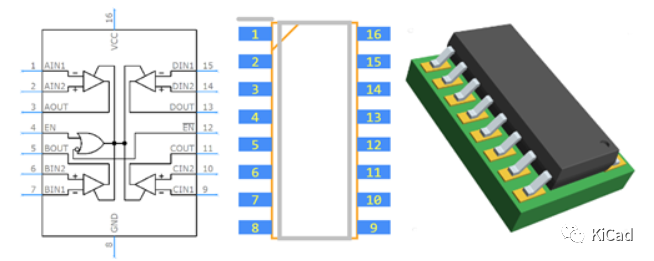

干货!原理图设计规范133条checklist

原理图设计是产品设计的理论基础,设计一份规范的原理图对设计PCB、跟机、做客户资料具有指导性意义,是做好一款产品的基础。原理图设计基本要求: 规范、清晰、准确、易读。因此制定《

发表于 04-01 15:50

原理图及PCB Checklist大放送~

原理图及PCB Checklist大放送~

评论