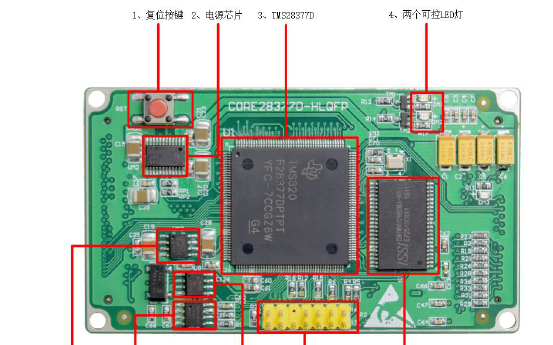

CPM核心板,#ZLG首款百元内64位1G主频工业级核心板,BGA封装集成处理器与DDR,不含数据存储器件。本文将从电路设计和PCB布线角度,指导用户如何通过eMMC扩展存储,以快速完成设计。

eMMC原理图设计

eMMC原理图设计

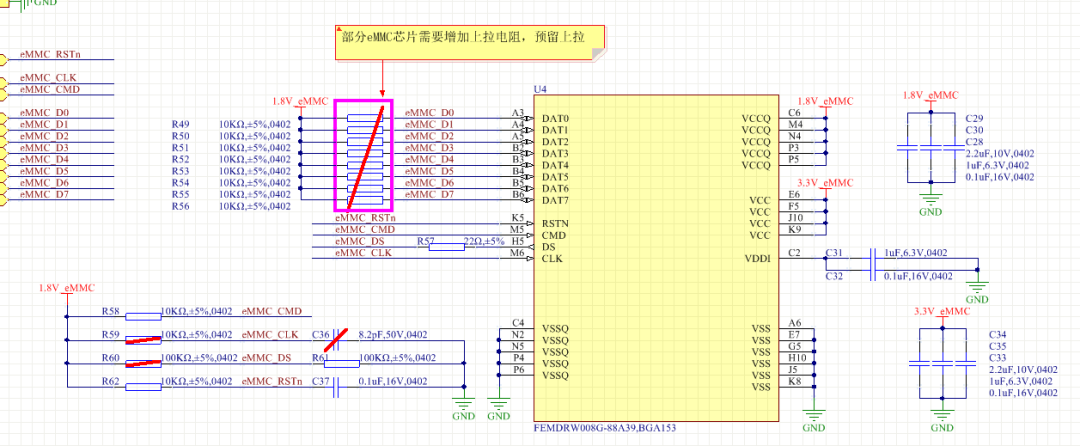

eMMC扩展电路原理图设计包括电容、上拉电阻、串联电阻等方面。图1是设计完成的电路图。

图1 eMMC扩展电路原理图下面对电路设计进行一些说明:

- RSTN通过10K电阻上拉至VccQ并需并联一个0.1uF对地电容,可提高抗干扰能力。

- eMMC_CMD外接10K电阻上拉至VccQ,eMMC_D[7:0]预留10K电阻上拉至VccQ,因CMD和Data传输起始位是以低电平开始所以CMD和Data需要默认上拉,实际使用阻值可参考手册。

- eMMC_Data_Stobe 在eMMC端串电阻,阻值建议为22~33Ω之间,并预留47K下拉电阻,因eMMC协议规定先采上升沿信号再采下降沿信号,所以DS需要默认下拉。

- eMMC_CLK 在MCU端串电阻,阻值建议为22~33Ω之间,为实现阻抗匹配,减少信号反射,实际以调试为准。

- VDDi引脚需要外接一个电容,以稳定Core电压,一般建议为1uF~ 4.7uF,实际使用容值可参考手册。

- VCC、VCCQ电源电路的滤波,采用大小电容并联的方式,大电容应该大于2.2uF,小电容可以在0.1uF左右,实际使用容值可参考手册。

底板eMMCPCB布线说明

底板eMMCPCB布线说明

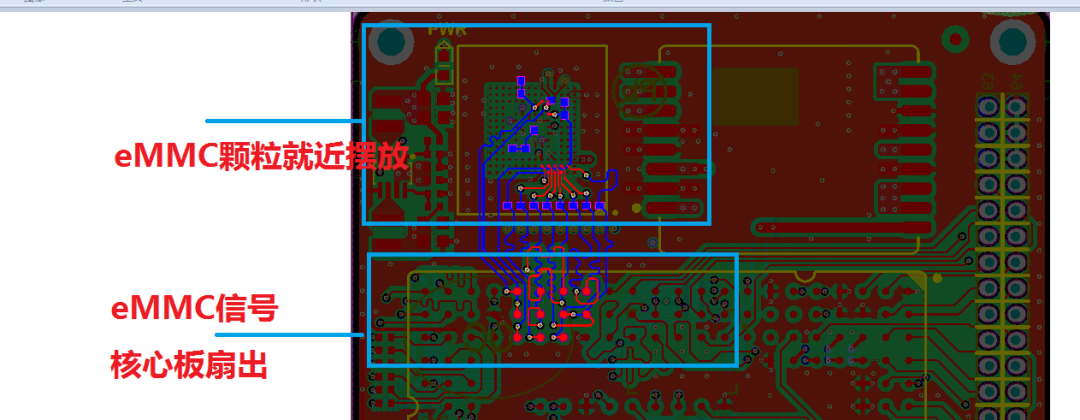

eMMC布线好坏直接影响eMMC能否使用以及eMMC的读写性能,相比原理图设计,eMMC的布线会更加重要。下面对PCB布线细节进行一些说明。

图2 PCB布线图

- 在CPM核心板扇出的eMMC信号引脚周围就近布局eMMC。

- eMMC的数据信号、时钟信号和控制信号需要做阻抗50Ω±10%匹配管控。

- 时钟、数据、命令信号需要做等长,误差小于50mil且走线总长不要超过3000mil(误差和等长需加上核心板的约束数据),走线越短越好,以便减少信号线上的寄生电容等参数,使信号线上总的寄生电容少于30pF。

- CLK和RST_N长度差在1000mil以内。

- 时钟信号需要包地处理,地线每隔200mil打一个地过孔。

- eMMC信号间的间距至少2W ,eMMC 信号与其它信号间间距建议3W至少2W,以便减少不必要的串扰信号。

- eMMC个电源管脚的滤波电容靠近对应的管脚放置,尽量保证一个管脚放一个。

- eMMC所有信号少换层打孔,过孔数量尽量不要超过两个,eMMC 信号换层前后,参考层建议都为地平面,在信号过孔周围建议添加地回流过孔,以改善信号回流路径,所有信号线参考平面必须完整不能跨分割。

- 内部走不出来的信号可以从NC PAD走,不能从RFU PAD上走线。

已验证的eMMC型号

已验证的eMMC型号

ZLG首款百元内64位1G主频工业级核心板

ZLG首款百元内64位1G主频工业级核心板

ZLG致远电子创新推出超小型CPM核心板,采用 BGA 封装形式,集成处理器、DDR内存及NorFlash,并配备外置电源模块。用户可依根据产品需求灵活搭配不同容量的EMMC存储器,实现定制化配置。CPM核心板继承了易开发、高稳定性的传统优势,并在灵活性与性价比上取得新突破,为用户带来更多元化的应用体验。

-

硬件设计

+关注

关注

18文章

394浏览量

44525 -

CPM

+关注

关注

0文章

12浏览量

7692 -

emmc

+关注

关注

7文章

200浏览量

52593 -

核心板

+关注

关注

5文章

985浏览量

29698

发布评论请先 登录

相关推荐

智明力强IMX6核心板参数

Cyclone V Soc 核心板

FPGA+ARM cyclone 核心板

什么是核心板?核心板有何优势

什么是嵌入式核心板

【资料分享】全志科技T507工业核心板硬件说明书(一)

HDSP-D377DQC2核心板硬件使用说明书的详细资料免费下载

高频核心板设计的技巧有哪些

MT6762_MT6765核心板硬件手册

什么是嵌入式核心板、一体板?米尔核心板有什么优势?

CPM核心板应用之电源硬件设计指导

CPM核心板应用之量产贴装指导

CPM核心板应用之eMMC硬件设计指导

CPM核心板应用之eMMC硬件设计指导

评论