在数字时代,DRAM(动态随机存取存储器)扮演着至关重要的角色。它们存储着我们的数据,也承载着我们的记忆。然而,要正确地操作DRAM并确保其高效运行,了解其背后的时序和操作机制是必不可少的。

1. DRAM操作的挑战

DRAM的操作复杂性主要来自于其时序要求。DRAM是一种异步系统。只要信号以正确的顺序应用,并且信号持续时间和信号之间的延迟满足特定限制,DRAM就能正常工作。控制DRAM操作的主要信号包括:

行地址选通(RAS):RAS信号是低电平有效。要启用RAS,需要从高电压过渡到低电压,并且电压必须保持低电平直到RAS不再需要。在完整的内存周期中,RAS必须保持有效状态的最小时间是tRAS。此外,RAS在再次激活之前必须保持非活动状态的最小时间是tRP。

列地址选通(CAS):CAS用于锁定列地址并启动读或写操作。CAS也是低电平有效。内存规格列出了CAS必须保持活动状态的最小时间tCAS。对于大多数内存操作,CAS在再次激活之前也必须保持非活动状态的最小时间tCP。

写使能(WE):写使能信号用于选择读操作或写操作。WE信号是低电平有效。

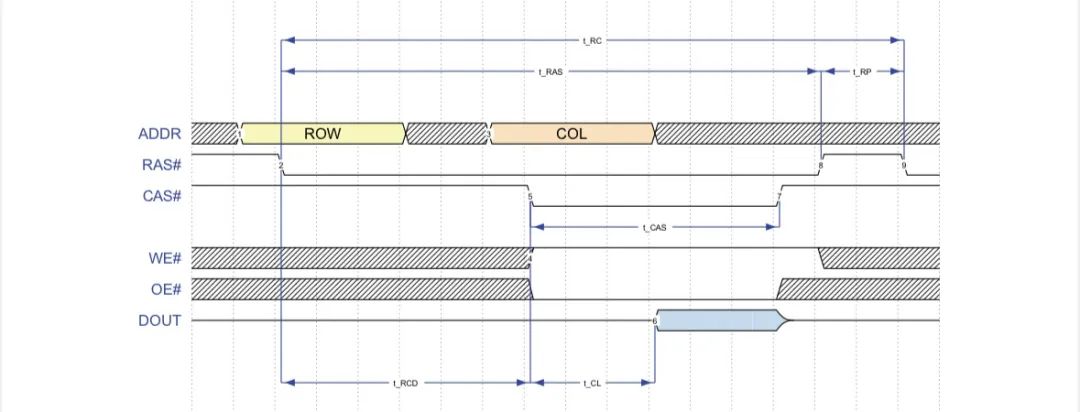

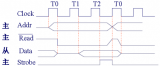

2. 读操作

读取DRAM中的数据时,需要通过地址输入引脚提供行和列地址来选择特定的DRAM存储单元。选中的DRAM单元上的电荷随后由灵敏放大器检测,并发送到数据输出引脚。

读操作的时序步骤如下:

在RAS信号变低之前,行地址必须应用于内存设备的地址输入引脚。

RAS信号从高变低,并保持低电平一段时间(tRAS)。当RAS变低时,由行地址指定的内存行被打开,选中行的单元电荷开始流向位线。

在CAS信号变低之前,列地址必须应用于内存设备的地址输入引脚。

在CAS信号转换之前,WE信号必须设置为高电平以进行读操作,并在CAS转换后保持高电平。

经过规定的RAS到CAS延迟时间(tRCD)后,CAS信号从高变低,并保持低电平一段时间(tCAS)。这确保了选中单元的电荷在位线上,并被灵敏放大器正确检测。

数据出现在内存设备的数据输出引脚上,这个过程称为CAS延迟(tCL)。

读周期完成前,CAS和RAS必须返回到非活动状态。新的读或写访问只能在规定的行预充电时间(tRP)后开始。

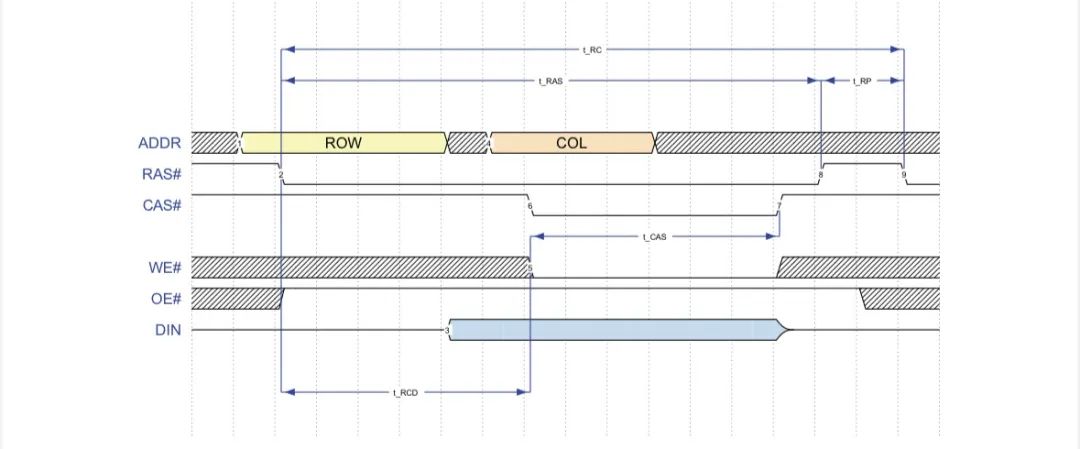

3. 写操作

写入DRAM存储单元时,同样需要选择行和列地址,并将数据呈现在数据输入引脚上。灵敏放大器根据要存储的是1还是0,对存储单元的电容器进行充电或放电。

写操作的时序步骤如下:

在RAS信号变低之前,行地址必须应用于内存设备的地址输入引脚。

RAS信号从高变低,并保持低电平一段时间(tRAS)。当RAS变低时,由行地址指定的内存行被打开。

数据在CAS信号变低之前必须应用于数据输入引脚。

在RAS信号变低后和CAS信号变低之前,列地址必须应用于内存设备的地址输入引脚。

为了进行写操作,WE信号必须设置为低电平。

经过规定的RAS到CAS延迟时间(tRCD)后,CAS信号从高变低,并保持低电平一段时间(tCAS)。

4. 刷新操作

由于DRAM存储单元是电容器,其电荷会随时间逐渐流失。如果电荷丢失,数据也会丢失。为了防止数据丢失,必须定期刷新DRAM,即恢复每个存储单元上的电荷。DRAM的刷新是逐行进行的,刷新频率取决于制造内存芯片的工艺和存储单元的设计。大多数现代DRAM每64毫秒需要刷新一次。

刷新DRAM时,通常使用所谓的CAS-before-RAS刷新序列。这个过程包括以下步骤:

CAS信号从高变低,同时WE信号保持高电平(相当于读操作)。

经过规定延迟后,RAS信号从高变低。

内部计数器确定要刷新的行,并在地址引脚上应用行地址。

通过这些步骤,DRAM能够保持其数据的完整性,确保我们的信息安全存储。

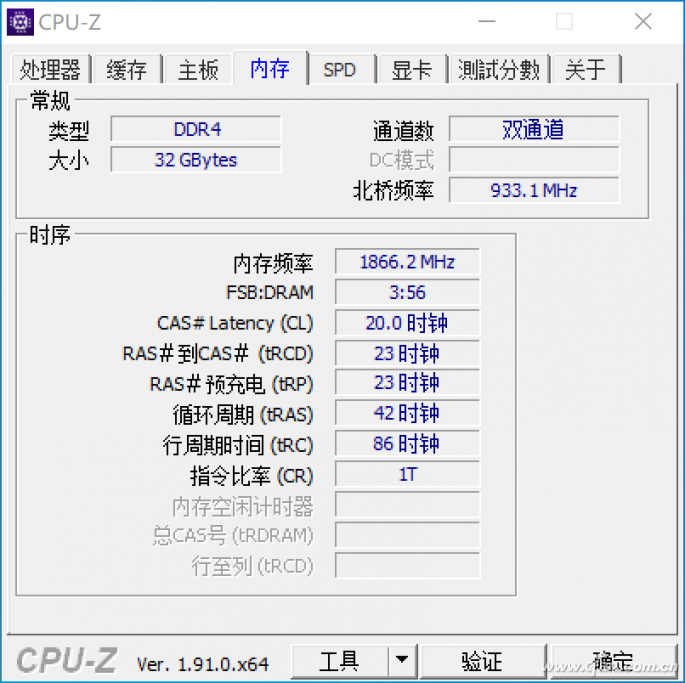

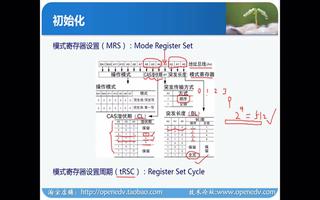

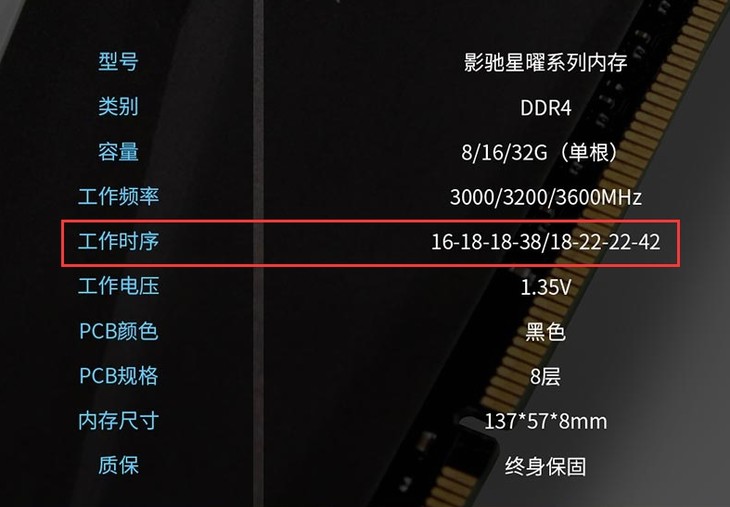

5. 重要时序参数总结

行激活时间(tRAS):RAS信号需要保持低电平的最小时间,以读取或写入存储位置。

CAS延迟(tCL):从正确列已打开的DRAM读取第一个比特所需的时间。

行地址到列地址延迟(tRCD):激活RAS到激活CAS所需的最短时间。

随机访问时间(tRAC):从没有激活行的DRAM读取第一个比特所需的时间。

行预充电时间(tRP):数据检索成功后,需要关闭用于访问数据的行。

行周期时间(tRC):与单次读或写周期相关的时间,tRC = tRAS + tRP。

-

DRAM

+关注

关注

40文章

2309浏览量

183418 -

存储器

+关注

关注

38文章

7481浏览量

163751 -

时序

+关注

关注

5文章

387浏览量

37308

原文标题:DRAM内存操作与时序解析

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

内存中隐藏的内存时序的意义分析

DRAM内存原理

【内存知识】DRAM芯片工作原理

DRAM内存模块的设计技术

内存速度和时序重要么

正点原子开拓者FPGA:SDRAM时序操作

DRAM内存操作与时序解析

DRAM内存操作与时序解析

评论