JK触发器概述

JK触发器,也被称为通用可编程触发器,是数字电路中的一种基本存储器件。它得名于其输入端口J(置位)和K(复位),以及一个时钟控制端。JK触发器能够模拟其他多种类型触发器的行为,具有置0、置1、翻转和保持四种功能,是集成触发器中功能最为齐全的触发器之一。由于其强大的通用性和灵活性,JK触发器被广泛应用于时序电路、频率分析电路、数码集成电路等多种数字电路中,特别是在计算机的寄存器中用于存储二进制信息。

JK触发器的工作原理

1. 基本组成与功能

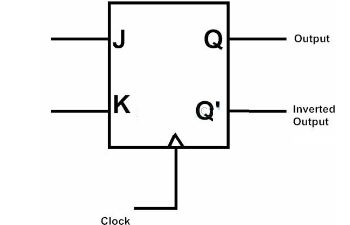

JK触发器由两个输入端口(J和K)、一个时钟控制端(CP)以及两个输出端(Q和Q')组成。其中,Q是JK触发器的主输出,Q'是Q的补码输出。JK触发器的功能由J、K输入和时钟信号CP共同决定。

2. 触发条件

JK触发器是边沿触发触发器,这意味着它仅在时钟信号的上升沿或下降沿(具体取决于触发器类型)到来时触发状态转移。在时钟信号的非触发边沿期间,JK触发器的输出状态保持不变。

3. 功能模式

JK触发器根据J、K输入的不同组合,可以工作在以下四种功能模式下:

- 保持模式 :当J和K输入均为低电平时(J=0, K=0),JK触发器将保持其先前的状态不变,即Q和Q'的输出将维持原样。

- 复位模式 :当J为低电平而K为高电平时(J=0, K=1),JK触发器将进入复位状态,此时Q输出为0,Q'输出为1。

- 置位模式 :当J为高电平而K为低电平时(J=1, K=0),JK触发器将进入置位状态,此时Q输出为1,Q'输出为0。

- 翻转模式 :当J和K输入均为高电平时(J=1, K=1),JK触发器将进入翻转状态,即其输出将取反先前的状态。如果先前Q=0,则翻转后Q=1;如果先前Q=1,则翻转后Q=0。

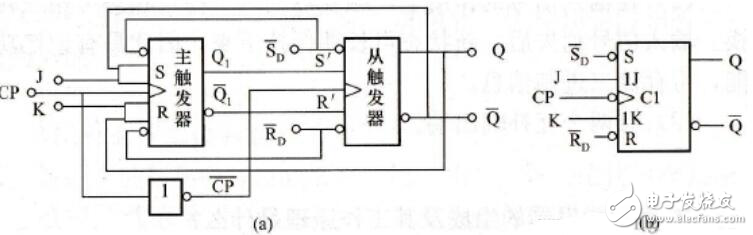

4. 内部结构与逻辑实现

JK触发器的内部结构通常可以用NAND门(与非门)锁存器来解释。与非门是一种逻辑门,其输出是其输入的逻辑与的补码。JK触发器由两个与非门构成,形成一个正反馈回路。输入J和K连接到第一个与非门的输入,而第一个与非门的输出连接到第二个与非门的输入。第二个与非门的输出再连接到第一个与非门的输入,形成反馈回路。这种结构使得JK触发器具有记忆功能,能够在时钟信号的作用下保持或改变其输出状态。

5. 时钟信号的作用

时钟信号是JK触发器工作的关键。当时钟信号CP的上升沿或下降沿到来时(具体取决于触发器类型),JK触发器将根据J、K输入的值来决定是否改变其输出状态。在时钟信号的非触发边沿期间,JK触发器的输出状态保持不变。

6. 触发器类型

JK触发器主要分为边沿型和主从型两种:

- 边沿型JK触发器 :在时钟信号的上升沿或下降沿触发状态转移。这种触发器具有较快的响应速度和较高的抗干扰能力。

- 主从型JK触发器 :由主触发器和从触发器两个部分组成。主触发器在时钟信号的上升沿接收输入信号并改变其状态,而从触发器则在时钟信号的下降沿将主触发器的状态传输到输出端。这种触发器能够避免在输入信号变化时产生的竞争冒险现象。

总结

JK触发器作为数字电路中的一种重要存储器件,具有置0、置1、翻转和保持四种功能。它根据J、K输入和时钟信号CP的共同作用来决定其输出状态的变化。JK触发器的内部结构通常用NAND门锁存器来解释,形成一个正反馈回路以实现记忆功能。在数字电路中,JK触发器被广泛应用于时序电路、频率分析电路、数码集成电路等多种场合,特别是在计算机的寄存器中用于存储二进制信息。通过合理设计JK触发器的类型和参数,可以实现复杂的逻辑功能和时序控制要求。

-

JK触发器

+关注

关注

1文章

43浏览量

15906 -

数字电路

+关注

关注

193文章

1605浏览量

80617 -

触发器

+关注

关注

14文章

2000浏览量

61148

发布评论请先 登录

相关推荐

jk触发器是什么原理_jk触发器特性表和状态转换图

JK触发器概述及工作原理

JK触发器概述及工作原理

评论