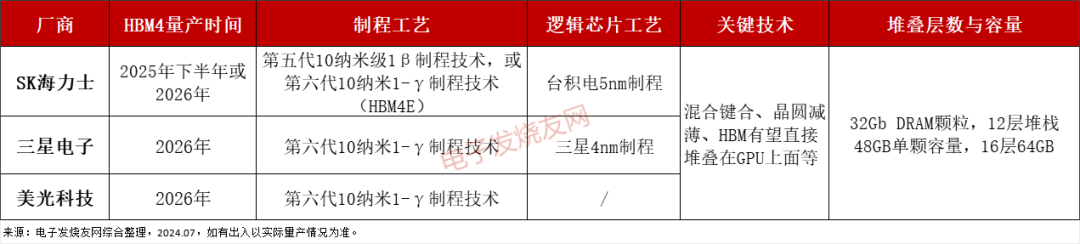

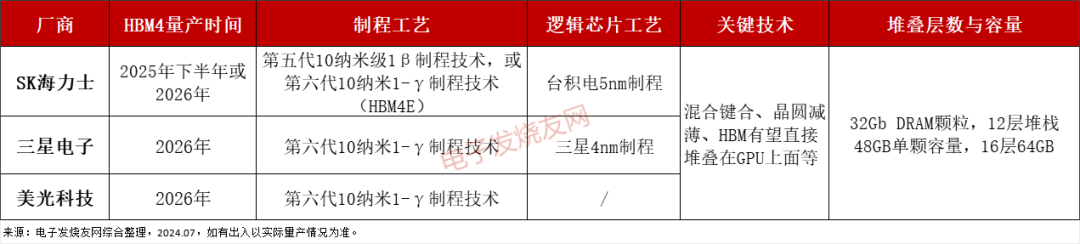

电子发烧友网报道(文/黄晶晶)眼下各家存储芯片厂商的HBM3E陆续量产,HBM4正在紧锣密鼓地研发,从规格标准到工艺制程、封装技术等都有所进展,原本SK海力士计划2026年量产HBM4,不过最近有消息说提前到2025年。其他两家三星电子和美光科技的HBM4的量产时间在2026年。英伟达、AMD等处理器大厂都规划了HBM4与自家GPU结合的产品,HBM4将成为未来AI、HPC、数据中心等高性能应用至关重要的芯片。

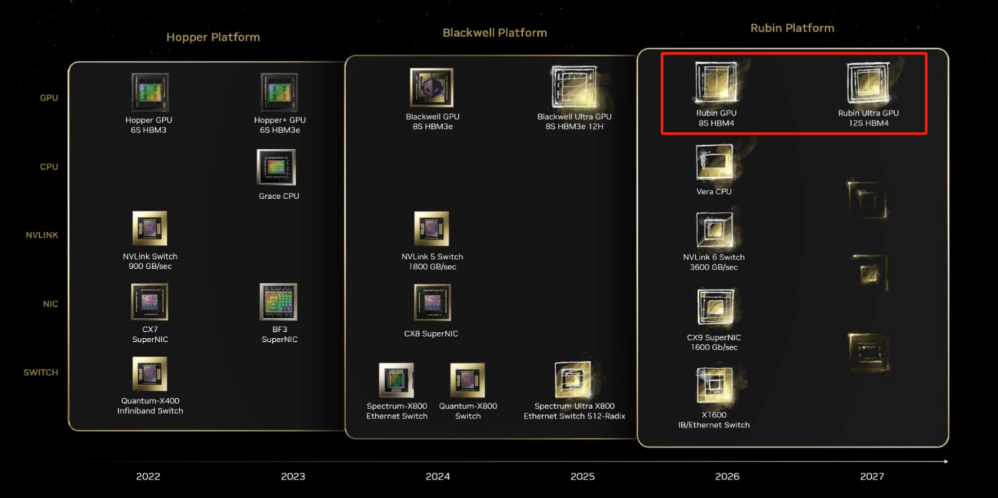

结合正在制定的行业标准以及厂商信息,我们大致可以看到HBM4的一些特性。首先HBM4的接口将采用2048位,比HBM3E的1024位高出一倍。HBM4的带宽在2TB/s或以上,HBM3E的带宽最高可达1.2TB/s。另外,SK海力士技术人员Kim Kwi Wook表示,HBM4E内存可较HBM4在带宽上提升40%、密度提升30%,同时能效也提高30%。堆叠层数和容量上,HBM4采用32Gb DRAM颗粒,12层堆叠达到48GB容量,高至16层可达到64GB,HBM3E采用24Gb DRAM颗粒,8层堆叠为24GB容量,最高12层,36GB容量。今年6月,NVIDIA 宣布下一代Rubin GPU将配备8个HBM4,Rubin Ultra GPU将配备12个HBM4芯片,其总内存容量将显著提升。

结合正在制定的行业标准以及厂商信息,我们大致可以看到HBM4的一些特性。首先HBM4的接口将采用2048位,比HBM3E的1024位高出一倍。HBM4的带宽在2TB/s或以上,HBM3E的带宽最高可达1.2TB/s。另外,SK海力士技术人员Kim Kwi Wook表示,HBM4E内存可较HBM4在带宽上提升40%、密度提升30%,同时能效也提高30%。堆叠层数和容量上,HBM4采用32Gb DRAM颗粒,12层堆叠达到48GB容量,高至16层可达到64GB,HBM3E采用24Gb DRAM颗粒,8层堆叠为24GB容量,最高12层,36GB容量。今年6月,NVIDIA 宣布下一代Rubin GPU将配备8个HBM4,Rubin Ultra GPU将配备12个HBM4芯片,其总内存容量将显著提升。

行业标准制定中

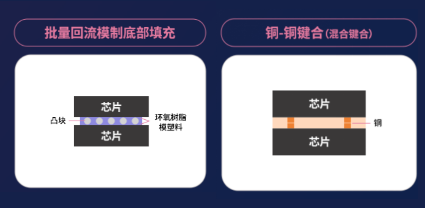

近日,JEDEC固态技术协会发布的新闻稿表示,HBM4标准即将定稿,进一步提高数据处理速率,具有更高带宽、更低功耗以及增加裸晶/堆栈的容量。这些进步对于需要高效处理大型数据集和复杂计算的应用至关重要,包括生成式人工智能(AI)、高性能计算、高端显卡和服务器。 与HBM3相比,HBM4在每个堆栈中引入了两倍的通道计数,具有更大的物理尺寸。为了支持设备兼容性,标准确保单个控制器可以同时处理HBM3和 HBM4。HBM4将指定24 Gb和32 Gb层,并提供支持4层、8层、12层和16层TSV堆栈的选项。该委员会初步同意最高6.4 Gbps的速度,并正在讨论更高频率的问题。 另外,韩媒报道还指出,JEDEC有望放宽对HBM4内存的高度限制。目前,HBM内存的最大DRAM堆叠层数为12层,允许的最大厚度为720微米。三星最近HBM3E 12H产品通过对NCF材料的优化,芯片之间的间隙已降低至7微米。若HBM4内存提升到16层,再加上凸块厚度,传统技术无法实现在720微米厚度下的16层堆叠。于是,据称JEDEC主要参与方已同意放宽HBM4高度限制至775微米。这样也可以为混合键合HBM内存的商业化留出更多时间。 下图左边为SK海力士从HBM3开始采用的先进大规模回流成型底部填充 (MR-MUF) 工艺,右边为Cu-to-Cu(Copper-to-Copper, 铜-铜)键合封装工艺,是一种混合键合方法,可在完全不使用凸块的情况下将间距缩小至10微米及以下。混合键合技术可以进一步缩小间距,同时作为一种无间隙键合(Gapless Bonding)技术,在芯片堆叠时不使用焊接凸块(Solder Bump),因此在封装高度上更具优势,是目前各家存储芯片厂商重点开发的技术。

图源:SK海力士

HBM4制程工艺与性能

HBM的制程工艺方面,SK海力士在HBM3E内存上使用第五代10纳米级1β制程技术,在2024年度IEEE IMW国际存储研讨会上,SK海力士表示计划使用第六代10纳米级的1-γ制程技术的32Gb DRAM裸片构建HBM4E内存。至于HBM4内存,分析认为由于SK海力士将在2025年量产HBM4,比其他两家要早,那时可能还是采用的第五代10纳米级1β制程技术。另外,三星电子、美光科技也纷纷将使用第六代10纳米级的1-γ制程技术用于HBM4内存。

图源:英伟达 (注:右上角红框为配备8个HBM4的Rubin GPU,以及配备12个HBM4芯片的Rubin Ultra GPU)

逻辑芯片、3D堆叠封装工艺更新

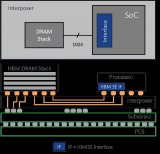

三星电子最近介绍了HBM与定制逻辑芯片进行3D堆叠的方案,是将HBM直接安装在系统芯片上,可省去中间件和基板,大幅减少功耗和面积。SK海力士也在考虑HBM4直接堆叠在GPU上的方案。这是除HBM堆叠在GPU芯片旁这种较成熟的方案之外的另一个可能性。 对于逻辑芯片,它是DRAM 堆栈的控制单元,也负责通过互连层与处理器上的内存接口通信,也是 HBM 内存的重要组成部分。由于HBM4的逻辑芯片需要支持更多的信号引脚、更大的数据带宽和承载部分客户定制功能,因此存储厂商开始选择与逻辑晶圆厂合作,用逻辑半导体工艺生产HBM4的逻辑芯片。 目前的消息显示三星将采用自家的4nm制程生产,该制程的良率已经超过70%。三星已经将晶圆代工部门员工派往HBM开发团队,通过内存部门和代工部门的紧密合作,从逻辑裸晶的设计阶段寻求优化,以最大限度地提高HBM4芯片的性能和功耗水平。 SK海力士则在今年4月与台积电签署谅解备忘录,合作生产HBM4。SK海力士表示,以往的HBM产品,包括HBM3E(第五代HBM产品)都是基于公司自身制程工艺制造了基础裸片(也就是逻辑芯片),但从HBM4产品开始计划采用台积电的先进逻辑(Logic)工艺。若在基础裸片采用超细微工艺可以增加更多的功能。由此,公司计划生产在性能和功效等方面更广的满足客户需求的定制化(Customized)HBM产品。 与此同时,双方将协力优化SK海力士的HBM产品和台积电的CoWoS技术融合,共同应对HBM相关客户的要求。 台积电在2024年的技术研讨会上展示了两款HBM4基础裸片,分别是N12FFC+和N5制程技术,其中N5版相较于N12FFC+版面积更小,性能更高,功耗更低,支持6~9μm级别的互联间距,并能实现与逻辑处理器的3D垂直集成,有望大幅提升HPC和AI芯片的内存带宽。那么SK海力士HBM4的逻辑芯片极有可能采用台积电的5nm制程工艺。 同时,韩媒消息称,SK海力士已向全球第二大封测厂Amkor协商供应硅中介层样品。SK海力士将自己生产的HBM和硅中介层等发送给Amkor,由Amko将把它们与英伟达等客户的GPU组装成AI加速器。 混合键合仍面临良率不佳的问题,因此SK海力士技术人员Kim Kwi Wook表示HBM4产品中采用混合键合的可能性不大。不过,为了降低晶圆堆叠的厚度,毕竟现在HBM芯片标准厚度为720um,如果要堆叠更多晶圆,晶圆减薄、铜-铜键合封装等都是关键技术。小结:

AI热度当前,英伟达、AMD等厂商对HBM的需求不减,HBM迭代频率在加快。随着行业标准的正式定稿,以及存储厂商HBM4新规格的发布,我们将进入HBM4的世代。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

存储

+关注

关注

13文章

4316浏览量

85861 -

HBM

+关注

关注

0文章

380浏览量

14763 -

HBM3E

+关注

关注

0文章

78浏览量

266

发布评论请先 登录

相关推荐

风景独好?12层HBM3E量产,16层HBM3E在研,产业链涌动

海力士宣布公司已开始量产12H HBM3E芯片,实现了现有HBM产品中最大的36GB容量。该产品堆叠12颗3GB DRAM芯片,实现与现有的8层产品相同的厚度,同时容量提升50%。运行

美光发布HBM4与HBM4E项目新进展

近日,据报道,全球知名半导体公司美光科技发布了其HBM4(High Bandwidth Memory 4,第四代高带宽内存)和HBM4E项目的最新研发进展。 据悉,美光科技的下一

特斯拉也在抢购HBM 4

据报道,特斯拉已要求三星和SK海力士提供HBM4芯片样品。这两家半导体公司都在为特斯拉开发第六代高带宽内存芯片原型。据KEDGlobal报道,特斯拉已要求三星和SK海力士供应通用的HBM4芯片。预计

SK海力士推出48GB 16层HBM3E产品

的领先地位,更为未来的高性能计算市场带来了全新的可能性。 SK海力士CEO郭鲁正(Kwak Noh-Jung)表示,尽管业界普遍认为16层HBM市场将从HBM4时代开始兴起,但SK海力

三星电子加速推进HBM4研发,预计明年底量产

三星电子在半导体技术的创新之路上再迈坚实一步,据业界消息透露,该公司计划于今年年底正式启动第6代高带宽存储器(HBM4)的流片工作。这一举措标志着三星电子正紧锣密鼓地为明年年底实现12层HBM4产品的

三星HBM3e芯片量产在即,营收贡献将飙升

三星电子公司近日宣布了一项重要计划,即今年将全面启动其第五代高带宽存储器(HBM)芯片HBM3e的量产工作,并预期这一先进产品将显著提升公司的营收贡献。据三星电子透露,随着

SK海力士:HBM3E量产时间缩短50%,达到大约80%范围的目标良率

据报道,SK海力士宣布第五代高带宽存储(HBM)—HBM3E的良率已接近80%。

三星电子组建HBM4团队,旨在缩短开发周期,提升竞争力

据此,现有的DRAM设计团队将主要负责HBM3E内存的开发和优化,而今年三月份新设立的HBM产能与质量提升团队则专攻下一代技术——HBM4。

三星电子组建HBM4独立团队,力争夺回HBM市场领导地位

具体而言,现有的DRAM设计团队将负责HBM3E内存的进一步研发,而三月份新成立的HBM产能质量提升团队则专注于开发下一代HBM内存——HBM4

SK海力士与台积电共同研发HBM4,预计2026年投产

自 HBM3E(第五代 HBM 产品)起,SK海力士的 HBM 产品基础裸片均采用自家工艺生产;然而,从 HMB4(

三星电子HBM存储技术进展:12层HBM3E芯片,2TB/s带宽HBM4即将上市

据业内透露,三星在HBM3E芯片研发方面遥遥领先其他公司,有能力在2024年9月实现对英伟达的替代,这意味着它将成为英伟达12层HBM3E的垄断供应商。然而,三星方面不愿透露具体客户信息。

什么是HBM3E内存?Rambus HBM3E/3内存控制器内核

Rambus HBM3E/3 内存控制器内核针对高带宽和低延迟进行了优化,以紧凑的外形和高能效的封装为人工智能训练提供了最大的性能和灵活性。

发表于 03-20 14:12

•2556次阅读

美光量产行业领先的HBM3E解决方案,加速人工智能发展

2024 年 3 月 4 日全球内存与存储解决方案领先供应商 Micron Technology, Inc.(美光科技股份有限公司,纳斯达克股票代码:MU)近日宣布已开始量产其 HBM3E

三星电子成功发布其首款12层堆叠HBM3E DRAM—HBM3E 12H

2024年2月27日 - 三星电子今日宣布,公司成功发布其首款12层堆叠HBM3E DRAM——HBM3E 12H,这是三星目前为止容量最大的HBM产品。

美光科技批量生产HBM3E,推动人工智能发展

美光执行副总裁兼首席商务官萨达纳(Sumit Sadana)称,公司已实现HBM3E的市场首发和卓越性能,同时能耗具有显著优势,使公司在AI加速领域稳占先机。他还强调,美光拥有业界顶尖的HBM3E及HBM4路线图,DRAM与NA

HBM3E量产后,第六代HBM4要来了!

HBM3E量产后,第六代HBM4要来了!

评论