Part 01

前言

作为一名硬件工程师,从接触单片机的那天,就看到MCU的旁边经常看到会用到晶振,经常的旁边往往会放两个电容,有时候还会再放个电阻,很多硬件工程师都是看别的工程师放多大的电容,电阻,自己也跟着放,这样也没错,但是知其然不知其所以然,对你的硬件水平提高是没有任何帮助的,今天我们就讲一下晶振电路,以及晶振外围阻容器件的选型计算,下一篇文章会讲晶振和MCU是否匹配已经晶振常见问题处理。

Part 02

晶振电路

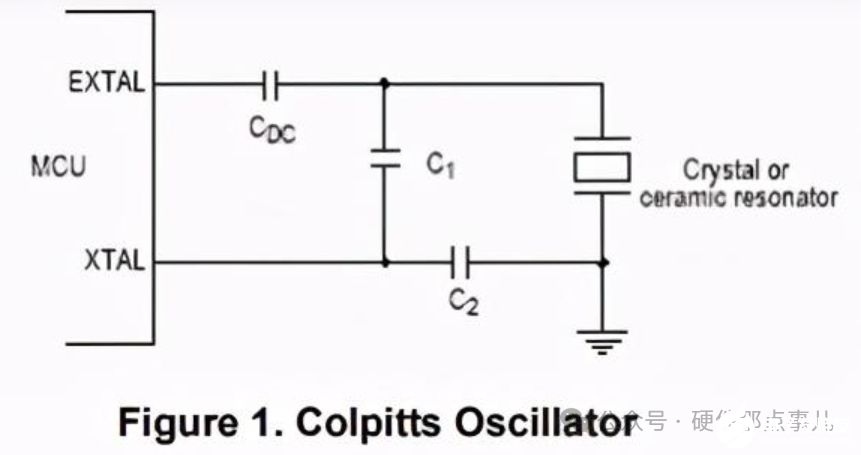

晶振电路有两种,一种是Pierce电路,另外一种是Colpitts电路,其实就是两种晶振拓扑,比较常用的是Pierce电路。所以我们大概介绍一下Colpitts电路的特点就跳过了,采用Colpitts电路的晶振的缺点是晶振两端会有杂散电抗,此时比较难考虑杂散电抗的影响,说白了就是计算起来比较麻烦,电路可靠性也更低,还会在晶振两端形成DC偏置电压,优点是电路有振幅限制,从而功耗更低,对外部电路辐射干扰更小。

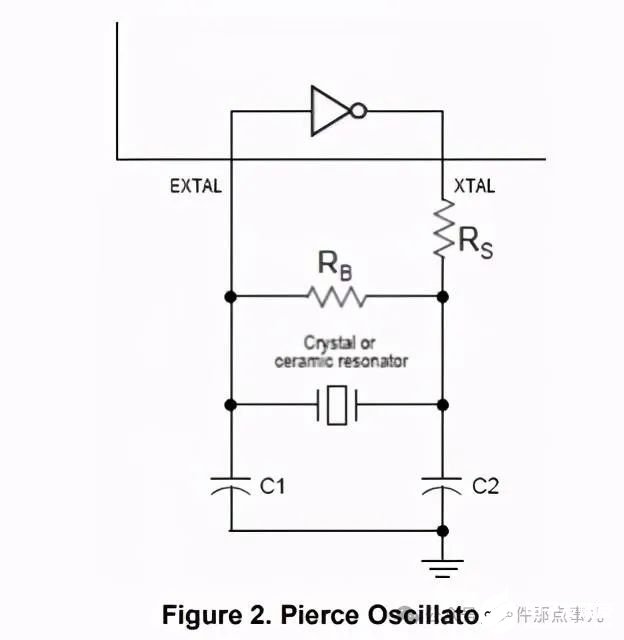

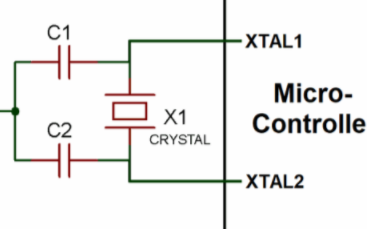

我们重点要介绍的是Pierce电路,具体电路就是下图这种形式,也是最常见的拓扑图,该电路一般由非门电路(增益特别大的运放),反馈电阻,负载电容构成,电容和晶振是外置的,一般要自己选型,运放和反馈电阻一般集成在IC内部,启动速度更快,可靠性更高,所以说除非有很严苛的功耗要求,一般推荐使用此电路。

1)Rs是限流电阻,Rs的值越小,晶振启动速度越快,为了避免晶振过驱动,Rs也不能过小,在高频晶振中,Rs可以短路。

2)Rb是反馈电阻,为运放输入提供反馈,让运放工作在线性区,当运放工作在线性区时,晶振才能正常起振,当然反馈电阻Rb也会影响运放的环路增益,反馈电阻越大,增益越大。

Part 03

阻容元件计算

1)负载电容计算

Cl=(C1*C2) / (C1+C2)+Cs+Cp

Cs就是晶振内部的杂散电容,晶振规格书中一般会标出该值,Cp就是PCB板上的走线以及晶振引脚的寄生电容,Cs和Cp的电容加起来总计2-8pF,最准确的方法是通过测试晶振输出波形来确认负载电容是否合适。负载电容越大,晶振频率越低。C1越大,反馈越弱,越不利于晶振起振,晶振就无法稳定工作,当然了反馈过强,会导致晶振过驱动,也会有问题。

大家需要注意的是负载电容一定要选用NP0或C0G电容才可以,温度稳定性更高,这样频率才会更稳定。

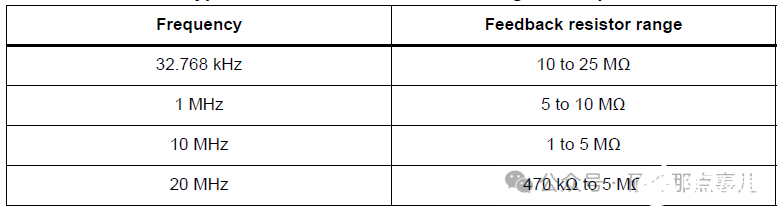

2)反馈电阻计算

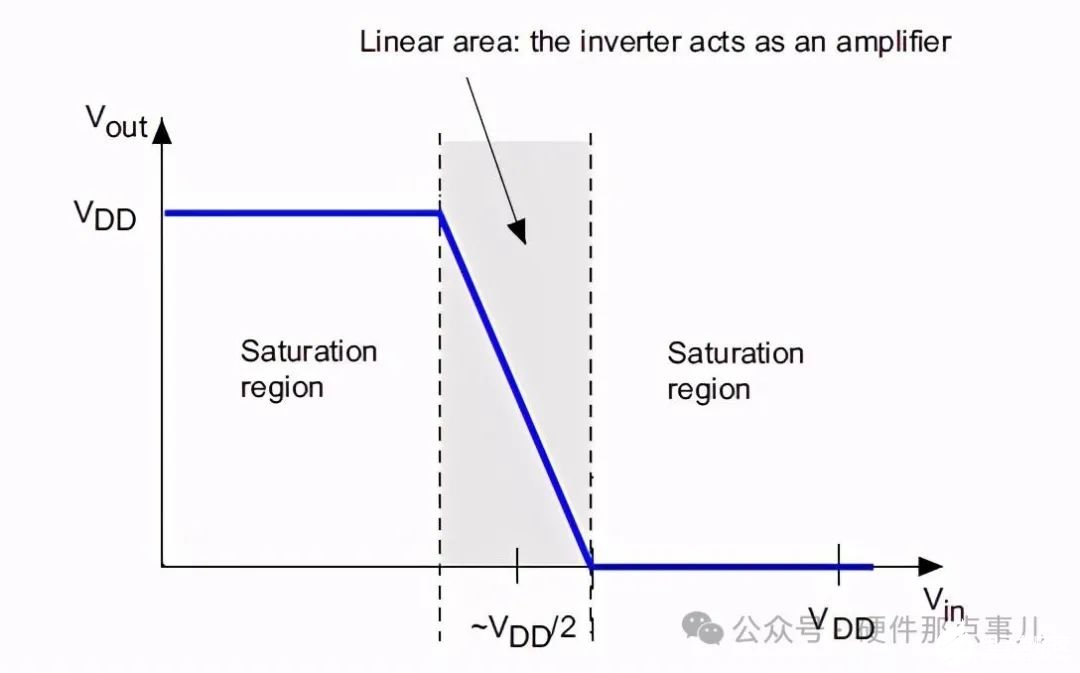

反馈电阻的作用是让晶振电路的反相器工作在线性区,也就是下图的阴影区时,这时候电路没有饱和,属于负反馈放大电路,才会稳定持续工作,反馈电阻的作用就在这里,那么反馈电阻怎么计算呢?我查阅了很多文档,都没有给出计算公式,但是找到了一份配置表,大家可以参考。

今天我们就讲到这里了,下一篇文章会讲一下晶振电路和MCU的兼容性计算,这点非常重要,因为晶振电路到底行不行还要看你选的MCU是否认可,那么怎么通过计算确认呢?敬请关注。

▼硬件那点事儿▼

-

mcu

+关注

关注

146文章

16975浏览量

350205 -

晶振

+关注

关注

33文章

2818浏览量

67887 -

系统电路

+关注

关注

0文章

4浏览量

6724 -

晶振电路

+关注

关注

7文章

92浏览量

25267

发布评论请先 登录

相关推荐

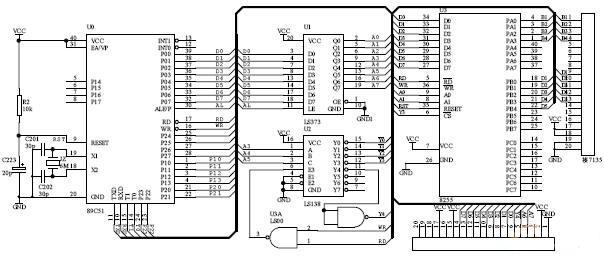

最小系统电路图

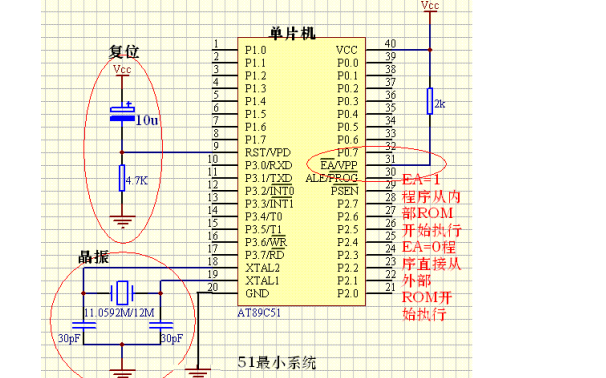

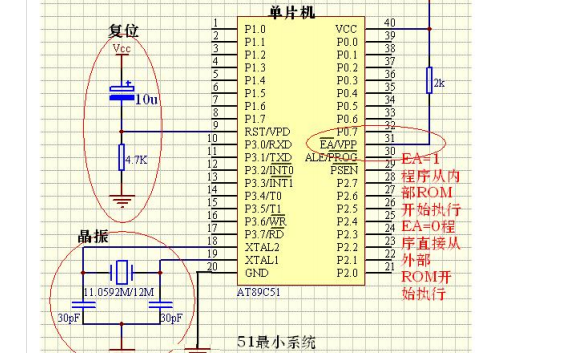

51单片机的最小系统电路图和复位电路的详细资料说明

51单片机最小系统是什么?51单片机最小系统的电路介绍

MCU最小系统电路中的晶振电路如何选型计算呢?1100字搞定它!

MCU最小系统电路中的晶振电路如何选型计算呢?1100字搞定它!

评论