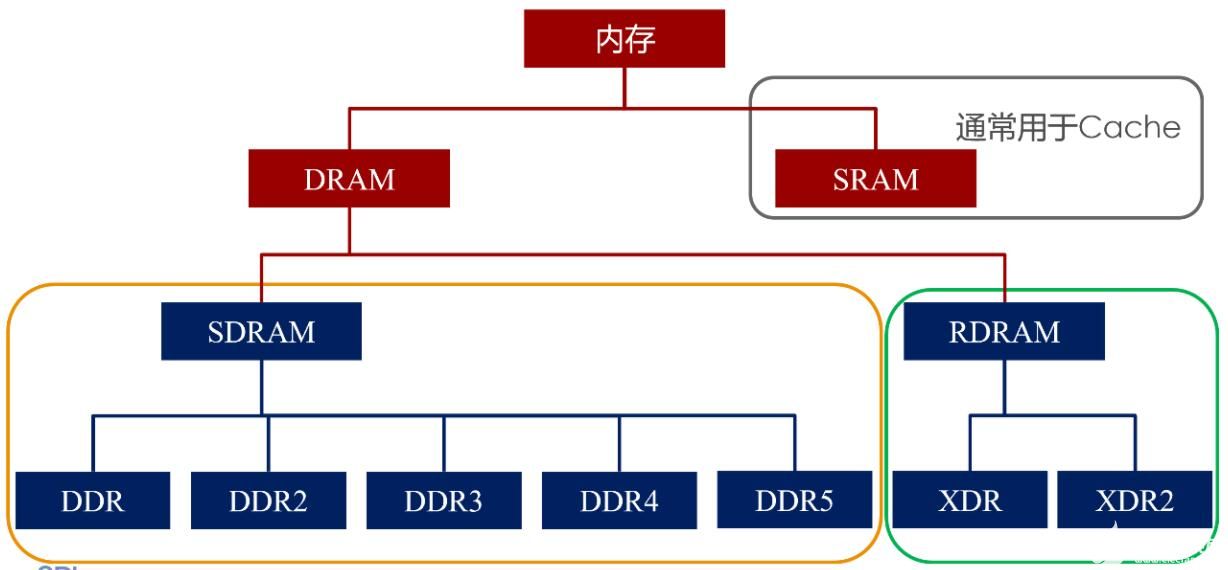

DRAM从20世纪70年代初到90年代初生产,接口都是异步的,其中输入控制信号直接影响内部功能。

同步DRAM(SDRAM)设备比DRAM设备有显著的改进。在两个方面与前几代DRAM设备不同:

1.增加了时钟信号;因此,SDRAM具有同步接口,也就是说是命令而不是信号在控制存储单元。

2.SDRAM包含多个独立bank。

3.SDRAM支持burst突发模式传输。

SDRAM有一个时钟信号,所有内部动作都发生在其边沿。

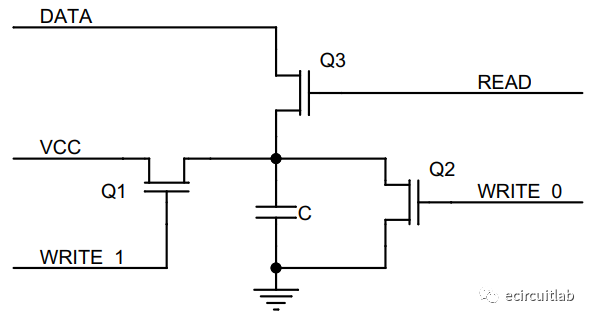

在DRAM中,来自内存控制器的RAS、CAS和WE信号直接控制内部latch和输入/输出buffer,这些信号可以随时到达DRAM的引脚。然后,DRAM立即响应RAS、CAS和WE信号。

相反,在SDRAM中,RAS、CAS和WE信号不能直接控制内部latch 和buffer。在SDRAM中,这些信号形成一个命令总线,用于将命令传输到内部状态机,该状态机在时钟信号的边沿执行命令。通过这种方式,内部latch和输入/输出buffer的控制从外部内存控制器移动到SDRAM控制逻辑中的状态机。

每个SDRAM中存在多个独立bank,这意味着当一个bank忙于行激活命令或预充电命令时,内存控制器可以向不同的bank发送新命令。现在可以在单个SDRAM中将内存请求交错到不同的bank。SDRAM包含2、4或8个独立bank。BA0、BA1和BA2决定了命令指的是哪个bank。

功能描述

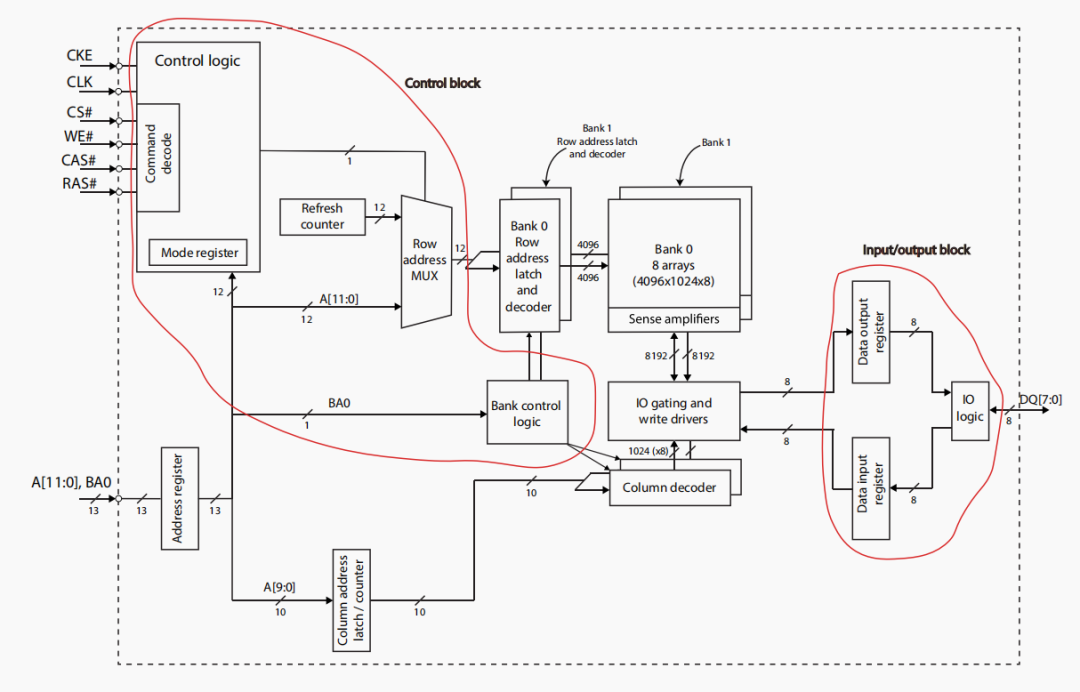

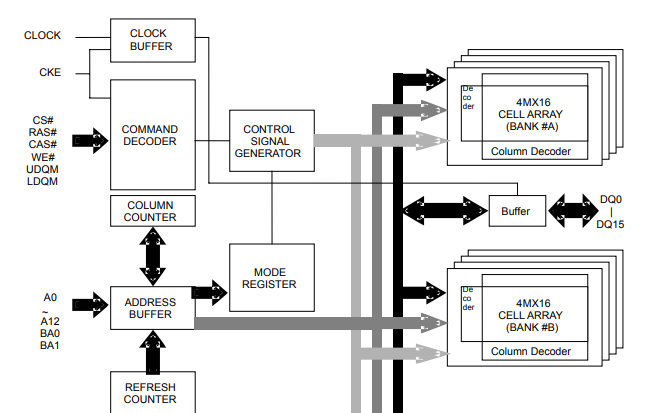

下图显示了具有两个独立bank的SDRAM的简化框图。

每个bank都有其行地址latch和解码器、列解码器和灵敏放大器。图中SDRAM中的每个bank由8个大小为4096x1024位的DRAM阵列组成。该地址现在由bank号码(BA)、行地址(A[11:0])和列地址(A[9:0])组成。

在SDRAM中,命令在时钟信号(CLK)的上升边沿解码,如果芯片选择信号(CS)处于有效状态。该命令由外部内存控制器在命令总线上发起。命令总线由WE、CAS和RAS信号组成。所有这些信号都是低有效。

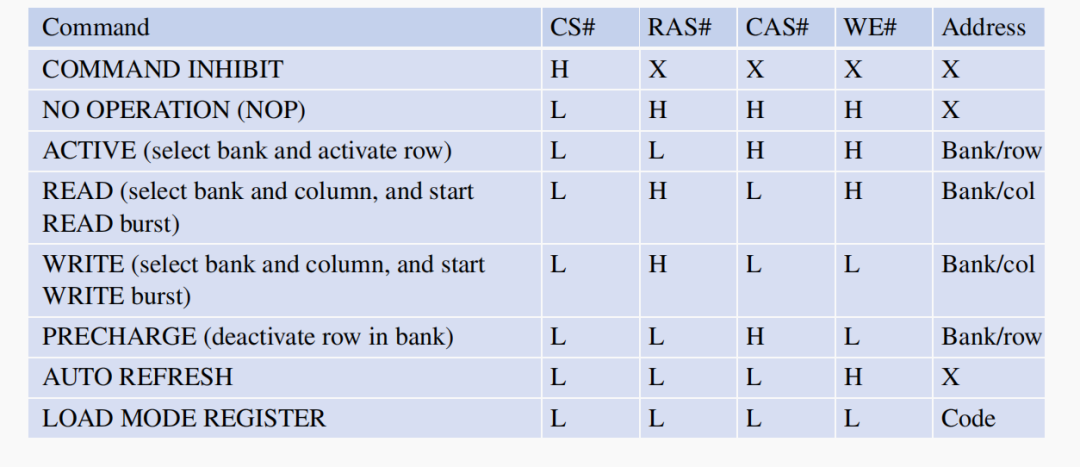

下表显示了SDRAM的命令集合。只要CS不处于有效状态,SDRAM就会忽略命令总线上的信号。

图中框出来的SDRAM控制模块由控制逻辑、选择行地址的多路复用器、刷新计数器和存储体控制逻辑组成。其中刷新计数器跟踪要刷新的行,多路复用器用于选择要传送到行地址锁存器和解码器的行地址。地址可以是来自刷新计数器的地址(用来控制逻辑执行刷新周期),也可以是来自DRAM控制器的外部地址总线上的地址。

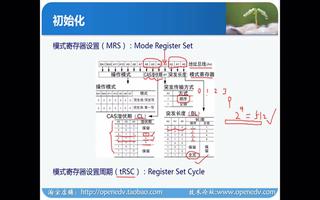

控制逻辑包含命令解码器、执行命令的有限状态机和模式寄存器。模式寄存器是一个可编程的10位寄存器,其决定:

·CAS延迟(CL)

·burst传输的长度

·以及内存数据在burst传输中的顺序。等等

控制逻辑从命令总线接收命令,然后根据命令类型和模式寄存器相应字段中的值执行特定的操作序列。这些操作由内部状态机在连续的时钟周期上执行,而不需要来自memory控制器的时钟控制。

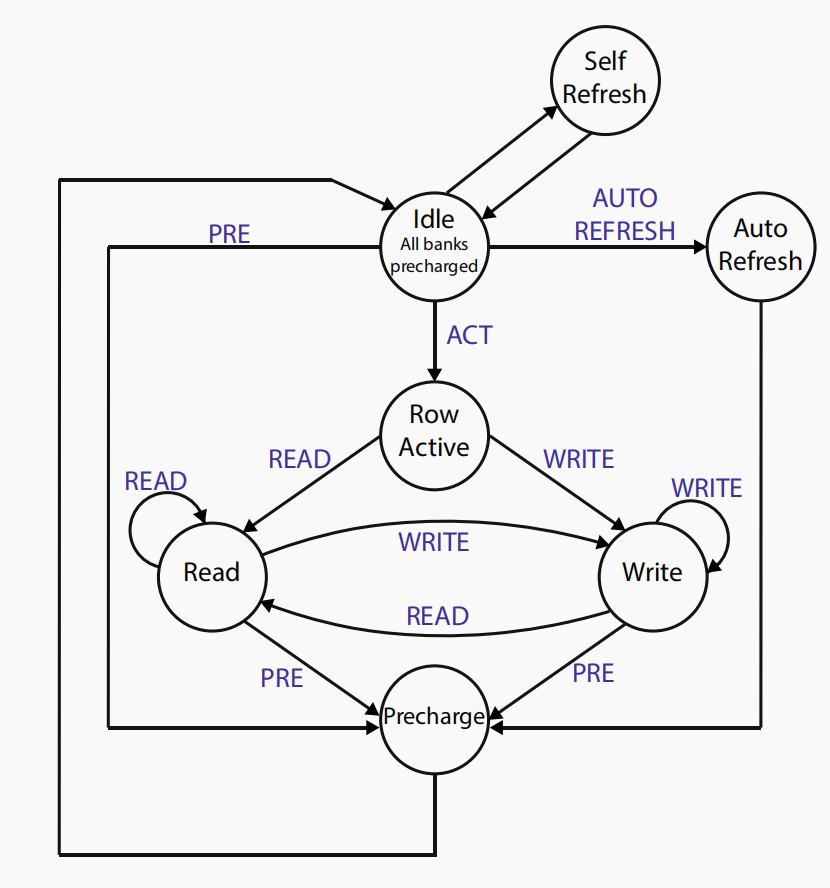

上图显示了内部状态机的简化状态图。在初始化模式寄存器后,内部状态机处于idle状态,所有行和列均预充电。如果没有向SDRAM发出命令,SDRAM芯片将定期执行自刷新操作。内部计数器驱动自刷新操作。

开始内存访问时,内存控制器应首先发出ACTIVE命令。这将打开某些bank/行,内部状态机在active状态下等待其他命令。

要读取数据,内存控制器应发出READ命令,要将数据写入内存,内存控制器应发出WRITE命令。然后内部状态机进入读或写状态,并使用列地址生成适当的内部信号来访问列。

READ或WRITE命令后面可以跟任意数量的READ或WRITE命令,或者可以发出PRECHARGE命令来恢复数据并关闭打开的bank/行。

在执行预充电操作后,内部状态机将恢复到IDLE状态。

例如,在 ACTIVE 命令的情况下,状态机通过多路复用器将行地址传递到行地址锁存器和译码器。地址位BA确定要访问的行,然后打开选定的行,并将其内容传输到灵敏放大器。

当存储器控制器发起读取命令时,内部状态机驱动行控制逻辑,根据 BA 位选择适当的列,然后从所选行的灵敏放大器中选择数据。

每个bank都有自己的列解码器-当从更多bank进行交错传输时,就特别有用,可以隐藏RAS到CAS延迟和行预充电时间。当第一次发送指定新bank的地址时,必须打开该行。 但是当后续的访问指定已经打开的bank中的同一行时,访问可以很快发生,只发送列地址,而无需等待 tRCD。此功能要求每个bank都有自己的行地址锁存器、灵敏放大器和列解码器。

-

DRAM

+关注

关注

40文章

2325浏览量

183841 -

SDRAM

+关注

关注

7文章

430浏览量

55346 -

内存控制器

+关注

关注

0文章

40浏览量

8928

原文标题:同步DRAM(SDRAM)介绍

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SDRAM的介绍及设计应用

DRAM,SRAM,SDRAM的关系与区别

EEPROM、EPROM、FLASH、SRAM、DRAM、SDRAM的区别.

求大佬详细介绍一下DRAM、SDRAM及DDR SDRAM的概念

从DRAM到广泛使用的SDRAM

有关arm裸机SDRAM的相关知识介绍

DRAM SRAM SDRAM内存精华问题汇总

DRAM、SDRAM及DDR SDRAM之间的概念详解

正点原子开拓者FPGA视频:SDRAM简介

正点原子开拓者FPGA:SDRAM时序操作

EM63A165 SDRAM高速CMOS同步DRAM的数据手册免费下载

SDRAM与DDR之间的主要差异是什么

同步DRAM(SDRAM)介绍

同步DRAM(SDRAM)介绍

评论