对于从事芯片行业的人员来说,还是有必要了解数字电路中的一些基本概念,例如用作逻辑开关的 MOS 晶体管。当然,我们的目的是了解现代芯片中的行为本质,而不需要陷入半导体物理方程。

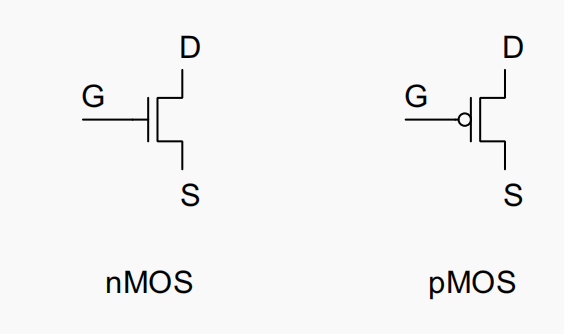

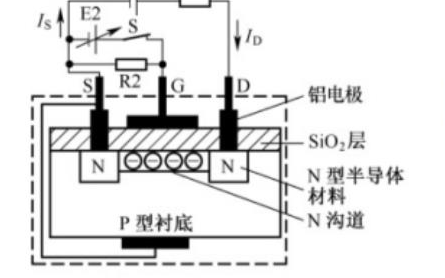

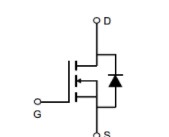

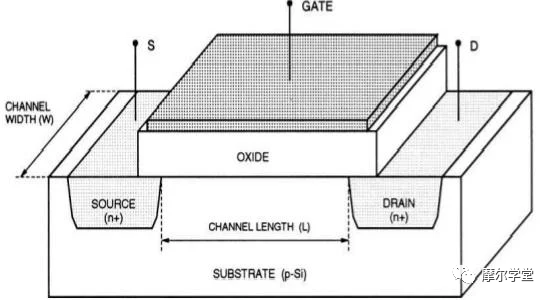

所有数字电路的基本组件是MOS晶体管。MOS是Metal-Oxid-Semiconductor金属氧化物体的首字母缩写,表示制造晶体管所用的制造工艺。有三个端口:栅极 (G)、漏极 (D) 和源极 (S)。

栅极是一个控制输入:它控制源极和漏极之间的电流流动。MOS晶体管有两种类型:nMOS和pMOS。上图显示了两个MOS晶体管的符号。

MOS晶体管作为开关

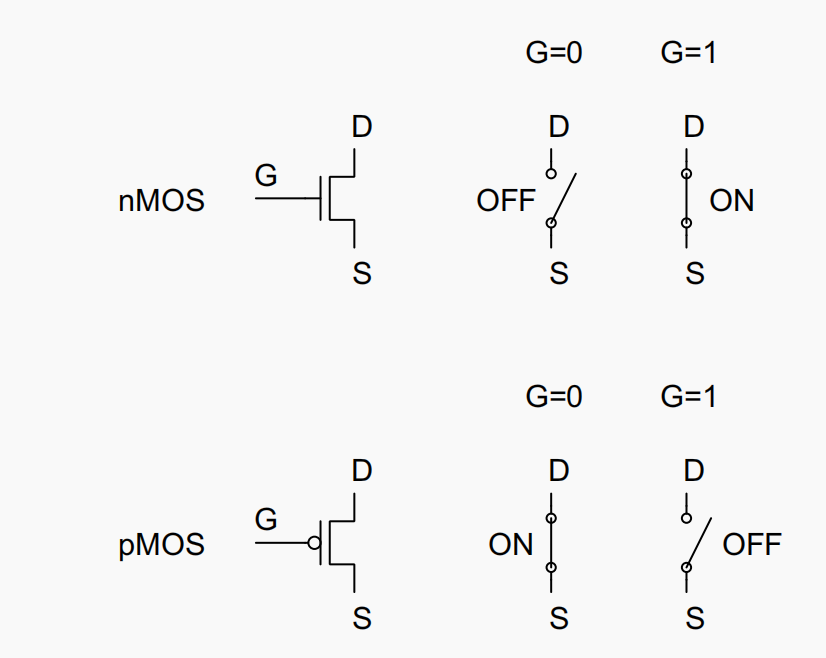

首先考虑nmos晶体管。如果栅极接地 (逻辑0),则漏极和源极之间没有电流流动。因此,我们说晶体管是关的,对应于逻辑0。如果栅电压高,则从源极到漏极电流可以流动。我们说晶体管是开着的,对应于逻辑1。

PMOS晶体管正好相反。当栅极处于与逻辑1相对应的正电压时没有电流流,晶体管处于OFF状态。与逻辑0相对应的足够低的栅电压则会形成从源极到漏极的导通路径,因此晶体管处于ON状态。

总之,MOS晶体管的栅极控制源极和漏极之间的电流流动,使我们可以将MOS晶体管视为ON/OFF开关。

当nMOS晶体管的栅极为1时,晶体管是接通的,电流在源极和漏极之间流动。当栅极为0时,nMOS晶体管关闭,源极和漏极之间没有电流流动。pMOS晶体管正好相反,当栅极电压为低时接通,当栅极高时关断。

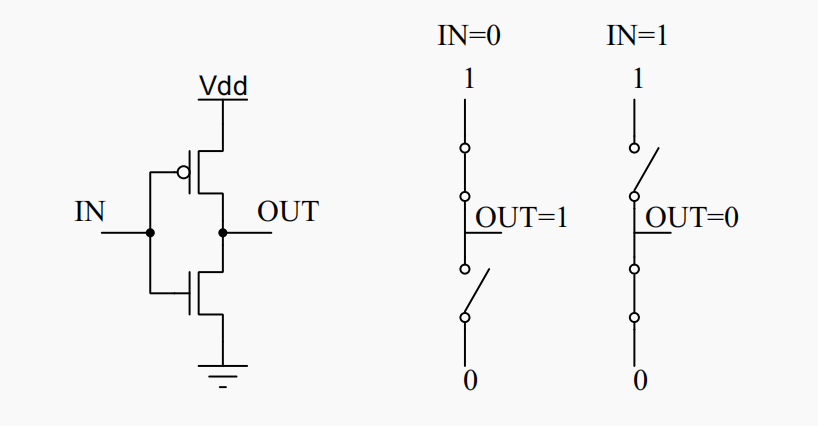

CMOS作为反相器

使用MOS晶体管建立的最简单的逻辑门是反相器。反相器由两个互补MOS晶体管组成,一个是nMOS,一个是pMOS,互补MOS(CMOS)反相器因此而得名。下图显示了使用一个nMOS晶体管和一个pMOS晶体管的CMOS反相器或"非"门的原理图和开关级模型。

输入IN连接两个晶体管的门。当输入IN为0时,nMOS晶体管为OFF,而pMOS晶体管为ON。因此,输出OUT被拉到逻辑1,因为它通过pMOS晶体管连接到Vdd。相反,当IN为1时,nMOS为ON,PMOS为OFF,而OUT则被拉低到“0”,因为它通过nMOS晶体管与GND相连。

到这里,我们的数字电路可以完成一些最基本的逻辑功能,但是还不能够存储信息。

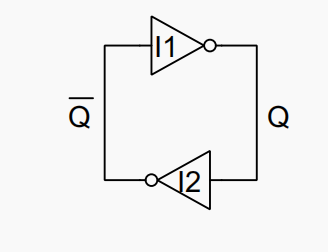

双稳态元件

现在我们已经熟悉了MOS晶体管和CMOS反相器,是时候学习如何在MOS数字电路中存储1bit信息了,即如何使用MOS晶体管和反相器形成一个1位存储单元。存储器的基本组件是双稳态元件,即具有两个稳定状态的逻辑元件。下图显示了由两个反相器I1和I2组成的双稳态元件。反相器是交叉耦合的,这意味着11的输入是I2的输出,反之亦然。

如果Q=0,12接收到一个False输入,在输出上产生一个TRUE输出。11接收到一个TRUE输入,在输出上产生一个False输出。这与最开始的输入Q=0是一致的,所以电路处于稳态。

如果Q=1,12接收一个TRUE输入,在输出上产生一个FALSE输出。11接收一个FALSE输入,在输出上产生一个TRUE输出。与最初的输入Q=1是一致的,所以同样电路处于稳态。

因为交叉耦合反相器有两个稳定状态,0和1,所以电路被称为双稳态。交叉耦合反相器的状态包含在一个二进制状态变量Q中。具体来说,如果Q=0,它将永远保持0,如果Q=1,它将永远维持1。

虽然交叉耦合反相器可以存储一点信息,但它们不实用,因为用户没有输入来控制状态。因此,我们必须用电路来扩展双稳态元件,它提供输入以控制状态变量的值。一个这样的元件,可以接受输入来控制存储在双稳态的值是一个静态RAM单元。

后续我们再介绍SRAM和DRAM。

到这里,虽然不够实用,但是我们已经可以使用MOS晶体管设计组合逻辑和时序逻辑了,这是芯片科技的关键一步。

-

CMOS

+关注

关注

58文章

5675浏览量

235104 -

反相器

+关注

关注

6文章

310浏览量

43240 -

晶体管

+关注

关注

77文章

9629浏览量

137808 -

数字电路

+关注

关注

193文章

1600浏览量

80489

原文标题:数字电路的基础——CMOS

文章出处:【微信号:数字芯片实验室,微信公众号:数字芯片实验室】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

【下载】《晶体管电路设计》——晶体管电路基础知识汇总

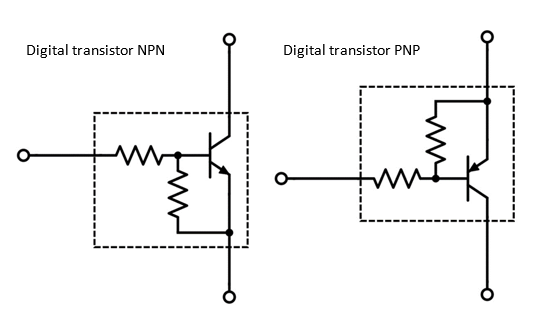

数字晶体管的原理

数字晶体管的原理

增强型MOS晶体管,增强型MOS晶体管是什么意思

MOS晶体管结构与CMOS单元电路与版图阐述

MOS管和晶体管的概念

浅析MOS 晶体管的核心概念

数字电路的基础概念:MOS晶体管

数字电路的基础概念:MOS晶体管

评论