前段时间公众号上发的“叼图系列”,有同学在问“还有后续吗?”,当然有,只不过我比较磨叽。毕竟发原创比较费时间,大部分时间还是要搬砖。现在子弹飞的时间差不多了,我们来一起来看下问题。

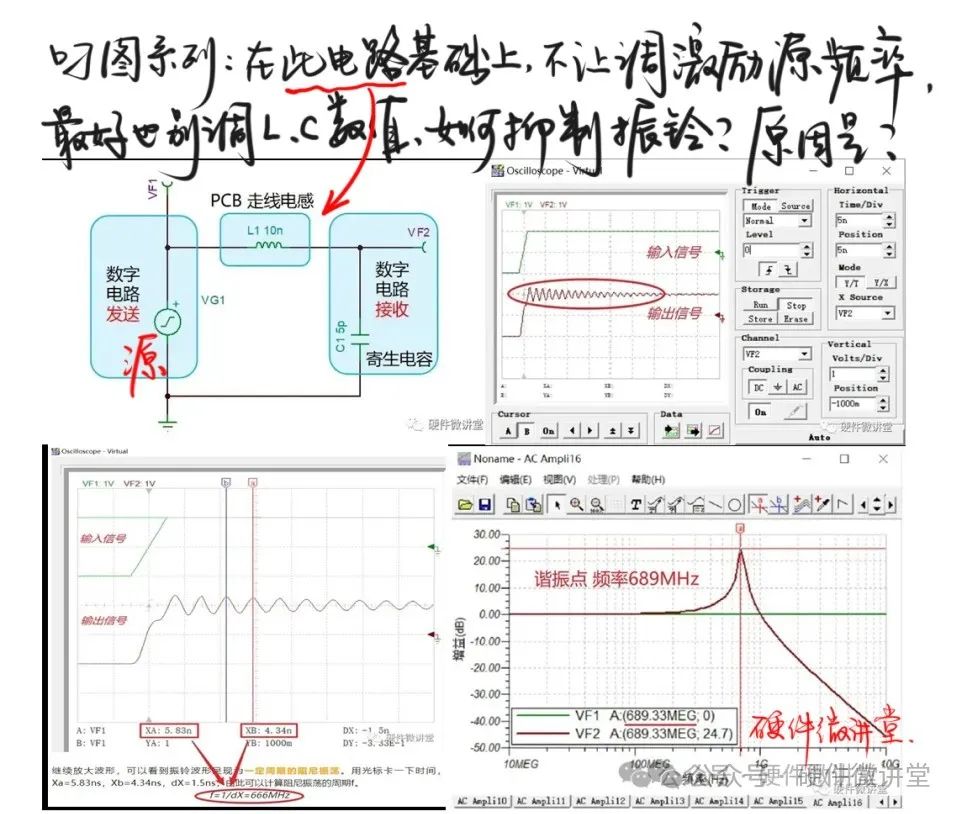

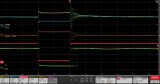

如下图所示,细心的同学也可以多研究下评论区的留言。留言质量很高的,都不用我讲太多,问题基本就解决了。

一道问题

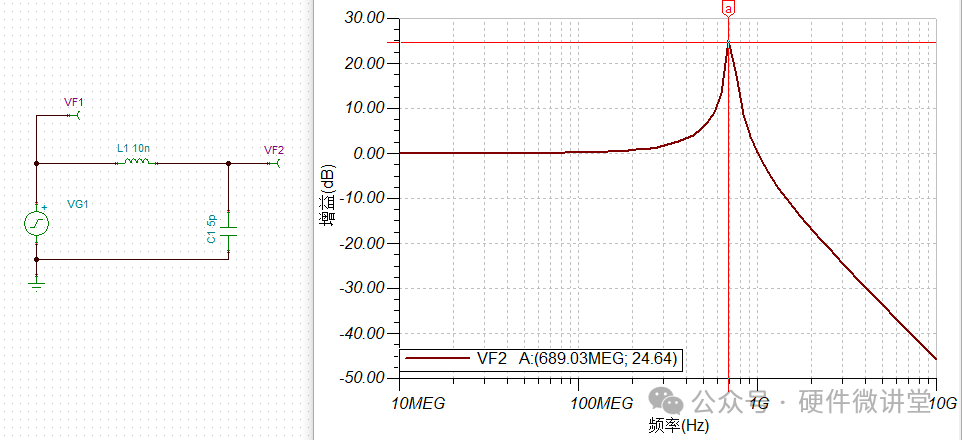

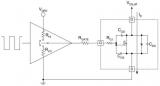

文章开头图片中,激励源VG1是2MHz的方波,经过L1和C1,输出端VF2的边沿有明显的振铃。问在此电路基础上,不调激励源频率,不调L和C数值,如何抑制振铃?

这个问题,在现实的问题调试中很常见。我们经常遇到PCB已经做好,板子也贴好,上电测试发现某驱动信号波形很差劲,有明显振铃。怎么办?

①调整电路参数;-->要改BOM,已贴好的板子都要返工改制;

②增加抑制振铃电路;-->要改PCB,重新打板,浪费时间和钱;

③降频;-->降低激励源频率是常见的SI调试手段,但现实条件未必允许。频率通常是在设计阶段提前规划好,牵一发则动全身。

这些都不行,怎么办呢?今天我们就来一起探讨一下……

激励源的频谱

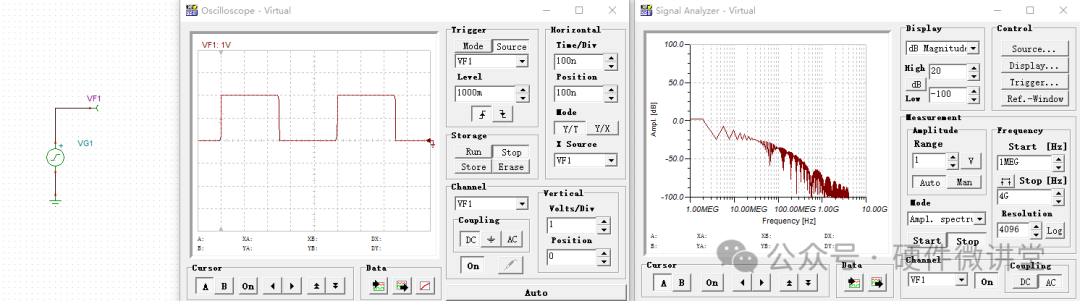

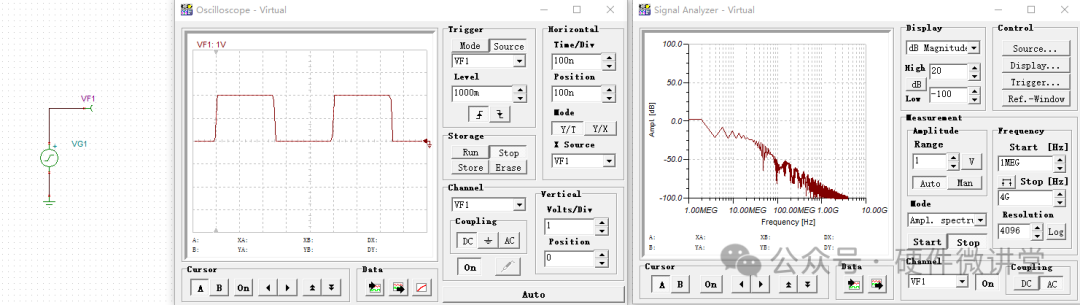

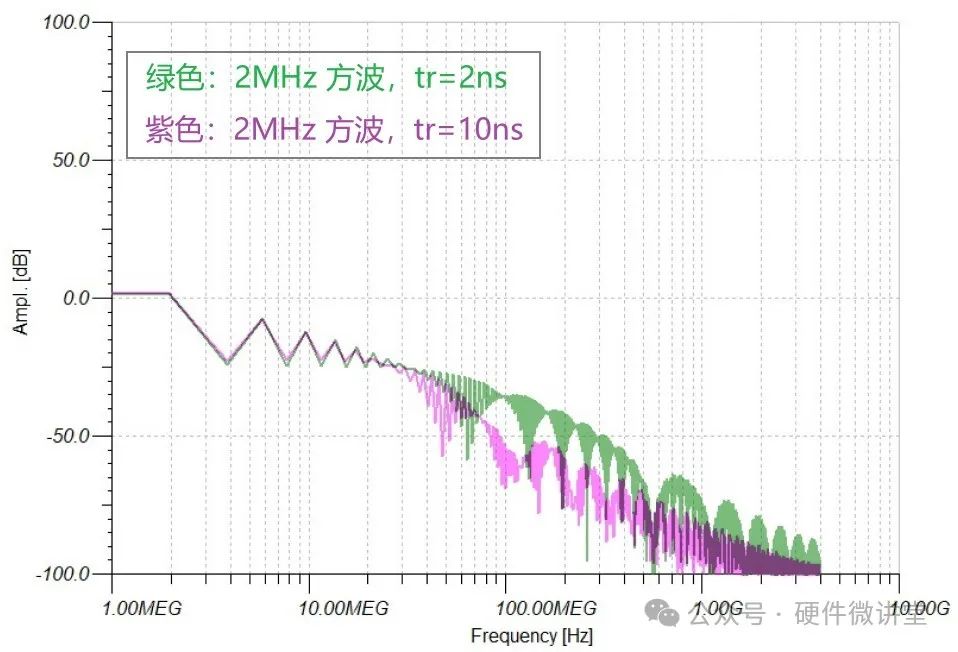

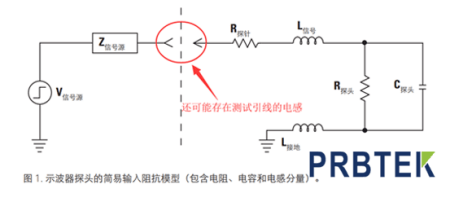

前面仿真我们用的激励源是2MHz的方波,上升沿为2ns。我们依然使用TINA-TI进行仿真,选用“示波器”来看激励源的时域信号,选用“信号分析仪”来看信号的频谱。仿真结果如下图所示:

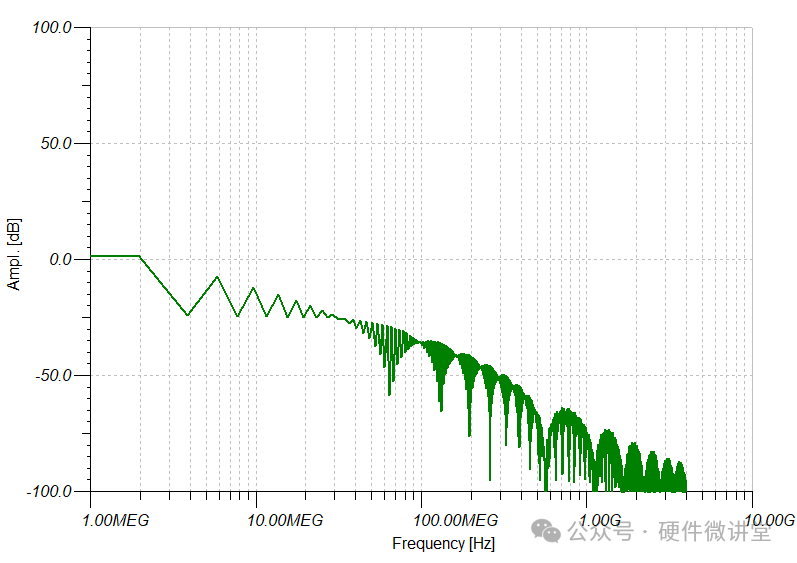

我们再把频谱的图片单独拉出来看下。

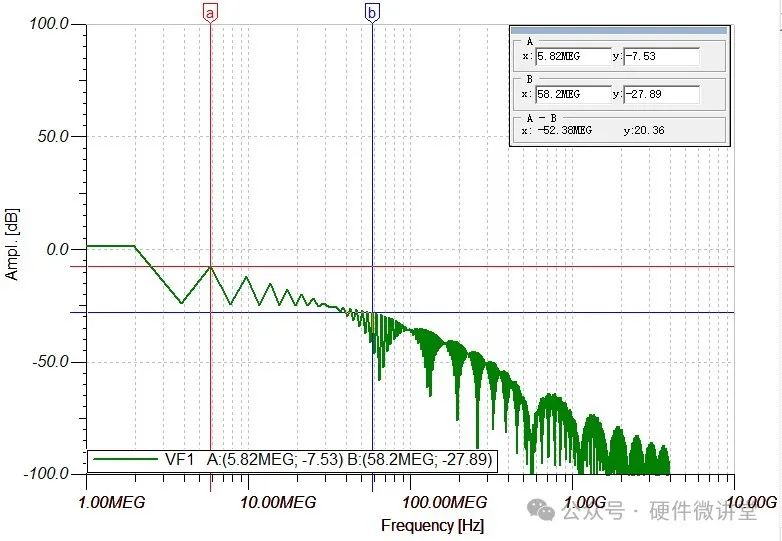

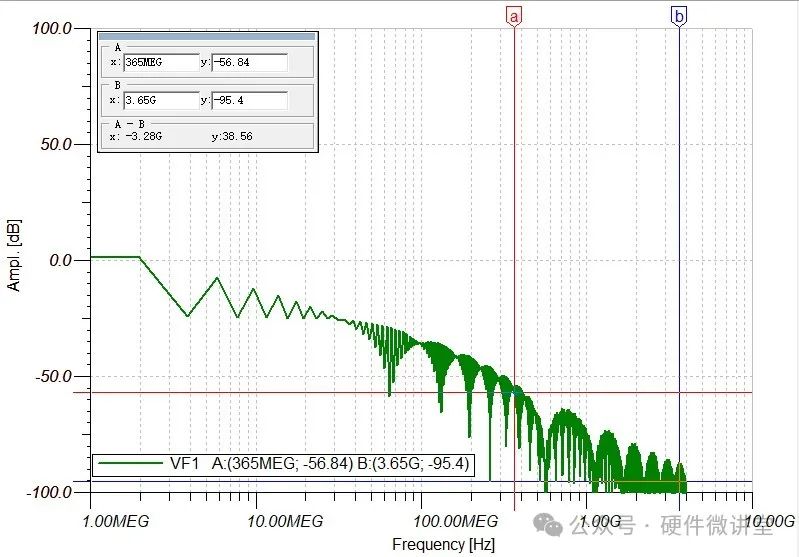

可能单看这个图,可能看不出来什么,不妨我们标记2组数据。

第一组:光标a处是5.82MHz,对应的幅值为-7.53dB;光标b处是58.2MHz,对应的幅值为-27.89dB,两者相差约20dB。

第二组:光标a处是365MHz,对应的幅值为-56.84dB;光标b处是3.65GHz,对应的幅值为-95.4dB,两者相差约40dB。

说到这里,有点同学可能想起来一些内容。对了,就是梯形波频谱的包络渐近线。现实中的方波,都不会是理想的方波,会存在一定上升沿和下降沿,即便是ns级,ps级,依然可以看做是梯形波。所以,理解梯形波频谱的包络渐近线,具有广泛的指导意义。

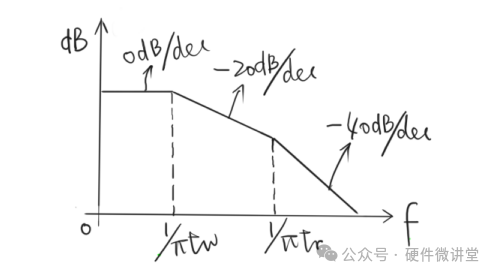

梯形波的频谱包络渐近线

梯形波的频谱包络由3条渐近线和2个分界点围城:

①渐近线0dB/10dec:在0~f1范围内;

②渐近线-20dB/10dec:在f1~f2范围内;

③渐近线-40dB/10dec:在大于f2的范围内;

④分界点f1:1/πtw;

⑤分界点f2:1/πtr;

tw为梯形波的脉冲宽度,tr为梯形波的脉冲上升沿时间。

在我们了解梯形波包络渐近线后,我们可以通过调整tw和tr来调整梯形波的频谱包络。

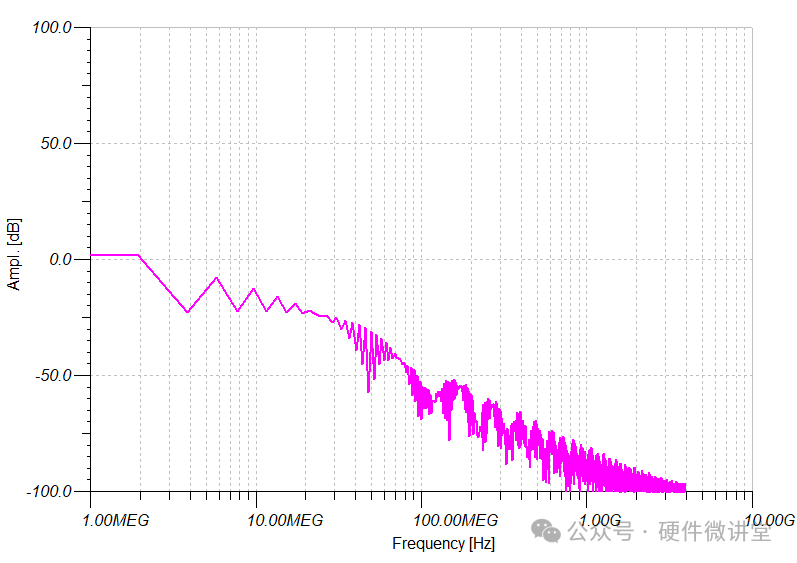

在不改变激励源频率的前提下,我们尝试把上升沿从2ns调整为10ns,再看下

对比tr=2ns和tr=10ns的频谱包络,可以粗略看出在高频段幅值有明显跌幅。此时我们可以重点关注下分界点f2(1/πtr),定量来分析。

tr=2ns时,可以粗略计算出f2=159MHz。即:当频率大于159MHz时,频率分量的幅值才以-40dB/dec的速率减小。

tr=10ns时,可以粗略计算出f2=31.8MHz。即:当频率大于31.8MHz时,频率分量的幅值就开始以-40dB/dec的速率减小。

从上图中,确实可以看出这样的趋势。当上升沿从2ns增大到10ns后,频谱以-40dB/dec速率下降的频点明显提前(从159MHz提前到31.8MHz)。

再结合电路分析

前面我们花了大量的篇幅来分析激励源的频谱,并对包络渐近线进行了定量解析,这只是对电路激励源的分析。我们再结合电路来看。

LC电路的频率增益曲线,如上图所示,相信各位同学并不陌生。谐振点的位置在689MHz附近。这个谐振频率属于电路的硬件特性,不会随着激励源的频率、上升沿变化而变化。不论激励源tr是2ns还是10ns,LC电路的谐振频率和Q值是不变的。

结合上一小节的结论,我们可以知晓:tr从2ns增大到10ns,频谱开始以-40dB/dec速率衰减的频点从159MHz提前到31.8MHz。当频率上升到689MHz附近时,相较于tr=2ns,tr=10ns的激励源频谱衰减的更多,幅值更低。基于LC谐振的选频特性,被选频放大后的幅值也会比tr=2ns的要小。

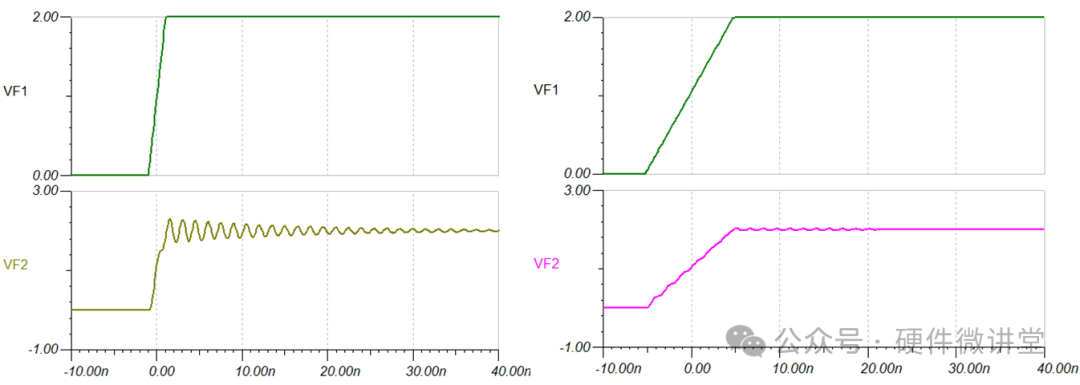

如上图所示,左侧为tr=2ns的VF1和VF2,右侧为tr=10ns的VF1和VF2。可以看出tr变缓后,输出端的振铃得到了明显的削弱。

强调:这里的振铃只是削弱/抑制,并不是消除。因为上面提到所有动作并没有从根本上改变振荡系统的工作状态,系统依旧处于欠阻尼状态。只是使得进入振荡系统的激励源能量减弱而已。

总 结

先聊到这里,梳理下今天讨论的内容:

①讲述一种实际问题:不能改PCB,不能改电路参数,不能改频率,又需要抑制振铃,如何破局?

②以实际仿真波形来解析梯形波频谱包络及其渐近线;

③以实际仿真波形对比来解析不同tr对应的梯形波频谱包络区别;

④结合电路及仿真来对比不同tr的振铃抑制情况;

⑤最后“强调”的那一段文字,说出了问题本质,尤其重要。

-

pcb

+关注

关注

4326文章

23159浏览量

399497 -

激励源

+关注

关注

0文章

5浏览量

8944 -

振铃

+关注

关注

0文章

27浏览量

17831

原文标题:不降频,不改PCB,不调电路参数,如何抑制振铃呢?

文章出处:【微信号:hjldws,微信公众号:硬件微讲堂】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

技术分享:如何设计可调光LED灯

升压转换器开关节点的振铃最小化-PMP-便携式电源应用

元件设计时注意事项

芯片引脚串联电阻的目的

利用RC来消除反激开关电源次级二极管的振铃

无需缓冲器的反激式转换器技术

图像处理振铃效应原理_图像处理中振铃现象

反激电源中如何抑制振铃

SIT1043Q CAN FD收发器振铃抑制功能实现原理及实际应用

纳芯微推出基于创新型振铃抑制专利的车规级CAN SIC—NCA1462-Q1

芯力特发布带振铃抑制功能的CAN收发器——SIT1463Q

如何抑制振铃

如何抑制振铃

评论