1. 引言

随着嵌入式技术飞速发展,高速电路的开发面临器件尺寸缩小、时钟频率提升、布线密度增加等因素,嵌入式产品在信号传输、电源质量等问题上要求日益提高。为确保高速电路在产品整个生命周期内的可靠性,必须采用先进的可靠性技术。

武汉万象奥科学习易瑞来殷老师可靠性相关课程与经验,以更好的应对这些挑战。

2. 高速电路开发的挑战

由于产品和器件的尺寸不断缩小,器件的时钟频率越来越高,信号边缘速率也越来越快,导致高速电路问题日益突出。现在IC的集成规模越来越大,管脚数量越来越多,单板上布线的密度不断加大,IC的电源电压逐渐降低、电流逐渐加大,功耗越来越大。

以上几个方面就是现代高速电路开发的最新挑战,对设计者的可靠性设计水平提出了更高的要求。

高速电路中的器件参数不一致,或发生飘移,使得整个电路的性能逐步降低,直至功能完全丧失。也可能产生过电应力或降额不足,使器件失效。SI问题的隐蔽性较大,往往在出厂前无法测试或通过老化筛选出问题,带来可靠性隐患。

可靠性设计主要就是解决产品在整个生命周期内出现的品质问题,既可以解决产品性能退化的问题,也可以解决器件失效的问题。可靠性技术在高速电路中的应用主要有最坏情况数字电路时序容差分析、串扰分析和电源完整性技术等。

3. 高速电路可靠性问题

高速电路引起的可靠性问题主要有以下5个方面:

信号传输延时逐步加大,造成时序失效。

信号波形失真逐步加大,造成信号读取错误。

信号之间的串扰逐步加大,产生误码或程序运行错误。

电源质量和地弹逐步变坏,影响器件的正常工作。

EMC指标逐渐超过要求。

4. 高速电路设计的可靠性技术

解决上述5个方面的问题,个人认为可以采用以下3种可靠性技术来解决:

1) 运用最坏情况分析(WCCA)方法,进行数字电路时序分析,使传输线延时、波形失真等在整个生命周期内不超过要求,保证高速数字电路的正常逻辑连接。

以前的电路板运行速度较低,因此很少有时序问题,现在的器件速度越来越快,时钟周期为纳秒级,传输走线延时的影响十分突出,已影响到器件能否正常工作,必须分析最坏情况下的时序参数。

数字电路时序容差分析主要是分析数字电路间的时序关系,即分析时序余量是否满足要求。

为了分析该电路的时序容差情况,主要考虑三个方面的因素:器件本身的时序参数容差、PCB布线产生的时序容差、其他干扰产生的时序容差。

器件本身的时序参数容差分析主要是检查输出器件端口的时序参数是否满足输入器件端口的时序参数要求。并且对器件的时序参数按最坏情况考虑,不是按一般的典型值进行分析。

PCB布线产生的时序容差分析主要是分析器件端口模型、传输线拓扑、终端匹配、负载数量等在最坏情况下,采用信号完整性(SI)仿真工具,分析传输信号延时和波形,得出对时序的影响。

其他干扰产生的时序容差分析主要是分析电源输入、电源平面谐振特性、同步开关噪声、串扰等对信号时序的影响。

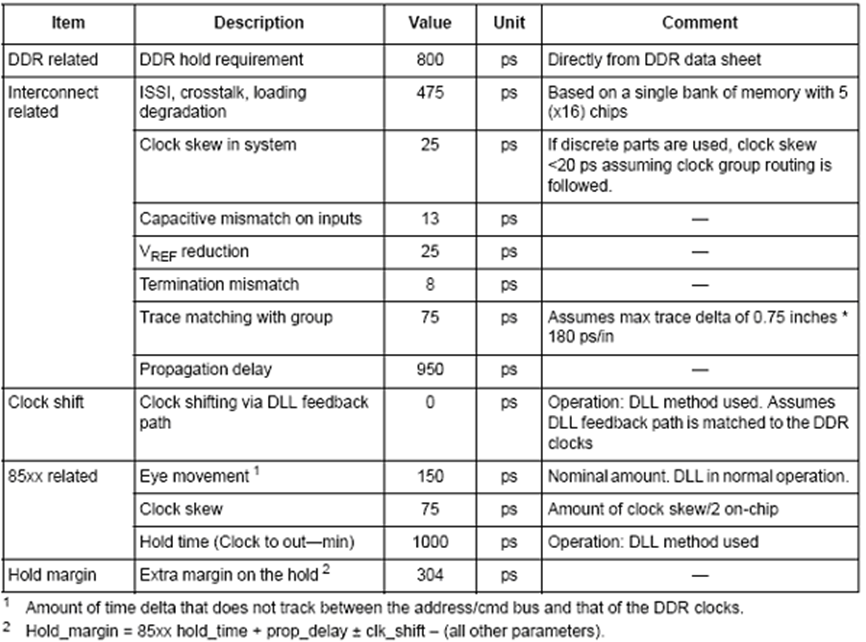

时序参数中最关键的是建立时间和保持时间两个参数。如下图,是某DDR存储器的地址、控制、命令信号的保持时间要求,对其中的每个参数都要分析得到它们的最坏情况值,然后代入公式中得到容差值,如果大于0,表示容差满足要求,如果小于0,表示容差设计不足,需要重新设计。

2) 运用仿真和实验相结合的方法,准确分析出串扰源和耦合途径。

串扰是PCB设计时必须关注的可靠性问题。由于被干扰信号上产生的脉冲或毛刺等多是半高电平,在CMOS信号的阈值附近,这样造成的串扰问题有很大的随机性,很多不能在出厂前测试出来,在市场上也是时有时无,返修产品有时候很难重复失效现象,分析起来非常困难,这些都是典型的可靠性问题。

串扰分析的方法推荐使用仿真和实验相结合的方法,既减少实验次数,又分析得比较全面。比如在分析一个串扰问题时,有些工程师认为是感性串扰,有些认为是容性串扰,有些认为是地弹噪声。

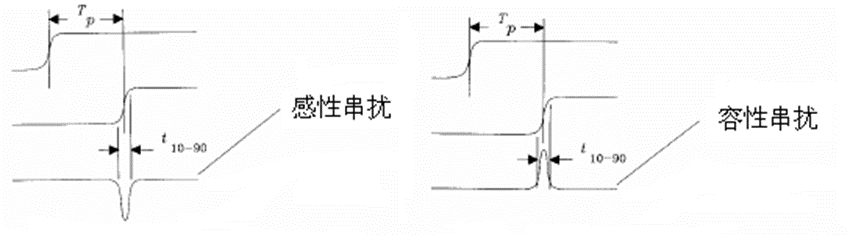

我们知道,感性串扰和容性串扰的相同点是:串扰在远端为短脉冲,近端为长信号。不同之处是:前向感性串扰和前向容性串扰的极性相反(如下图),感性串扰产生的是噪声电压信号,是串接在被干扰导线上的,而容性串扰产生的是噪声电流信号,是并接在被干扰导线和地之间的,也就是说,感性串扰随负载增大而减小,容性串扰随负载增大而增大。可利用这两点来辨别容性串扰和感性串扰。如果完全用实验的方法,那么要用很多的单板来进行割线、飞线、焊接器件等,做多次实验,但是用仿真的方法就方便经济得多了,而且几乎可以想怎么做就怎么做。

在PCB电路仿真中,把被串扰线负载电阻减小10倍时,串扰马上显著减小。可见降低对地阻抗可减小串扰大小,这是容性串扰的特征。

另外我们去掉在串扰源和被串扰信号线中间的一块灌铜地平面,提取出电路的仿真模型,在HSPICE中再次仿真,发现串扰显著增加。这也是容性串扰的一个证明。注意,这种方法是不能通过实际测试验证的,只能通过仿真来分析。

同时通过实际测试发现,串扰源的正跳变在被干扰信号线上对应为正的串扰信号,负跳变在被干扰信号线上对应为负的串扰信号。

综上所述,根据上述串扰形式判别方法,再通过上面几点的仿真和实测结果,能肯定该串扰为容性串扰占主导。最后针对容性串扰的特点,减小负载电阻,降低了串扰,电路恢复正常。

3) 运用电源完整性(PI)方法,分析电源输出滤波电路和电源平面设计,保证整个生命周期内的电源都符合要求。

随着信号频率的增高和高速系统单板布线越来越密集,无噪声的电源分配成为了PCB设计的一个主要挑战。当高速集成电路I/O端口同时改变状态时,通过电源分配系统(PDS)的纹波噪声随频率的变化而变化,这个噪声既影响高速设备系统中的IC工作,同时干扰周围的环境。

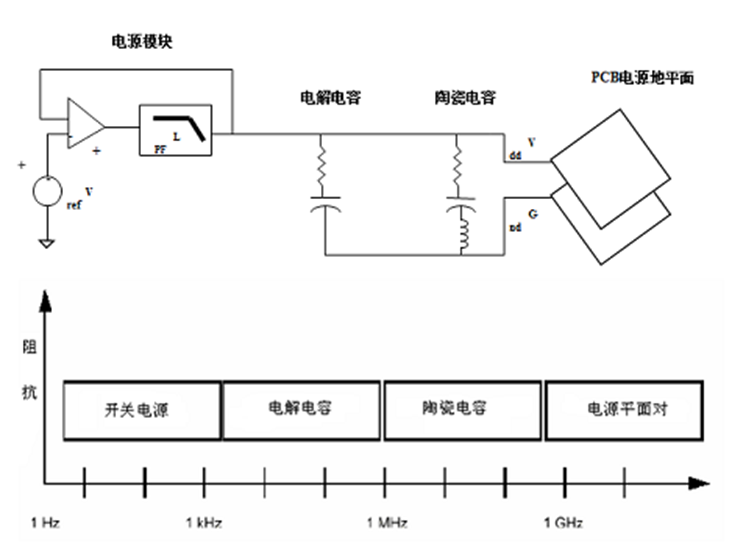

为了确保良好的电源分配,电源分配阻抗必须在一个很宽的频率范围内控制在一个要求的目标阻抗下。这可以通过在目标频率范围内仔细的考虑开关电源,大电容,陶瓷电容以及电源/地平面对等等来实现。陶瓷电容一般作去耦用,在逻辑开关时给需要大电流的驱动器件提供本地补偿。

上图显示了在控制电源分配系统(PDS)目标阻抗时各个频率范围内哪种器件是最有效的。

可以看出电源完整性工作主要有:确定目标阻抗和选择合适的PDS组成部分。

确定目标阻抗主要是根据SSN(SimultaneousSwitchingNoise同步开关噪声)来计算动态电流,然后根据电源变化的要求(一般为3-5%),计算出目标阻抗。这个时候也必须根据可靠性设计规律,考虑最坏情况下的动态电流,所以我们一般是假定所有I/O口同时切换,而且每个端口的输出电流都取最大值。而电源变化的要求则需要取最小值。

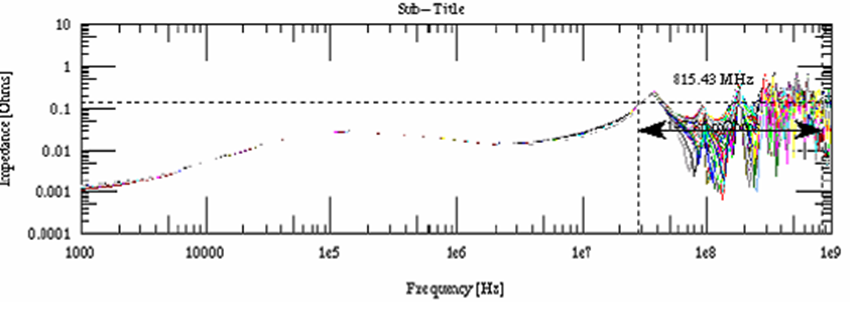

对于PDS的各个部分,特别是电解电容和陶瓷电容,必须考虑器件的容差,因为电容的来料精度一般比较差,20%精度的电容最常使用。同时电容容值受温度、湿度、气压以及寿命的影响也很显著。我们分析过,考虑上述因素后,电容的容值最大可以变化1倍以上。而且电容内部的分布参数(如ESR、ESL)都有很大容差。所以在PI分析中对电容参数也要选择多个参数分别分析,得出最坏情况下的PDS阻抗曲线。如下图所示。

可以看出,用可靠性技术来分析电源完整性,不仅要分析典型值下的PDS系统阻抗特性,同时要根据器件在最坏情况下的参数容差,分析PDS的极限阻抗特性,达到在整个生命周期内,电源对产品都不会引起可靠性问题。

-

嵌入式

+关注

关注

5090文章

19176浏览量

306884 -

高速电路

+关注

关注

8文章

159浏览量

24258 -

电路开发

+关注

关注

0文章

3浏览量

3636

发布评论请先 登录

相关推荐

高速电路开发中有哪些挑战?

高速电路开发中有哪些挑战?

评论