今天我们要分享的这个案例是关于eMMC启动不正常的问题,感谢热心网友“晒不”提供的案例素材,也谢谢他的分享。

上篇文章我们提到希望大家一起来分享硬件调试中发现的一些低级错误,果然就有我们的铁杆粉丝之一“晒不”发来了他初步整理的案例素材,大家一起来学习一下吧,也谢谢他的分享!

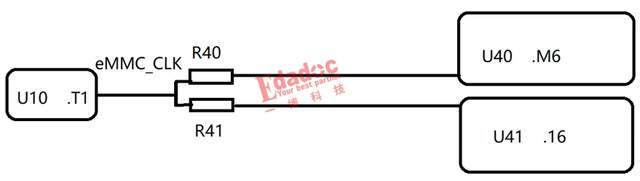

这个项目的主芯片是瑞芯微的RV1126(位号U10),分别拖了一个金士顿的eMMC芯片(位号U40)和镁光的NAND Flash芯片(位号U41),在Layout的时候做了兼容设计,也就是通过选焊电阻的方式,让主芯片来选通其中一个芯片,使用的时候二选一,eMMC和NAND Flash芯片不会一起工作,大致的拓扑图如下所示。

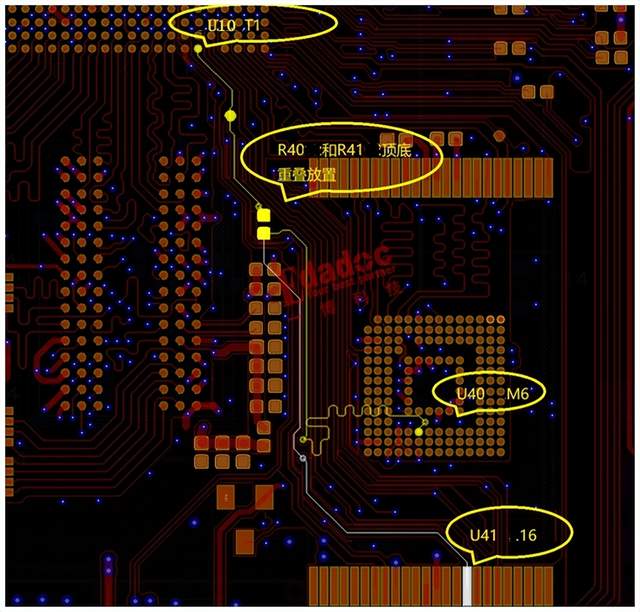

从Layout设计文件可以看到,几个芯片都是放在Top面,eMMC和NAND Flash基本是放在同一个中心位置,所以贴片的时候只能选择贴其中的一个,两个芯片是没法同时贴上的,所以需要做兼容设计。两个分支电阻在垂直空间上重叠放置在Top面和Bottom面,这样如果只焊接其中一个电阻的时候,确实是可以做选通操作,看起来Layout设计没什么问题,对应的走线如下图所示。

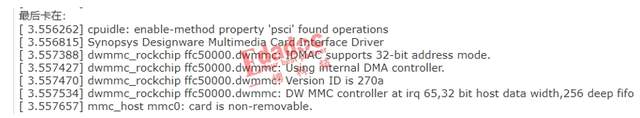

设计上没发现什么问题,然后就制板贴片开始调试。硬件在调试板子时发现,有时候上电,系统会有卡死的情况,同样的固件在开发板上是OK的,软件做了几轮修改都会有类似软件报错的情况,显示出跑到eMMC操作时就卡住了,最后只能怀疑是硬件或者PCB Layout的问题。

但硬件有排除不是自己问题的理由:“最小系统模块(包含eMMC)的原理是直接复制开发板的,所有的器件贴装也和开发板一样,同样的代码在之前开发板上没有问题,而现在新设计的板子有问题,那肯定是PCB Layout出了问题”。

不可否认,硬件的话确实有一定的道理,硬件原理之前是验证过的,这样压力一下子就给到了PCB设计工程师。无奈,PCB工程师只能想办法自证清白,在没有专职SI工程师的情况下,PCB设计工程师只能通过再次查板,进行粗略的估算和评估一些影响,检查的方向如下:

1、阻抗不匹配方向:所有信号走线没有跨分割平面,走线线宽和阻抗计算也没有错误,同时也不存在较长的走线Stub,所以这一条不会影响。

2、时序方向:因为需要跑200MHz的信号,等长也是比较关键的,但因为没有做仿真,只能按照芯片的手册要求来做好等长约束,检查了等长表,每根信号走线长度也是都可以满足芯片要求,所以时序这块的影响也是可以初步排除。

3、电源方向:按照经验简单算了电源平面载流能力是可以满足需求的,相应的电源Pin脚也有足够的滤波电容,硬件测试电压和电源噪声都是可以满足要求,所以电源的影响也可以排除。

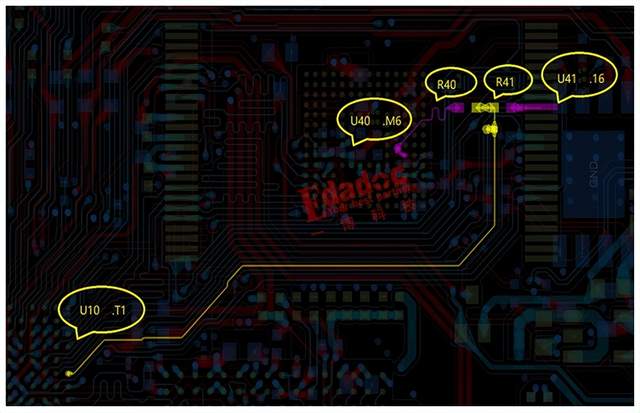

同时也和开发版本的设计进行了对比,硬件人员觉得是因为时钟信号走线和开发板不一致导致的。如下图是开发板的走线情况。

开发板上eMMC和NAND Flash也是同面同中心放置,原理是一样的,也是通过两个电阻做了选通,只是走线上的分支更短,而新改板后的分支相对来说长了很多。所以硬件人员有理由觉得是PCB改版带来的问题,所有的原理和贴片器件都是一样,PCB设计改了就出问题了,这个大概率是PCB设计不一样而带来的问题。

而PCB设计工程师也有自己的主张:“CLK信号是由RV1126源端发出的,开发板的串联阻抗匹配电阻放在了终端,靠近eMMC和NAND Flash是不对的,应该把串联匹配电阻靠近源端,所以本次改版设计的电阻就往源端放了,这样确实会导致分支变长,但由于是选焊的,如果一次只焊接其中一路的情况下,另一路是没有导通的,这样相当于没有分支的影响,原理上来说信号质量会更好。如果连串联匹配电阻放在源端也被怀疑有问题的话,那就是怀疑信号完整性的理论有问题了。”PCB设计工程师的话也是说得在理,无可挑剔,由于没有SI人员支持,于是双方各执一词,谁也说服不了谁。

经过几天的“沟通”,压力还是在PCB工程师这。就在PCB工程师拿着PCBA研究的时候,无意中发现虽然U41没有焊接,但是R41却焊接了器件。这个发现仿佛一道佛光,拯救了“背锅侠”。在PCB工程师的反馈下,硬件拆除了R41,系统终于可以正常启动了。

这个时候硬件人员就有疑问了,为什么开发板上的R41没有拆除可以正常工作,改版后的R41焊上就有问题了呢?大家可以帮忙回答一下哈!

同时也欢迎大家继续提供类似这种调试过程中的低级错误案例素材,谢谢!

审核编辑 黄宇

-

NAND

+关注

关注

16文章

1690浏览量

136412 -

Nand flash

+关注

关注

6文章

241浏览量

39965 -

emmc

+关注

关注

7文章

218浏览量

52887

发布评论请先 登录

相关推荐

伺服电机振动不正常原因和维修及案例分析

ADS1110 ESD不正常的原因?

LM4780桥接功放静态电流达到190mA,芯片非常烫,到底正不正常?

为什么AIC23刚上电时,工作不正常?

使用LM48511SQ功放升压电路工作不正常是哪里出了问题?

LTM4678输出不正常是哪里的问题?

LM358用tssop封装不正常工作的原因?

ADS1675采样不正常是哪些原因引起的?

LOG114 VLogout输出不正常的原因?

我的eMMC启动不正常,问题到底在哪里?

AD7616的VxGND全部接地时,读值不正常是怎么回事?

如何维修安捷伦N8946电源输出不正常

我的eMMC启动不正常,问题到底在哪里?

我的eMMC启动不正常,问题到底在哪里?

评论