一、引言

CMOS(互补金属氧化物半导体)门电路是现代数字电子系统中广泛使用的关键组件。它们以其低功耗、高噪声容限和易于集成等优点而著称。然而,在设计CMOS门电路时,经常会遇到多余的输入端问题。这些多余的输入端如果不妥善处理,可能会对电路的性能和稳定性产生不利影响。因此,了解并掌握CMOS门电路多余输入端的处理方法对于确保电路设计的成功至关重要。

二、CMOS门电路概述

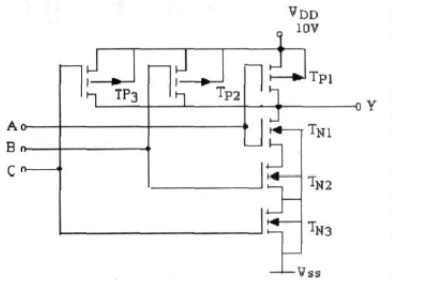

CMOS门电路由PMOS(P型金属氧化物半导体)和NMOS(N型金属氧化物半导体)晶体管组成,通过互补的方式实现逻辑功能。CMOS门电路的主要特点是静态功耗极低,因为当电路处于稳定状态时,PMOS和NMOS晶体管中只有一个处于导通状态,而另一个则处于截止状态,从而避免了电流的直接流通。

三、多余输入端的影响

在CMOS门电路中,多余的输入端如果不接任何信号或处理不当,可能会产生以下几种影响:

- 逻辑功能不确定 :多余的输入端如果处于浮空状态(即未接任何信号),其电平状态可能不稳定,导致电路的逻辑功能无法确定。

- 功耗增加 :在某些情况下,多余的输入端如果接入高电平或低电平信号,可能会增加电路的静态功耗。

- 噪声敏感性增加 :未处理的输入端可能更容易受到外部噪声的干扰,影响电路的稳定性和可靠性。

四、多余输入端的处理方法

针对CMOS门电路多余输入端的问题,可以采取以下几种处理方法:

1. 接地处理

将多余的输入端接地是一种常见的处理方法。这种方法适用于CMOS或非门、或非门等逻辑门电路,因为它们的逻辑功能在输入端接地时不会受到影响。接地处理可以有效地防止输入端浮空带来的不稳定性和噪声干扰。

实施步骤 :

- 使用导线将多余的输入端与地(GND)相连。

- 确保接地连接可靠,避免接触不良或开路现象。

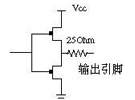

2. 接电源处理

对于CMOS与门、与非门等逻辑门电路,如果多余的输入端接入高电平信号对逻辑功能无影响,则可以将多余的输入端接电源(VCC)。这种方法可以确保输入端处于稳定的高电平状态,避免浮空带来的问题。

实施步骤 :

3. 并接使用

在某些情况下,可以将CMOS门电路多余的输入端与正在使用的输入端并接在一起使用。这种方法适用于输入端数量较多的情况,可以简化电路设计并减少元件数量。但需要注意的是,并接使用时要确保不会改变电路的逻辑功能。

实施步骤 :

- 使用导线将多余的输入端与正在使用的输入端相连。

- 验证并接后的电路逻辑功能是否符合设计要求。

4. 接入反相器

对于需要具有多种输入和输出的复杂电路,可以考虑将CMOS门电路多余的输入端接入一个反相器。通过反相器的作用,可以将多余的输入端反相输出,从而实现其他功能。这种方法需要额外的元件和布线,但可以增加电路的灵活性和功能性。

实施步骤 :

- 选择合适的反相器元件。

- 使用导线将多余的输入端与反相器的输入端相连。

- 将反相器的输出端连接到需要的位置。

5. 留空不接

在某些特殊情况下,如果CMOS门电路的多余输入端确实不需要使用,并且不会对电路的逻辑功能和稳定性产生影响,也可以选择留空不接。但需要注意的是,这种方法需要谨慎使用,因为留空的输入端可能会受到外部噪声的干扰。

实施步骤 :

- 确认多余的输入端确实不需要使用。

- 确保留空的输入端不会受到外部噪声的干扰。

五、注意事项

在处理CMOS门电路多余输入端时,需要注意以下几点:

- 了解电路特性 :在处理之前,需要充分了解CMOS门电路的特性,包括其逻辑功能、输入电压范围、功耗等。

- 避免干扰 :在连接和处理输入端时,要注意避免引入外部噪声和干扰信号。

- 选择适当的元件 :在选择限流电阻、反相器等元件时,要根据电路的实际需求进行选择,确保元件的规格和性能符合设计要求。

-

半导体

+关注

关注

334文章

27286浏览量

218050 -

数字电子

+关注

关注

6文章

104浏览量

21167 -

组件

+关注

关注

1文章

512浏览量

17813 -

CMOS门电路

+关注

关注

0文章

6浏览量

4901

发布评论请先 登录

相关推荐

cmos门电路多余输入端的处理方法

cmos门电路多余输入端的处理方法

评论